4.4 动态存储器(DRAM)

SRAM由于存在晶体管过多、功耗大、存储密度低等原因,静态存储器的规模往往较小。

一、DRAM简介

针对SRAM的改进构成了动态存储单元DRAM;

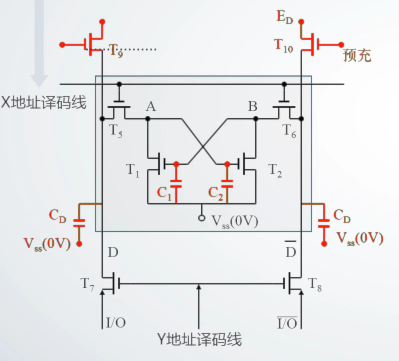

DRAM和SRAM相比,少了两个负载管(降低功耗和成本)且利用栅极分布电容存储电荷,同时增加电路协同存储单元工作;

DRAM靠内部寄生电容充放电来记忆信息,电容充有电荷为逻辑1,不充电为逻辑0。

DRAM的基本操作除了读、写、保持之外,还有一个刷新操作;

之所以要刷新是因为,DRAM是基于电容器上的电荷量存储信息的,而存储的信息电荷终究是有泄漏的,时间久了,信息就会丢失。因此,必须设法由外界按一定规律不断给栅极进行充电,补足栅极的信息电荷,这就是所谓“刷新”。

电路中各种操作的原理详见DRAM存储器原理

二、DRAM的刷新

刷新周期:两次刷新之间的时间间隔

由于MOS管栅极电容上存储的电荷会缓慢泄放,超过一定时间(2~3.3ms),就会丢失信息。因此必须定时给栅级电容补充电荷,进行刷新操作。

双译码结构的DRAM刷新按行进行(也就是可以一次刷新一整行),因次需要知道DRAM芯片存储矩阵的行数;

一般来说动态存储器的刷新有三种方式:

假设刷新周期为2毫秒,DRAM内部有128行,读写周期为0.5微秒;

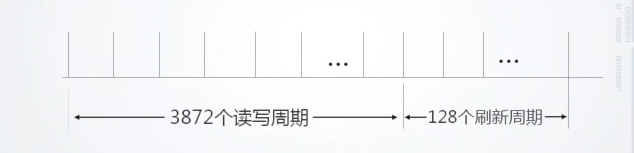

1. 集中式刷新

每一个刷新周期中集中一段时间对DRAM的所有航进行刷新;

两毫秒内有4000个读写周期,由于将刷新操作集中进行,4000个读写周期的前3872个读写周期用来读写,后128个周期用来行刷新;

在128个周期的刷新期间,CPU不能访问存储器,因此存在“死时间”;

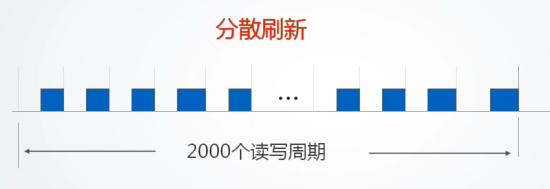

2. 分散式刷新

将刷新周期分配到读写周期中去。(每进行一次读写操作,随即刷新一次)

分散刷新情况下,存储器平均读写周期变慢(刷新的次数太多),存储器高速的特性没得到保留;

3. 异步刷新

由于要讲每一行刷新,将两毫秒平均分成128段, 每一段的时间进行一次刷新操作;

这种刷新方式保证了128行的遍历刷新,又保证了存储器高速特性;

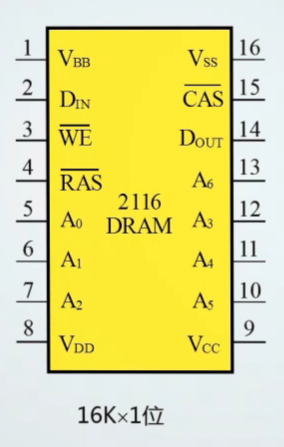

三、DRAM芯片的逻辑结构

芯片的逻辑结构如图示:

和SRAM芯片的逻辑结构相比,DRAM芯片的逻辑结构增加了RAS和DAS两个管脚,这分别代表了行选通和列选通信号。(SRAM是没有这两个信号的)

之所有要将这两个信号分开控制,是因为刷新的时候是按照行刷新的,刷新时不需要列选通;

同时DRAM的地址线是复用的,16k的地址本该有14根地址线,但图中只有7个地址线($A_0$ ~ $A_6$)。这是因为地址线做了复用,行列地址线是分开传送的;

Peter学长加油!!!!!

谢谢学弟❥