一丶计算机系统概述

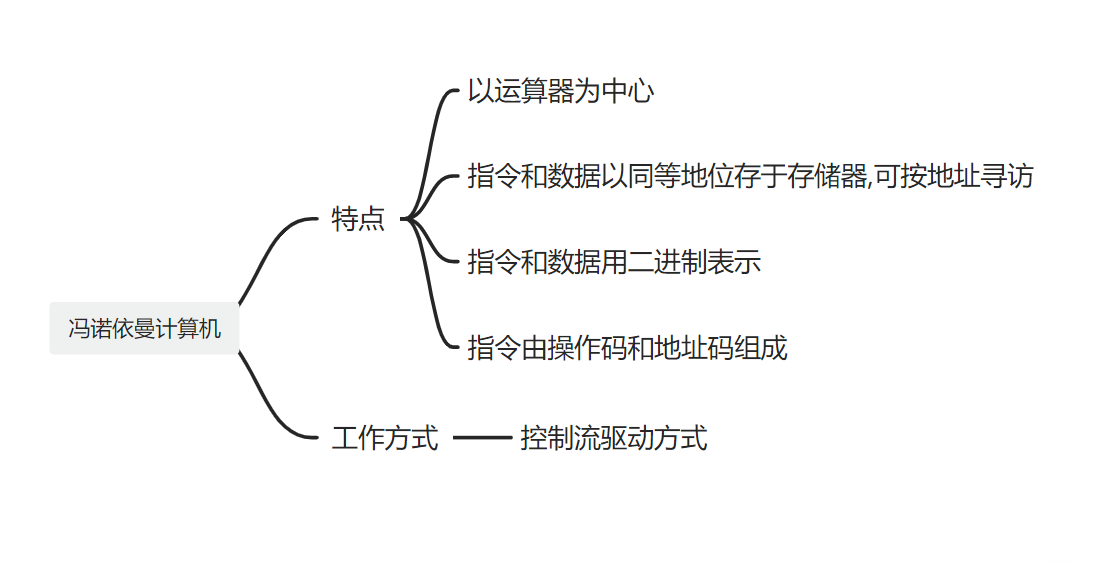

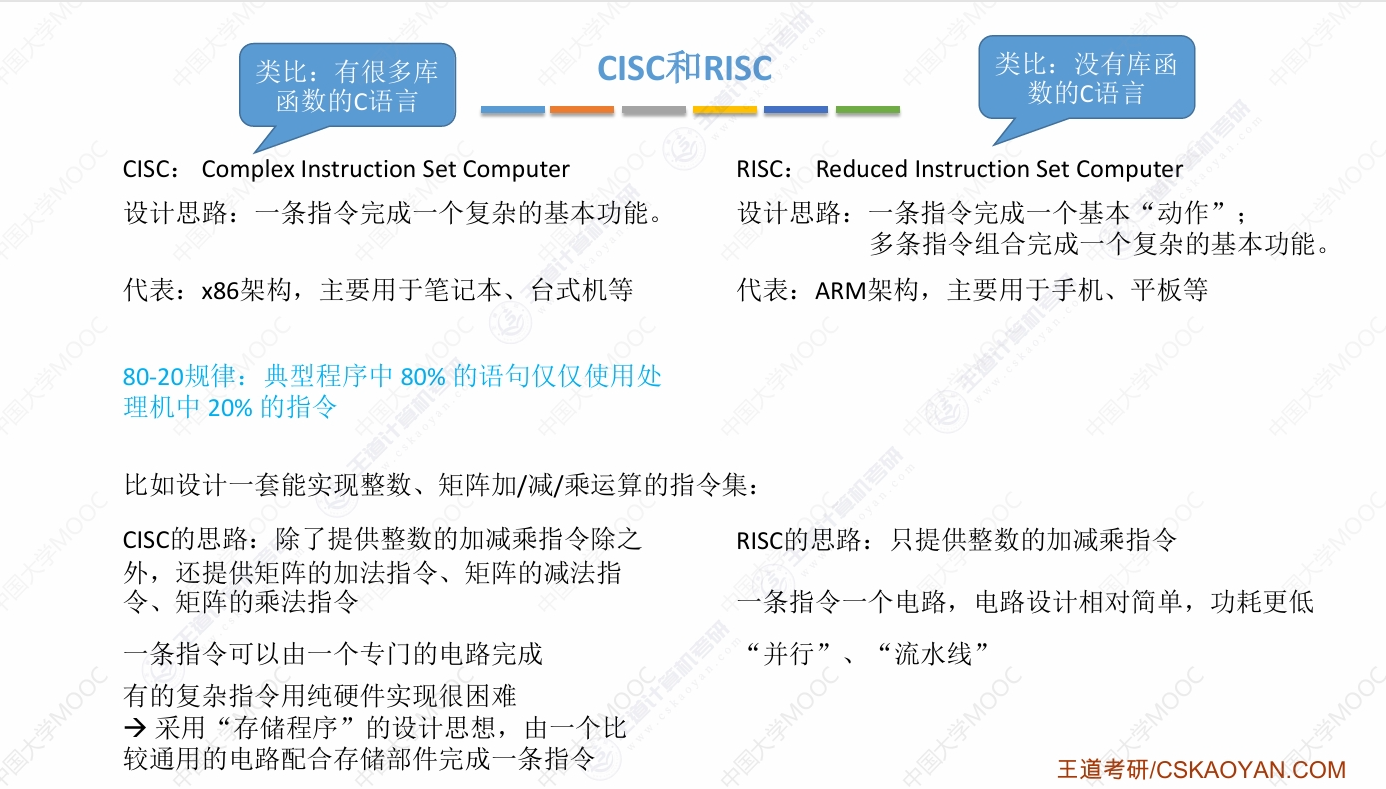

- “存储程序”思想 : 将事先编制好的程序和原始数据送入主存后才能执行

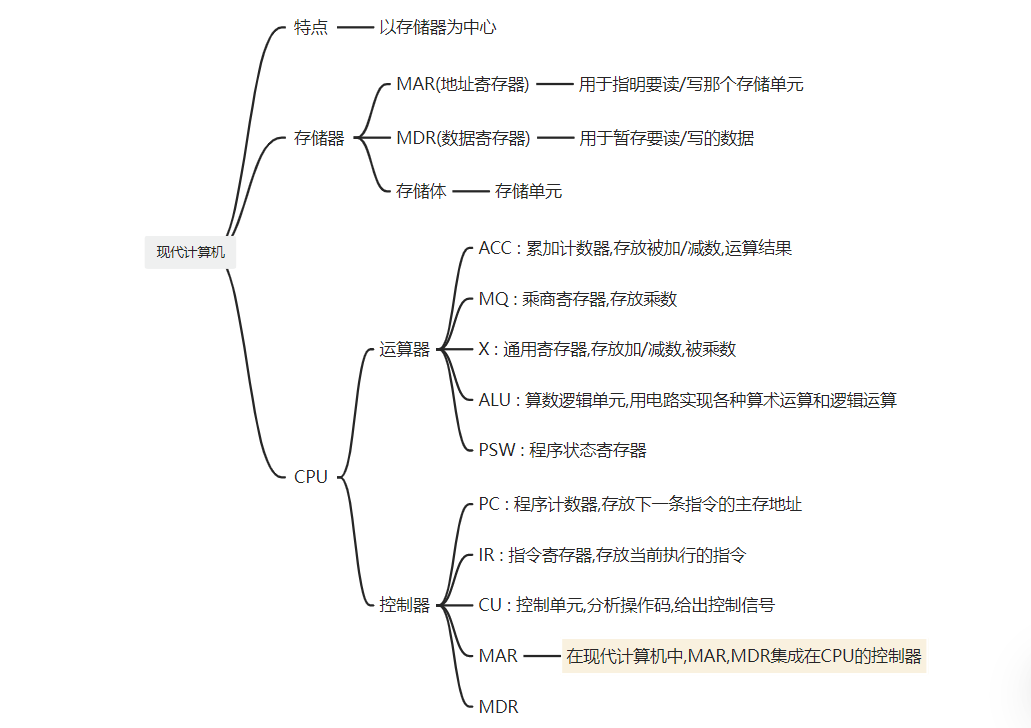

- CPU不包括地址译码器(其在主存中)

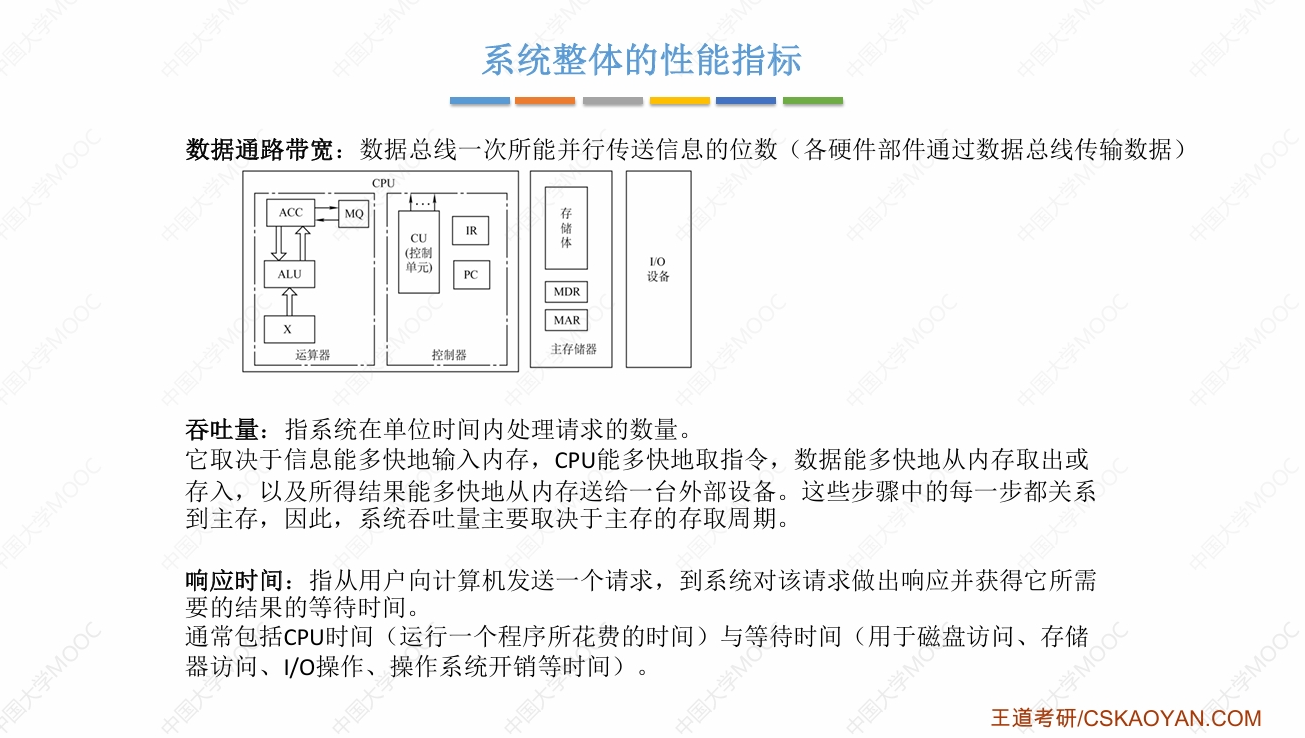

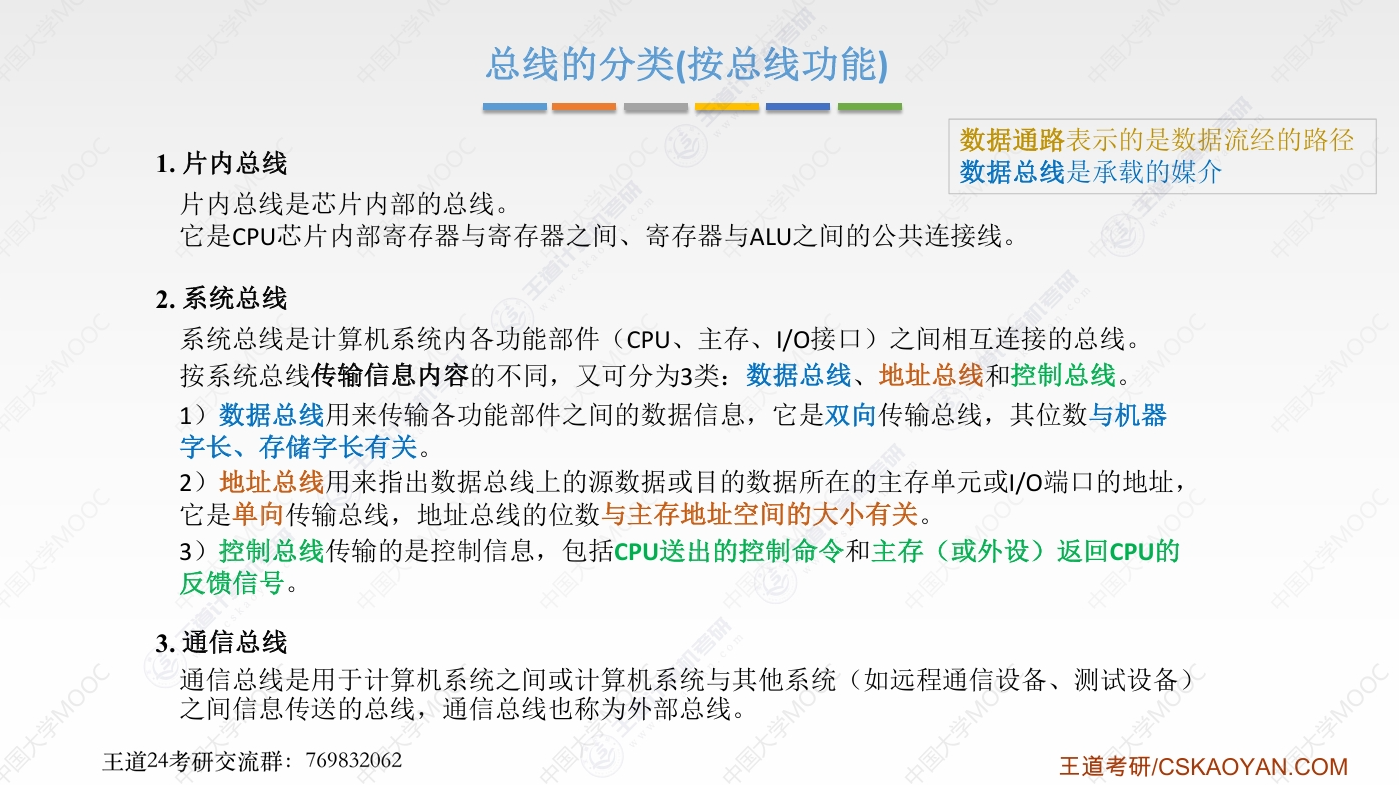

- 数据字长 : 数据总线一次能并行传送信息的位数

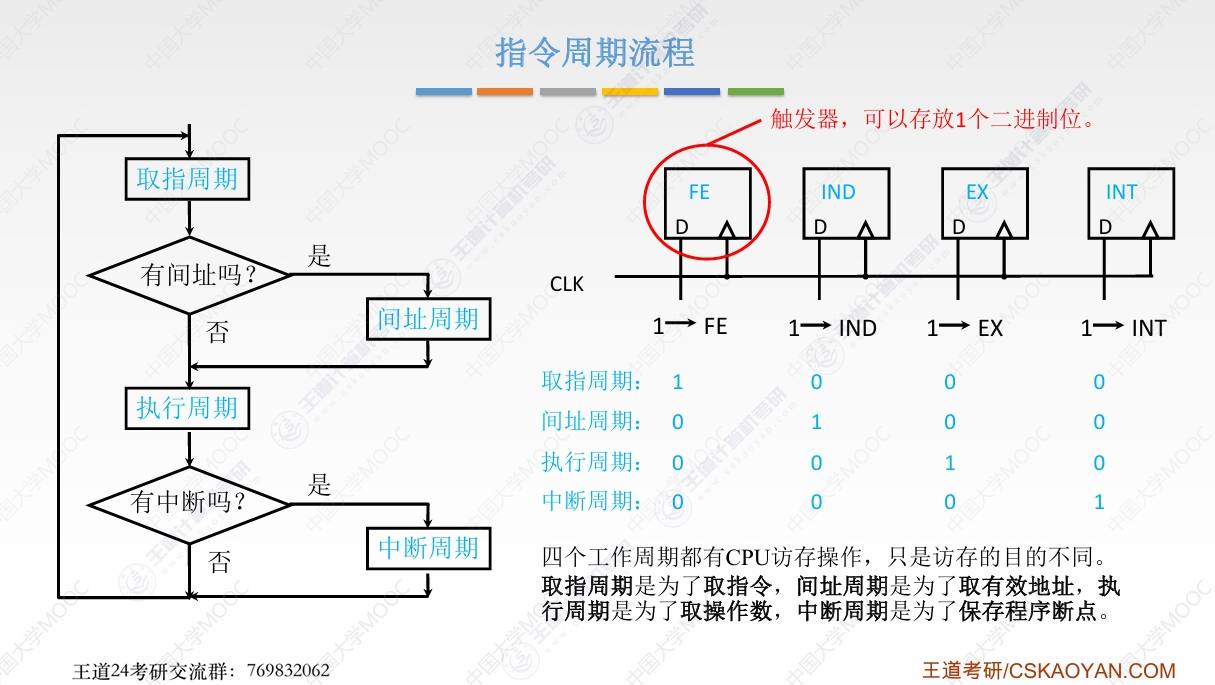

- 控制器根据指令周期来分辨存储单元中的是指令还是数据(取指令阶段取出的是指令,执行指令阶段取出的是数据)

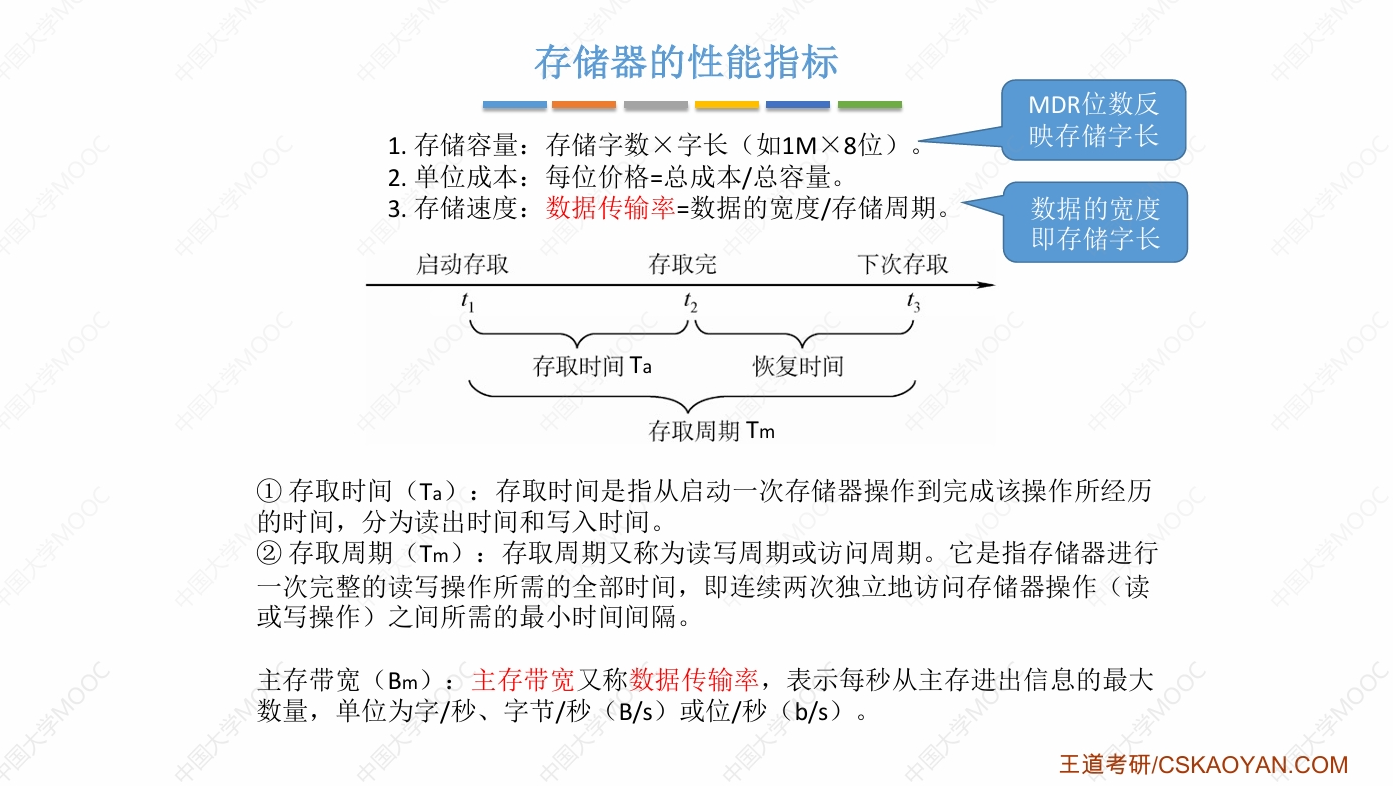

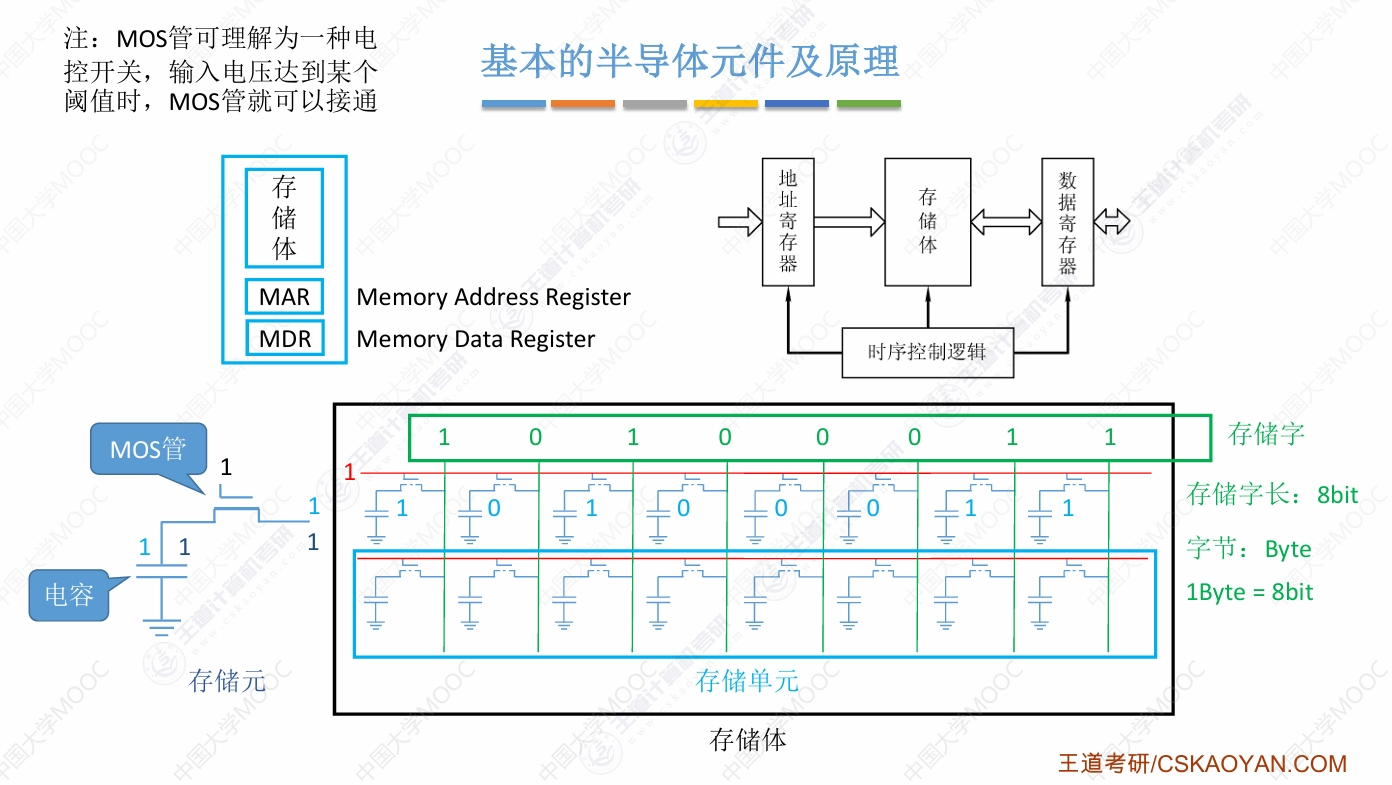

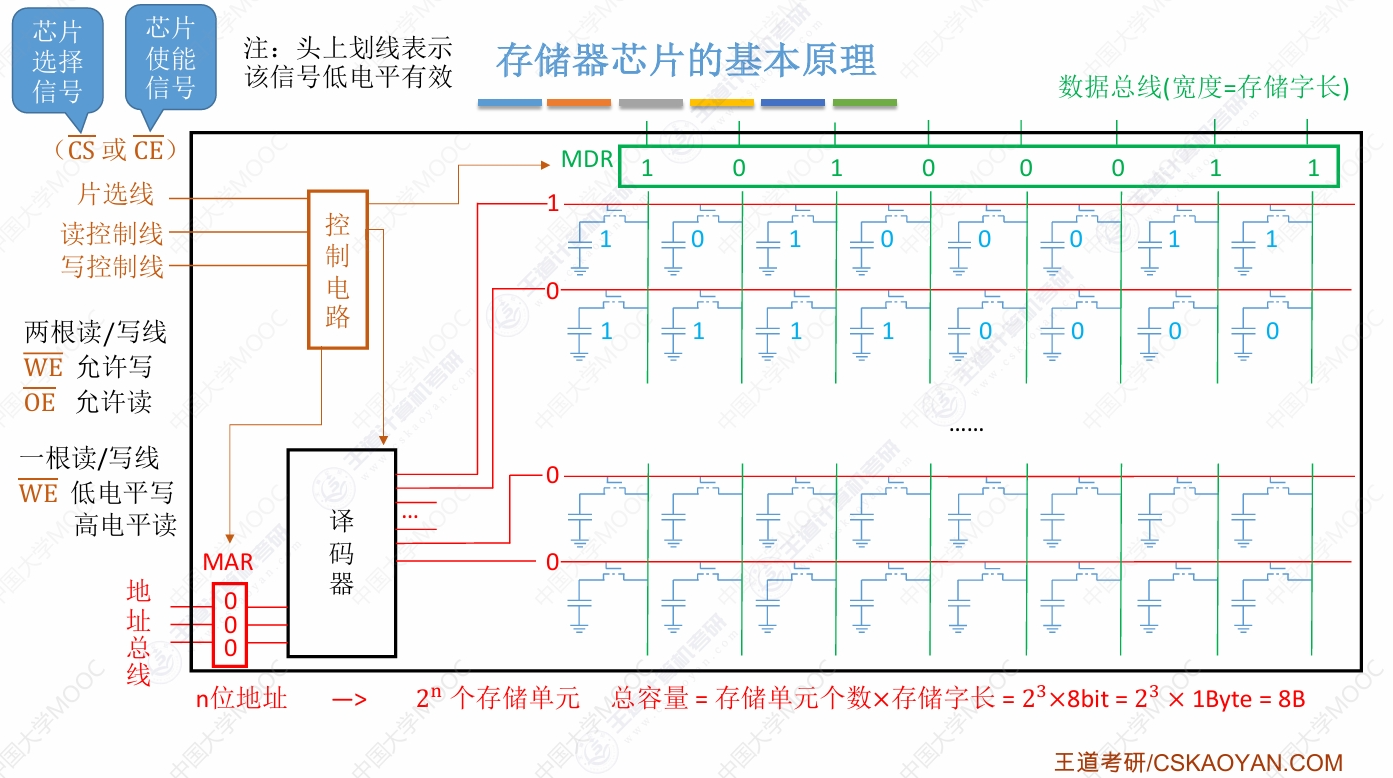

- 存储字长(存储单元中二进制代码的位数)=MDR位数=1个字(word)的长度

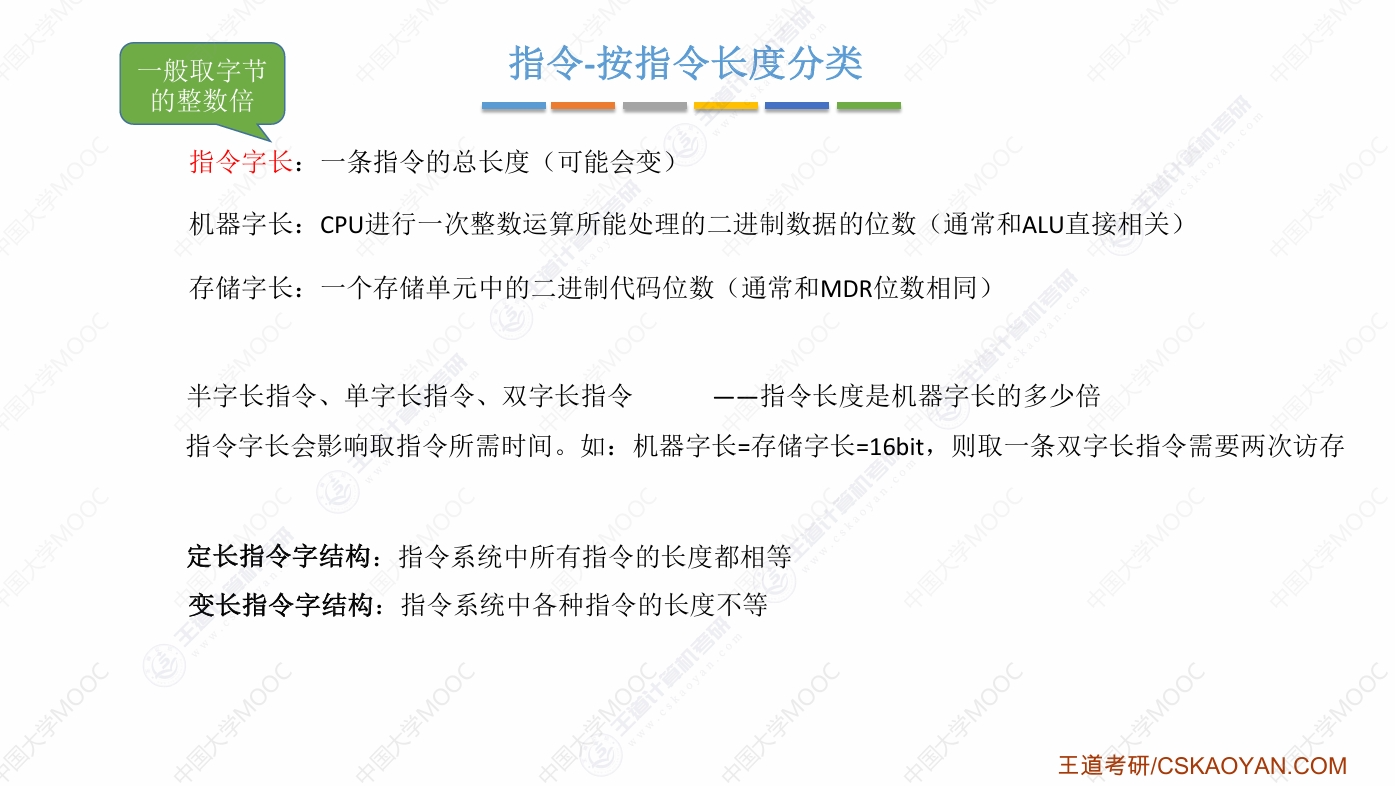

- 指令字长 : 一条指令包含的二进制代码的位数,按指令长度分类为半/单/双字长指令(这里的字长指的是机器字长)

- MAR位数=存储单元数量=地址码长度

- 机器字长=计算机的位数=能够一次性直接处理的二进制数据位数

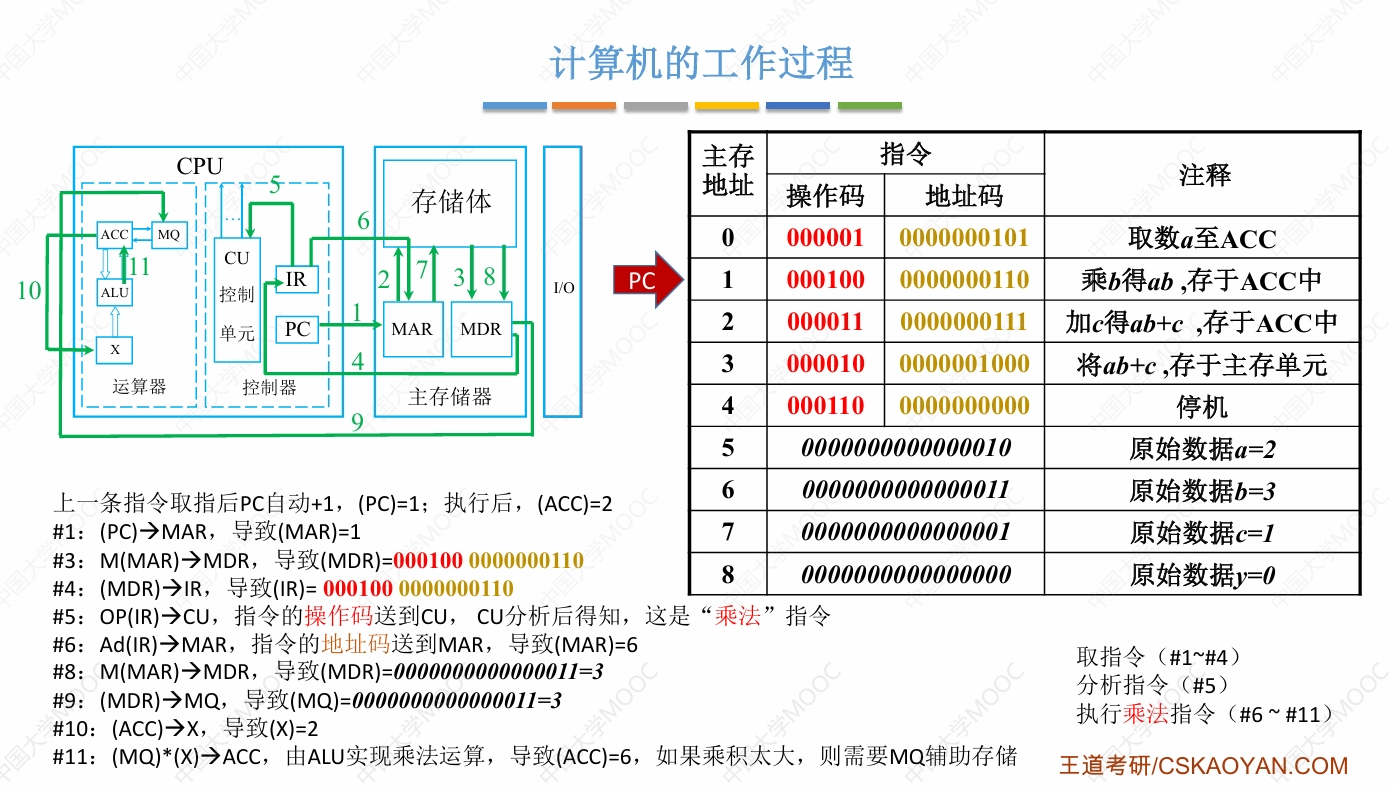

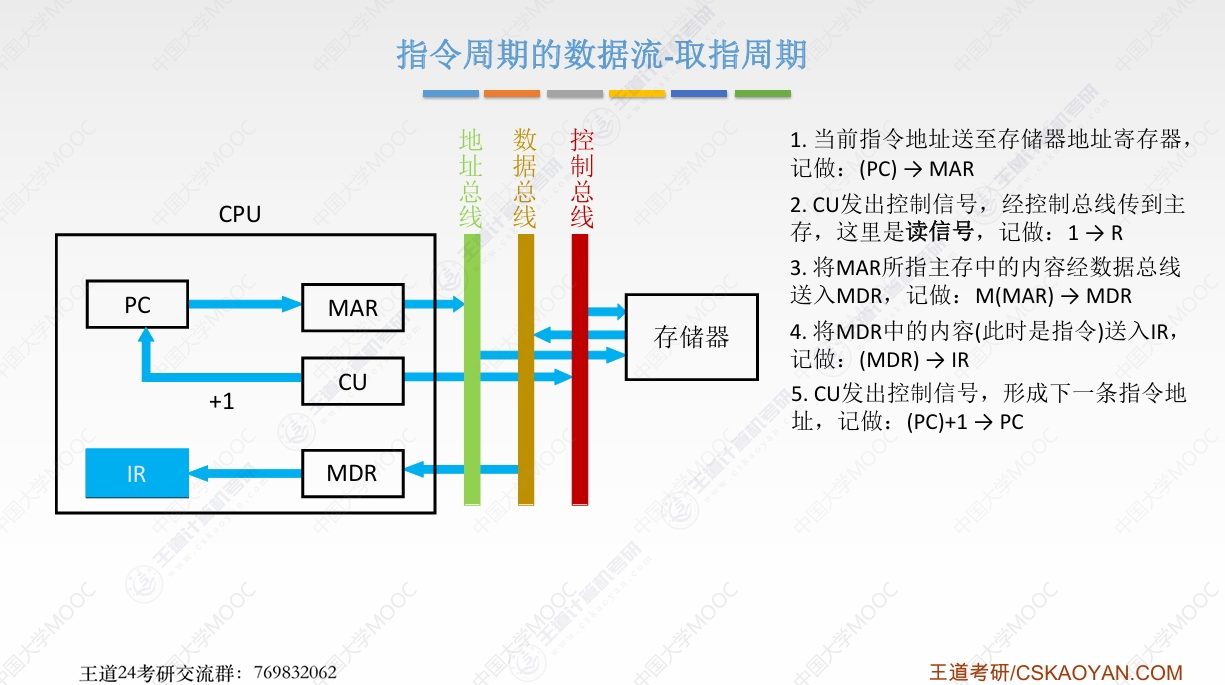

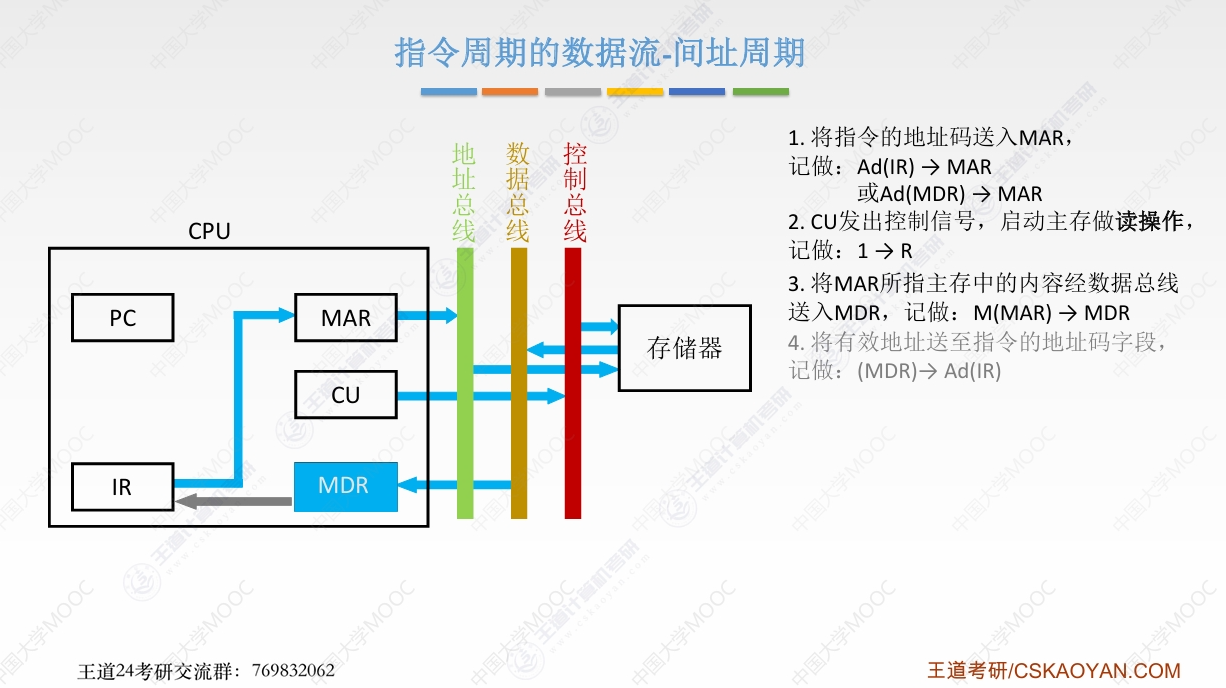

计算机的工作过程

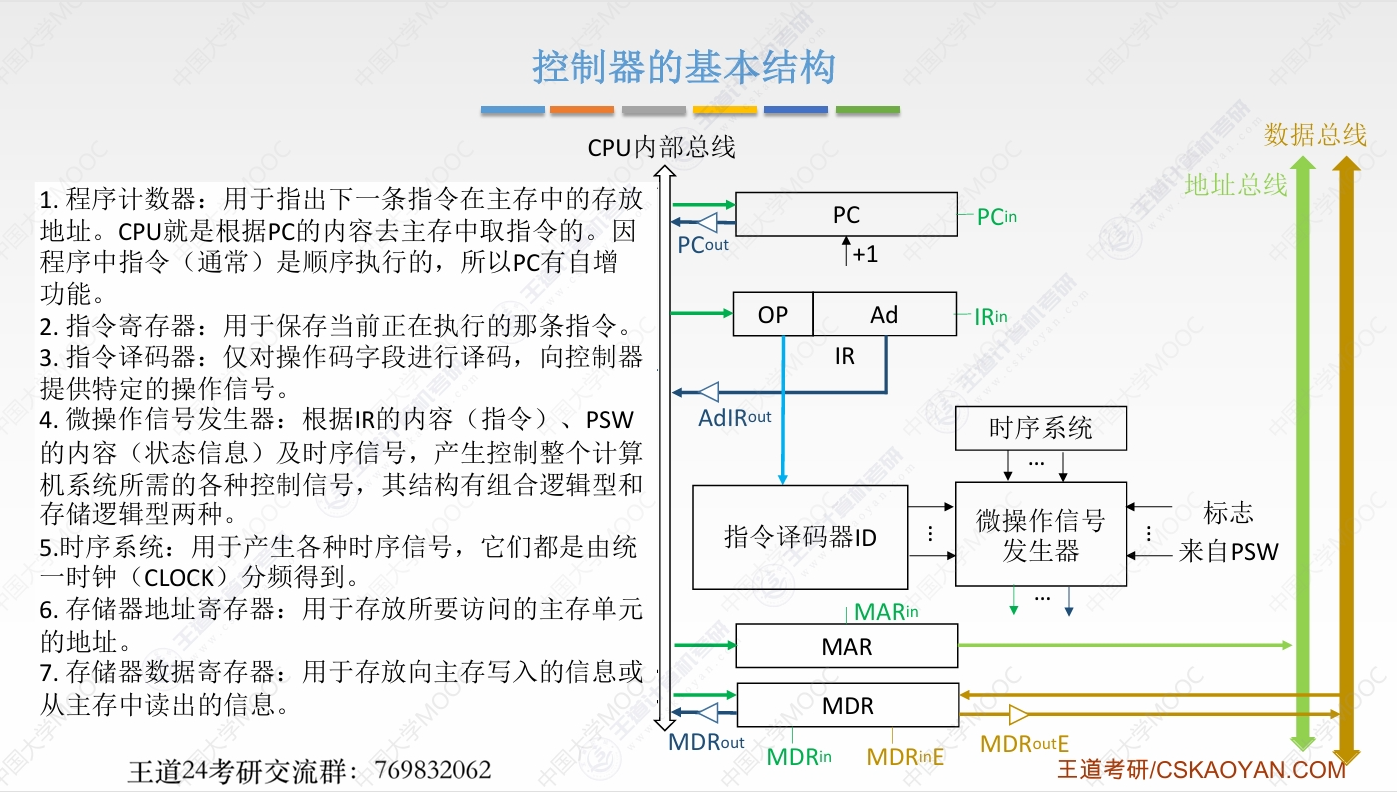

1. PC把主存地址发送给MAR

2. MAR根据主存地址找到对应的指令

3. MDR获得对应的指令

4. MDR把指令发送给IR

5. IR把操作码发送给CU,CU分析操作码

6. IR根据地址码找到对应的主存地址并把主存地址对应的指令地址发送给MAR

7. MAR根据指令地址找到对应的指令

8. MDR获得对应的指令

9. MDR将指令(乘数)发送给MQ

10. ACC将上一步的运算结果(被乘数)发送给X

11. ALU将运算结果发送给ACC

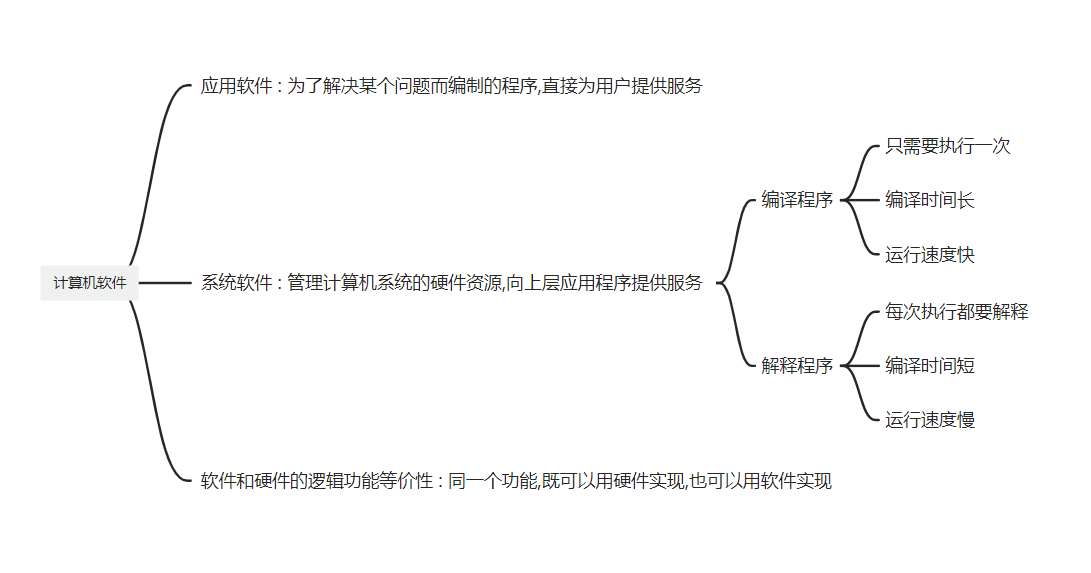

- 数据库管理软件(DBMS)是系统软件,数据库软件(DBS)是应用软件

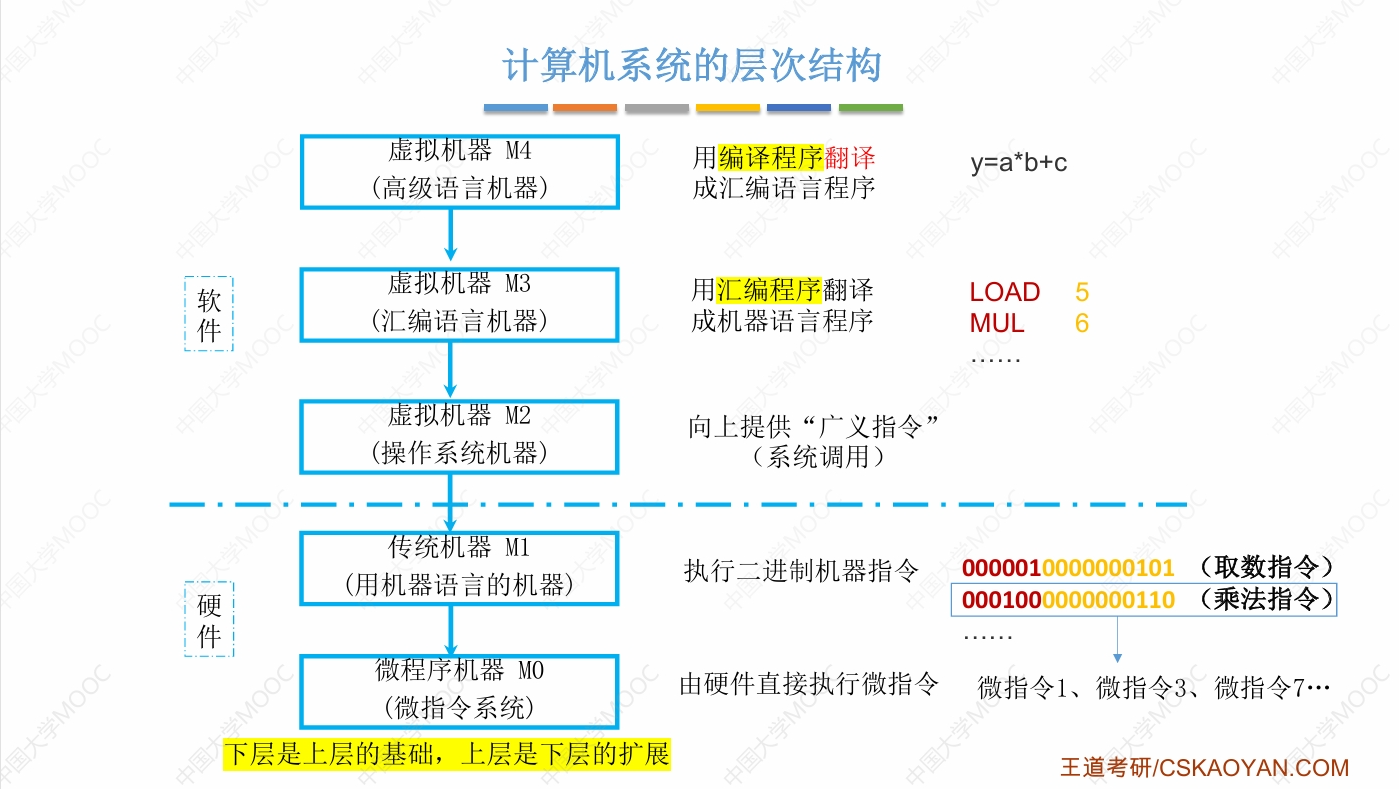

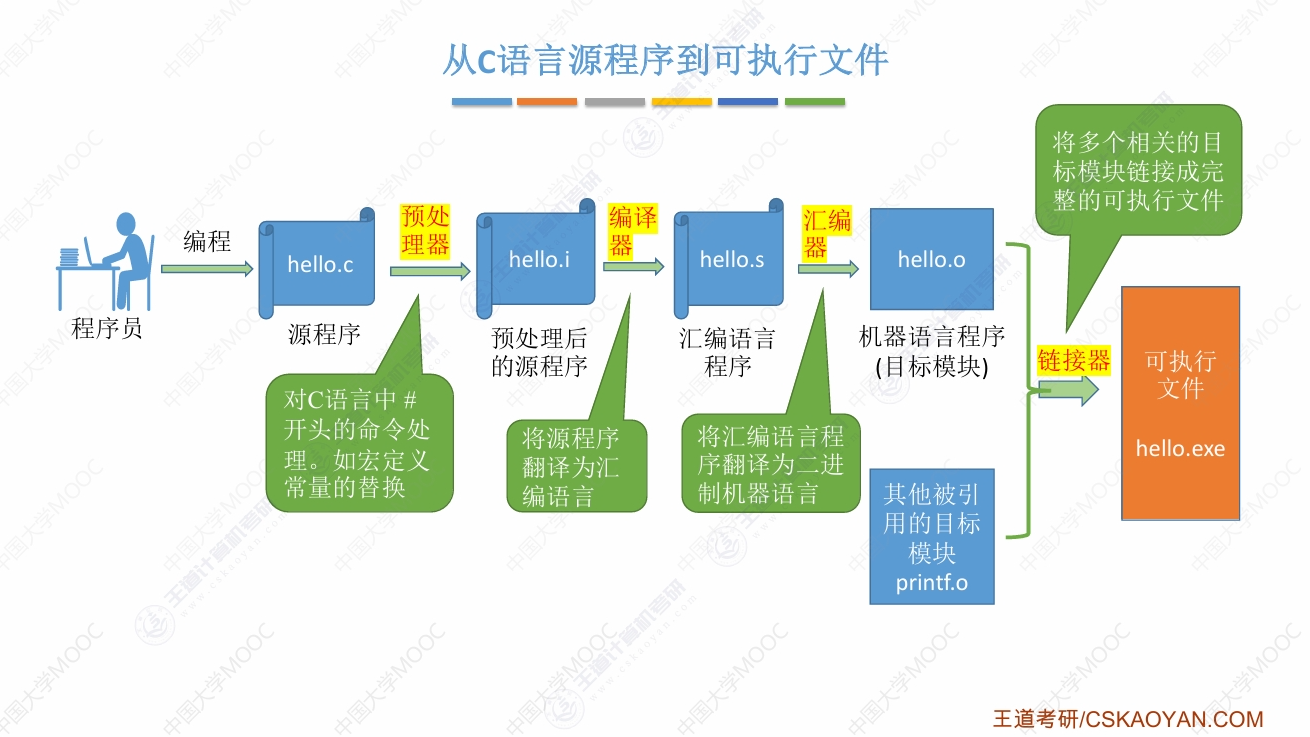

- 编译程序(编译器)也可直接将高级语言翻译成机器语言

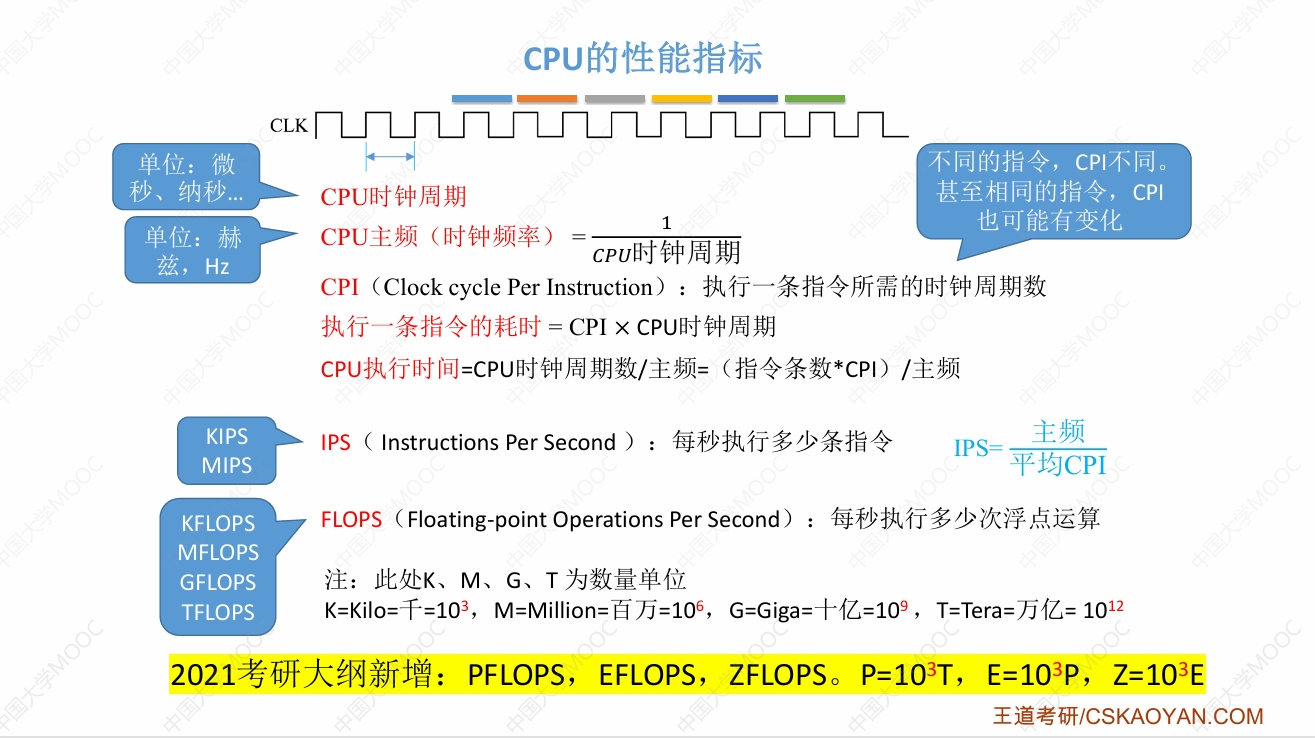

- K,M,G,T等单位,描述文件大小,存储容量时以2为底,描述速率,频率时以10为低

- 机器字长 : 衡量计算机并行处理的能力

- 数据通路带宽 : 衡量计算机在功能级部件间传输数据的能力

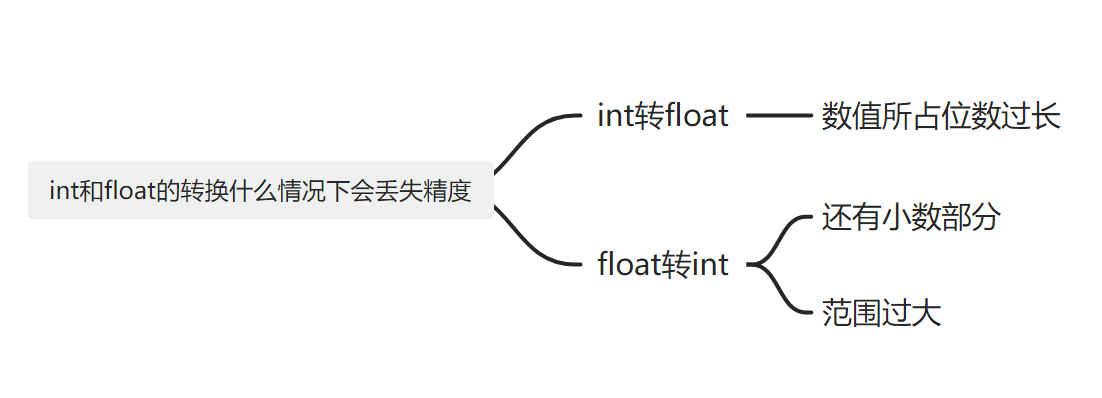

二丶数据的表示和运算

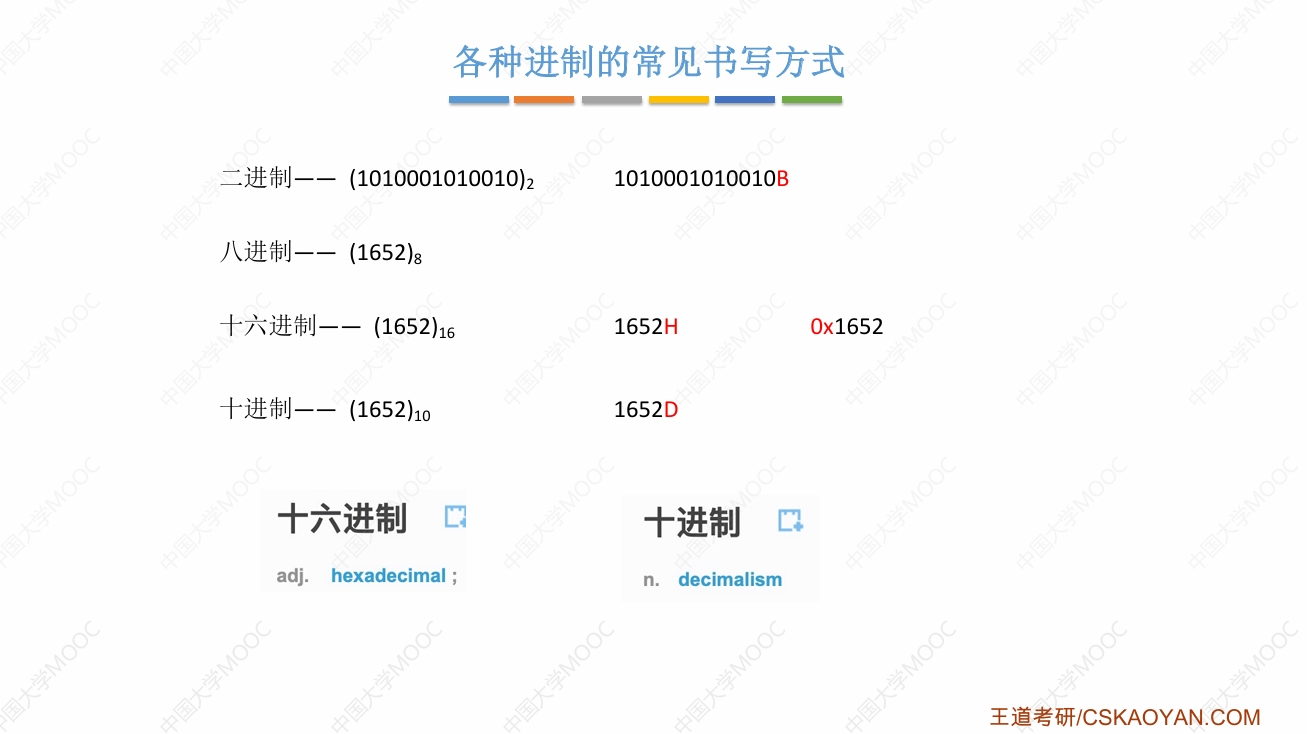

- 二进制转换成八进制/十六进制 : 整数在头部补零,小数在尾部补零

- 并不是每个十进制小数都可以准确的用二进制表示

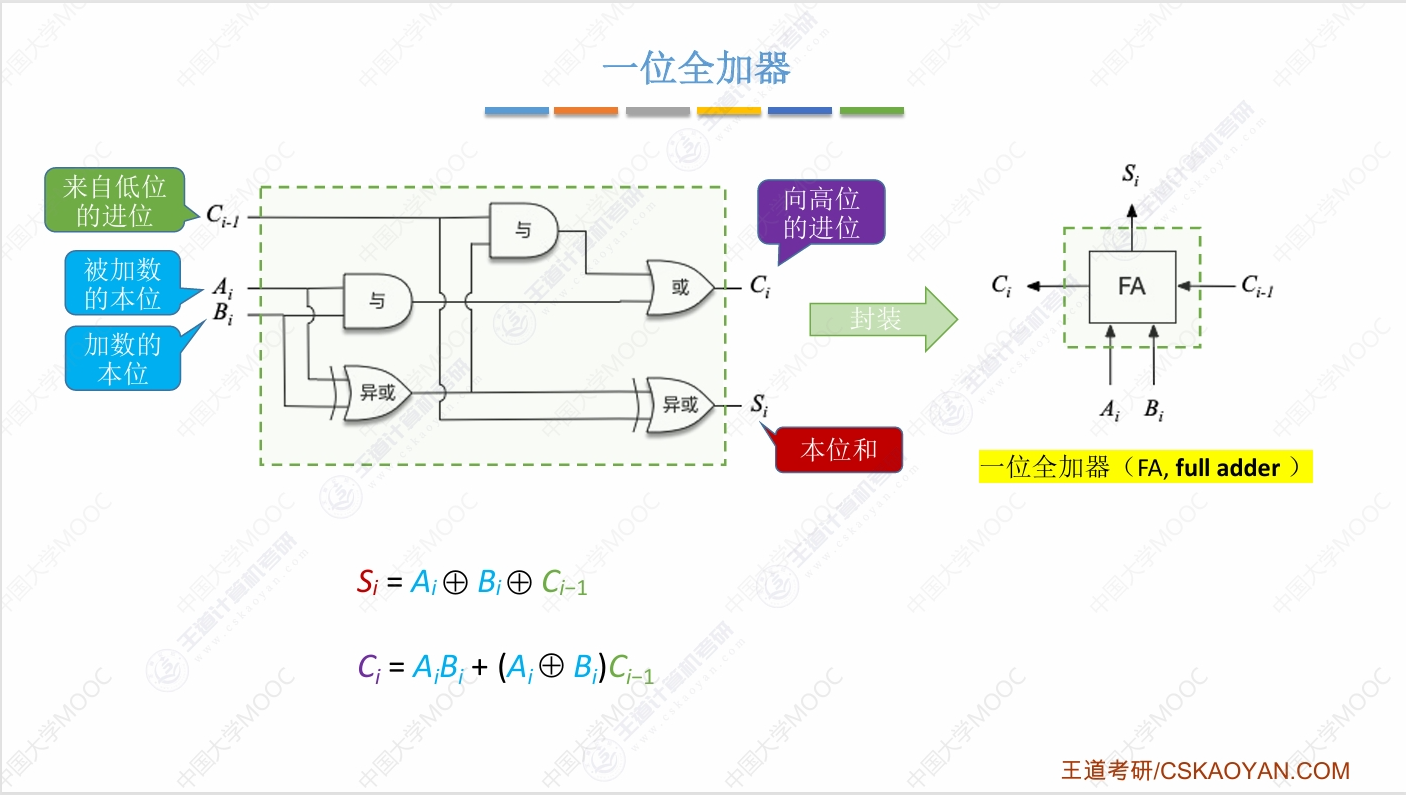

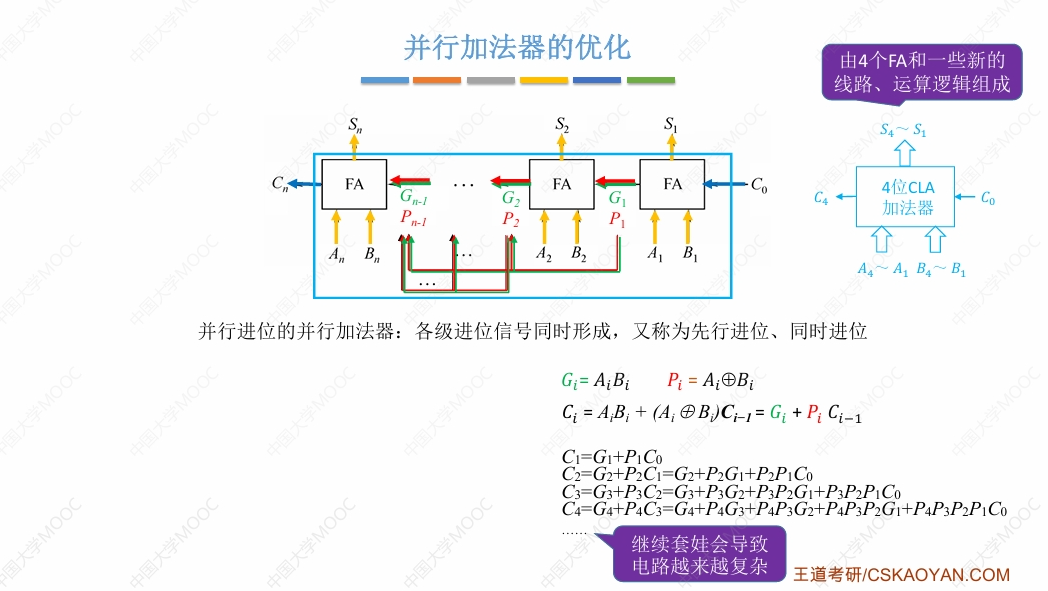

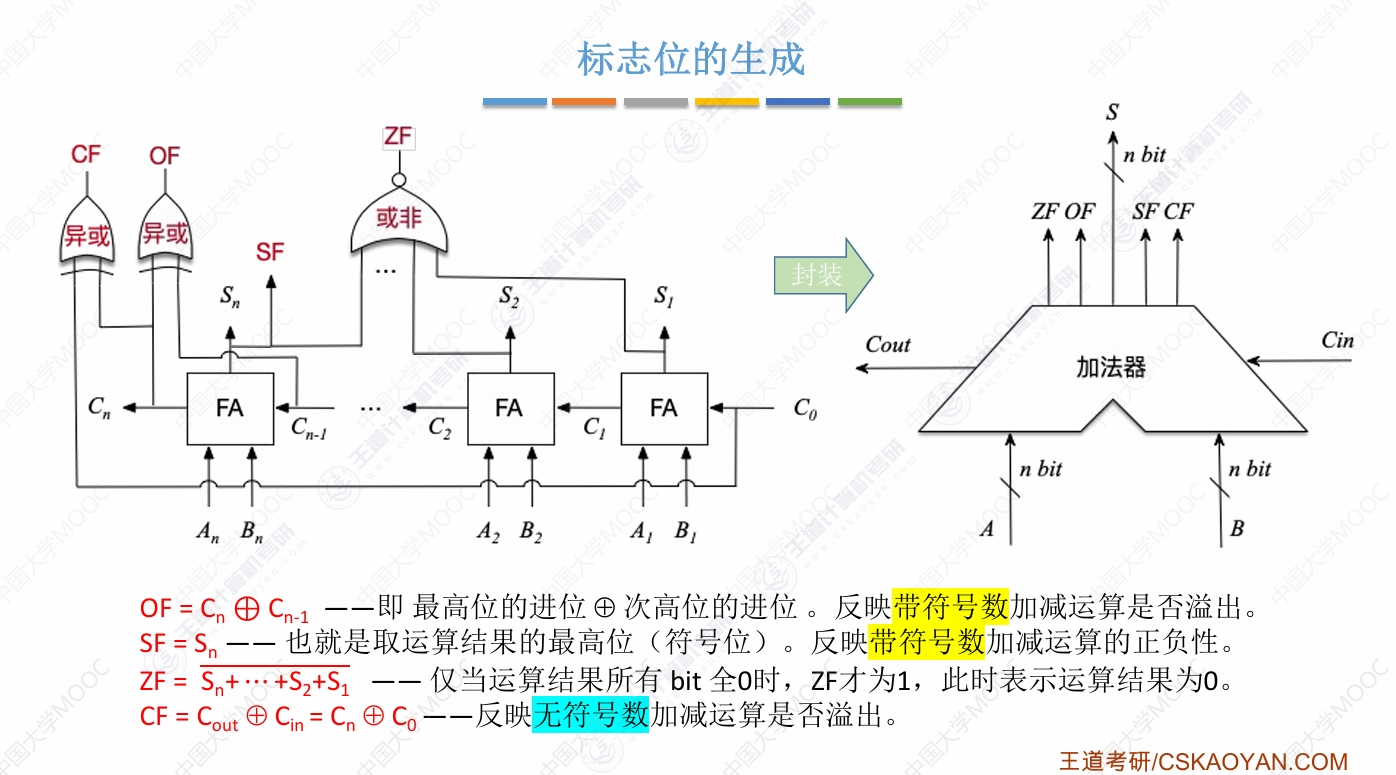

- g=进位生成信号,p=进位传递信号

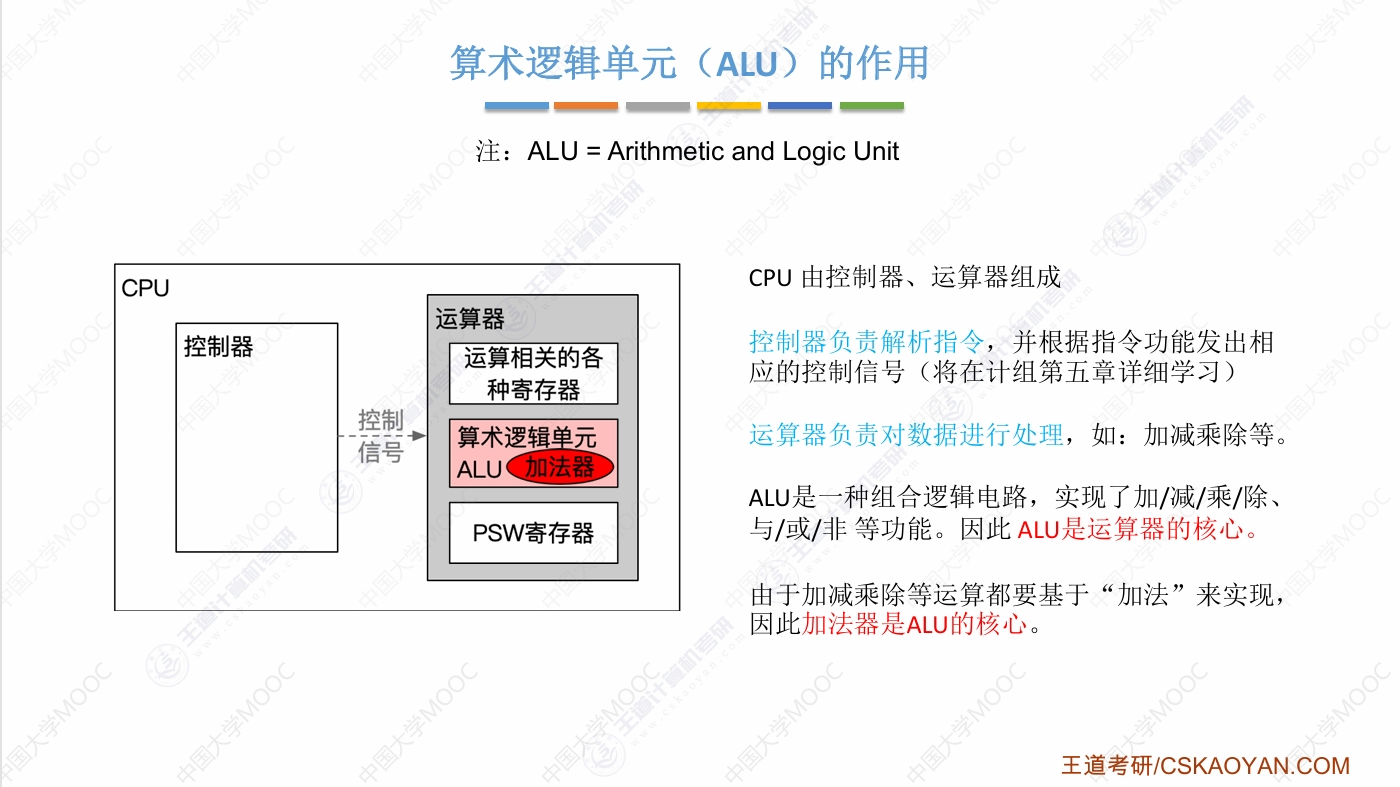

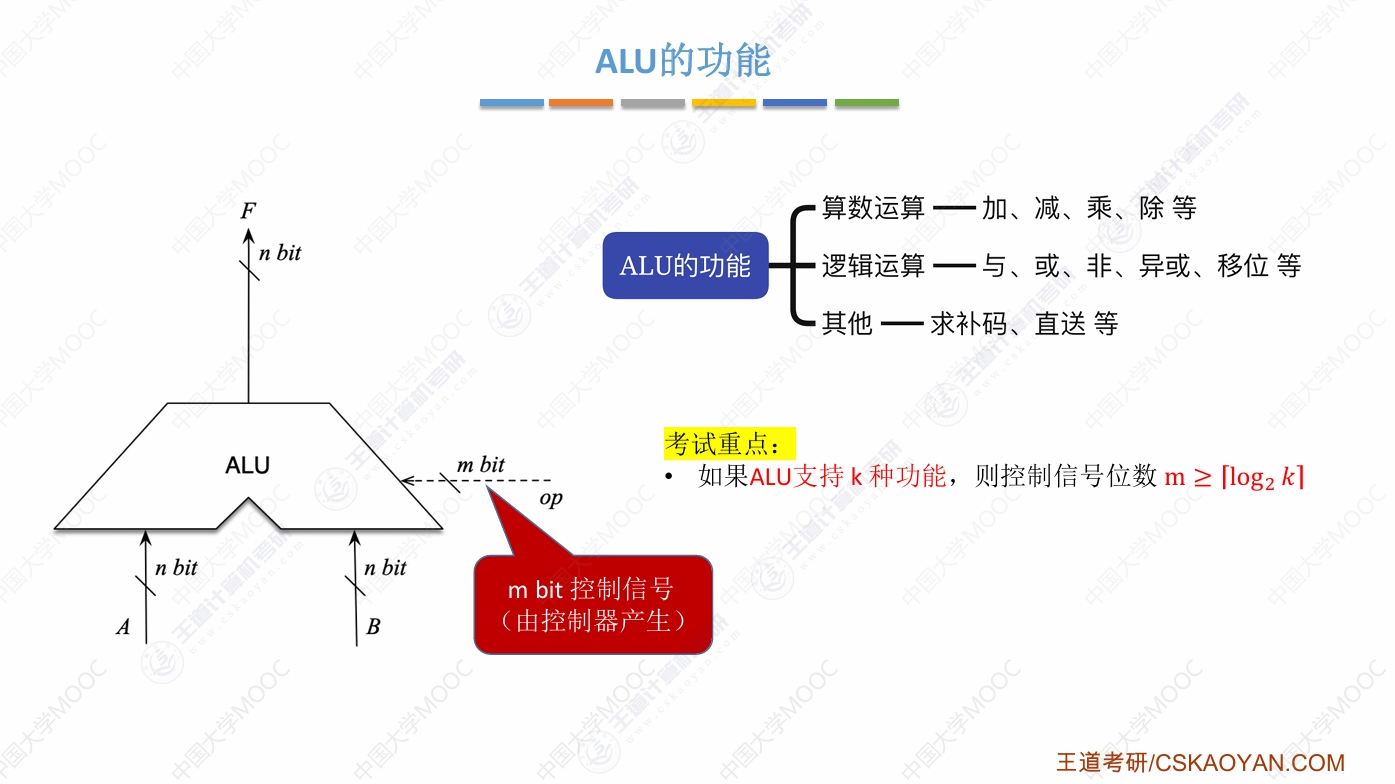

- ALU的运算数,运算结果位数与计算机的机器字长相同

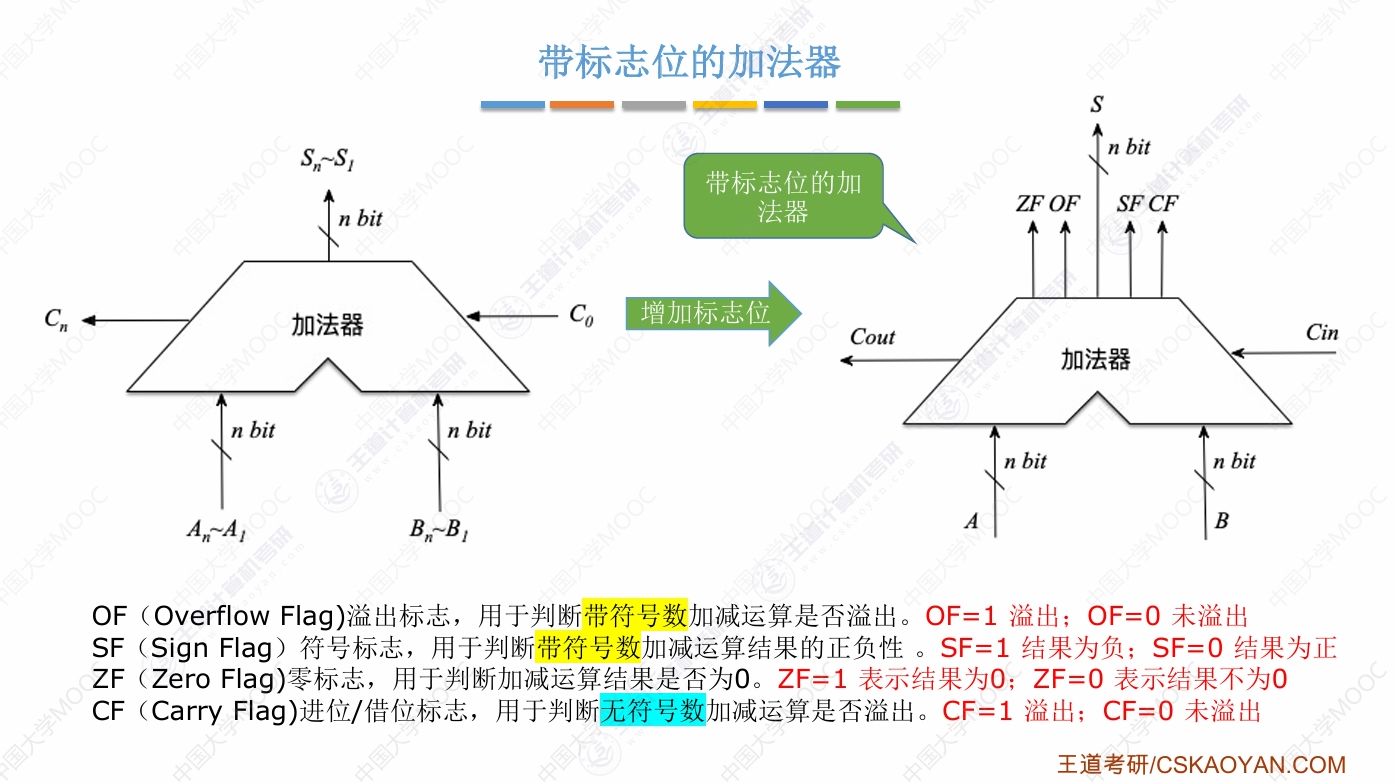

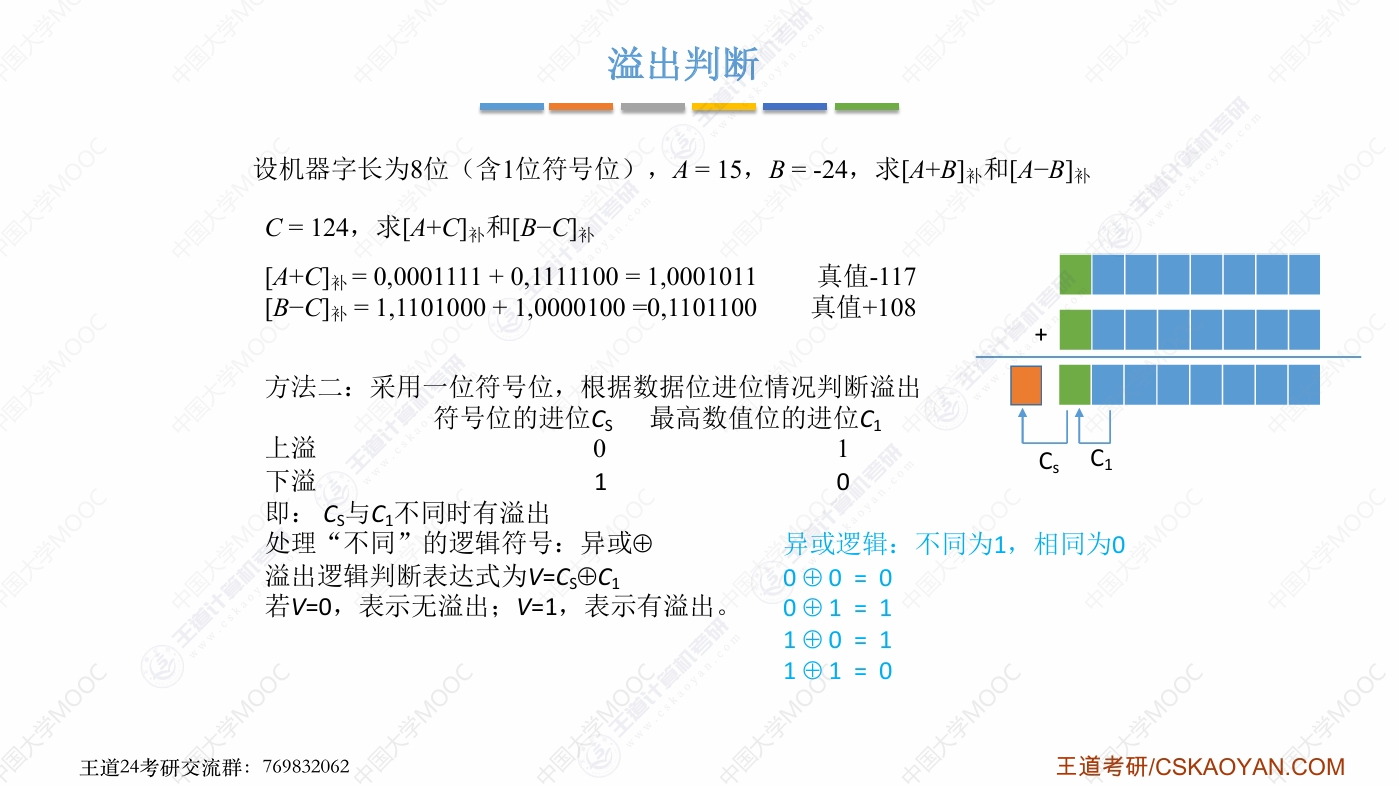

加减溢出问题

1.正+正=正,负+负=负

2.双符号位的异同

3.符号位进位和最高有效数值位进位的异同(左移也算进位)

- 变形补码就是双符号位补码

- 模4补码更容易检查加减运算中的溢出问题

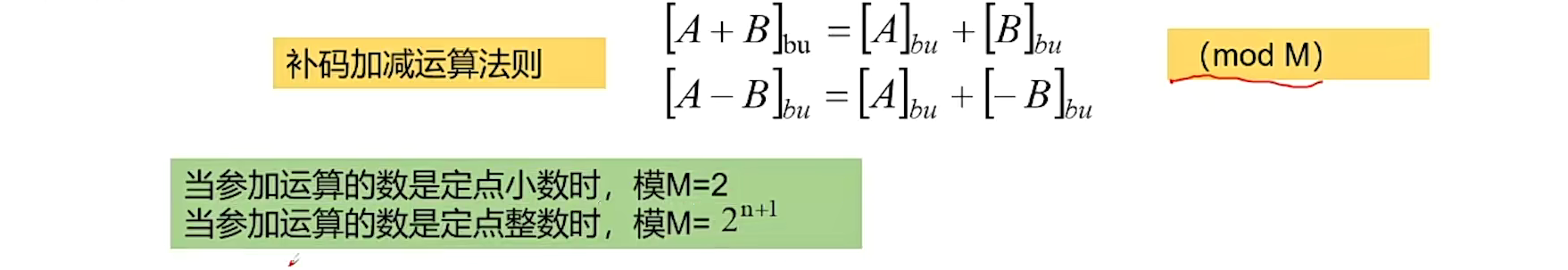

- 加减运算的溢出判断由异或逻辑来处理

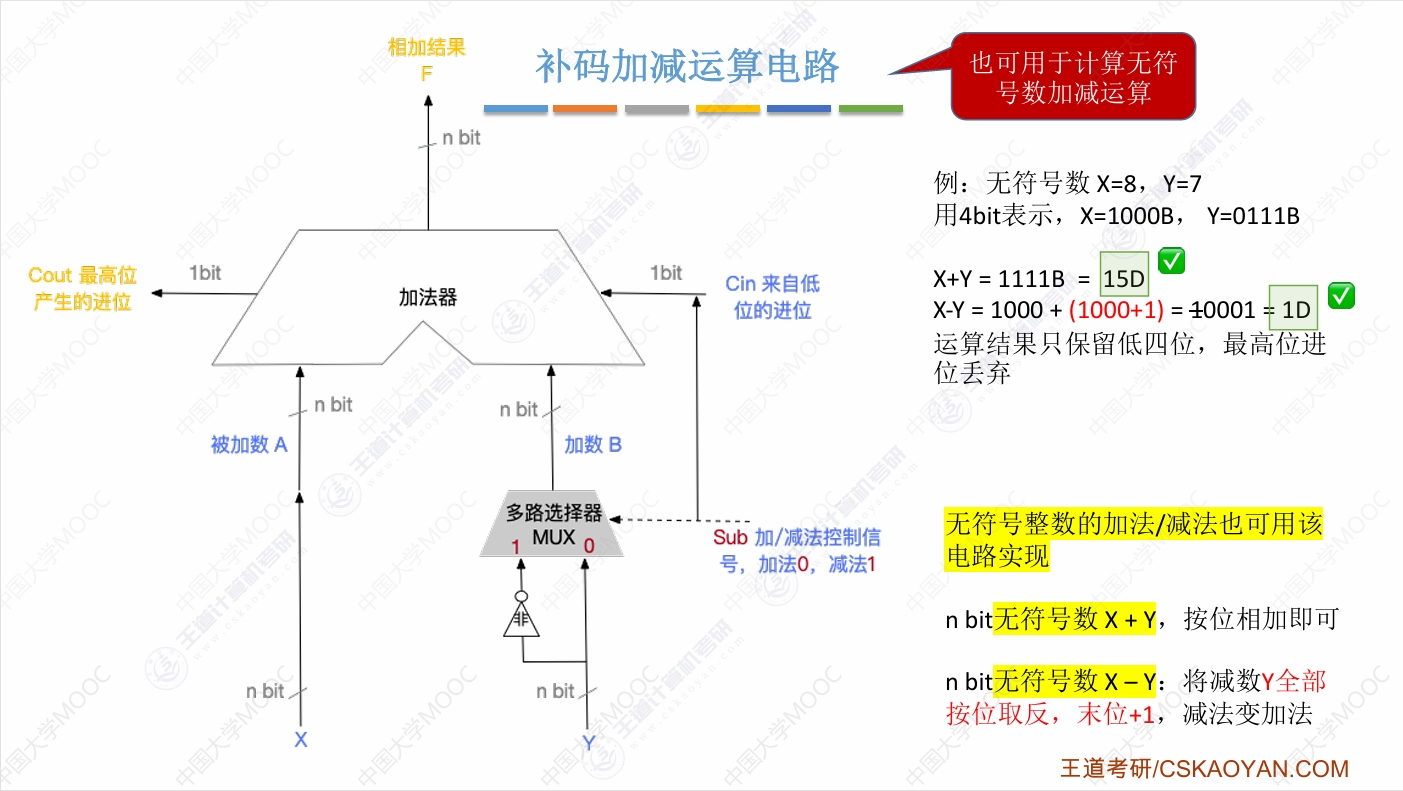

- 无符号数的加法运算等价于带符号数(补码)的加法运算

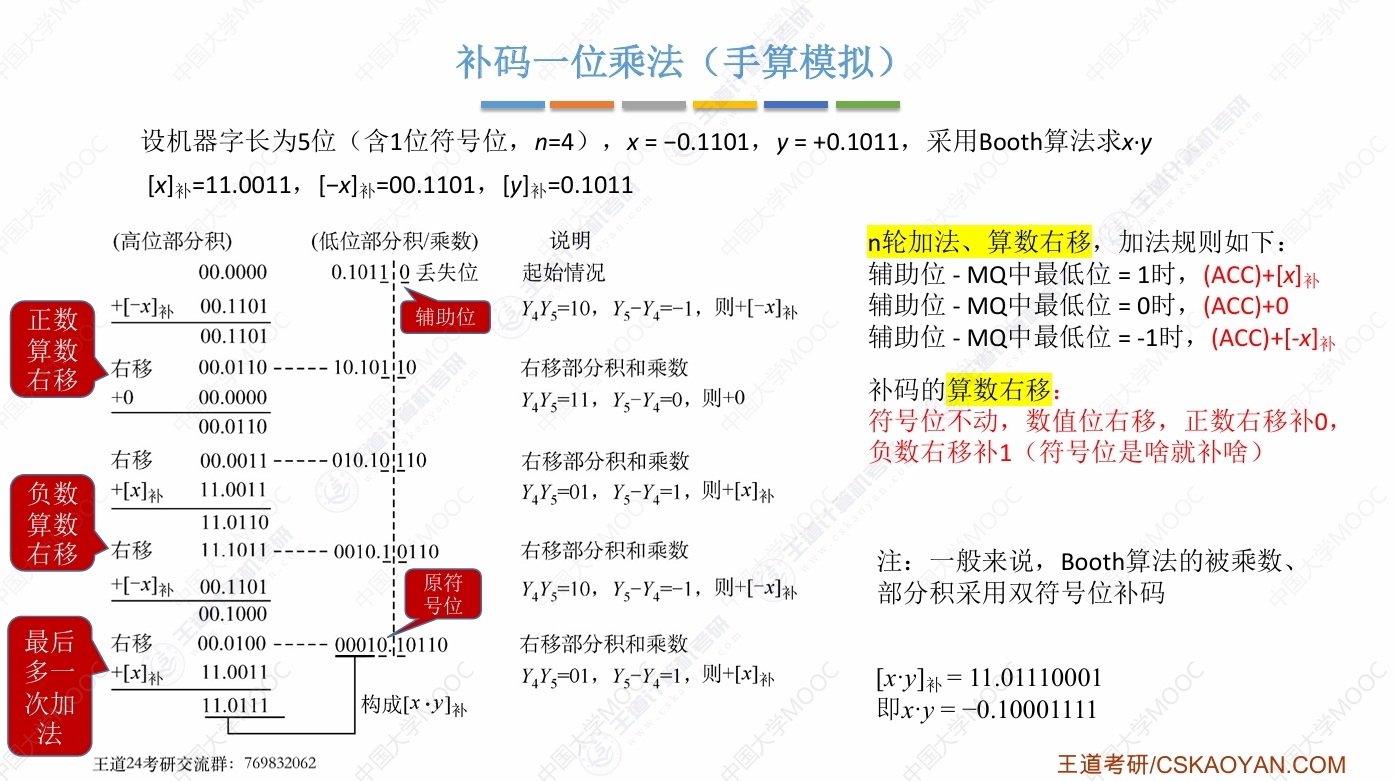

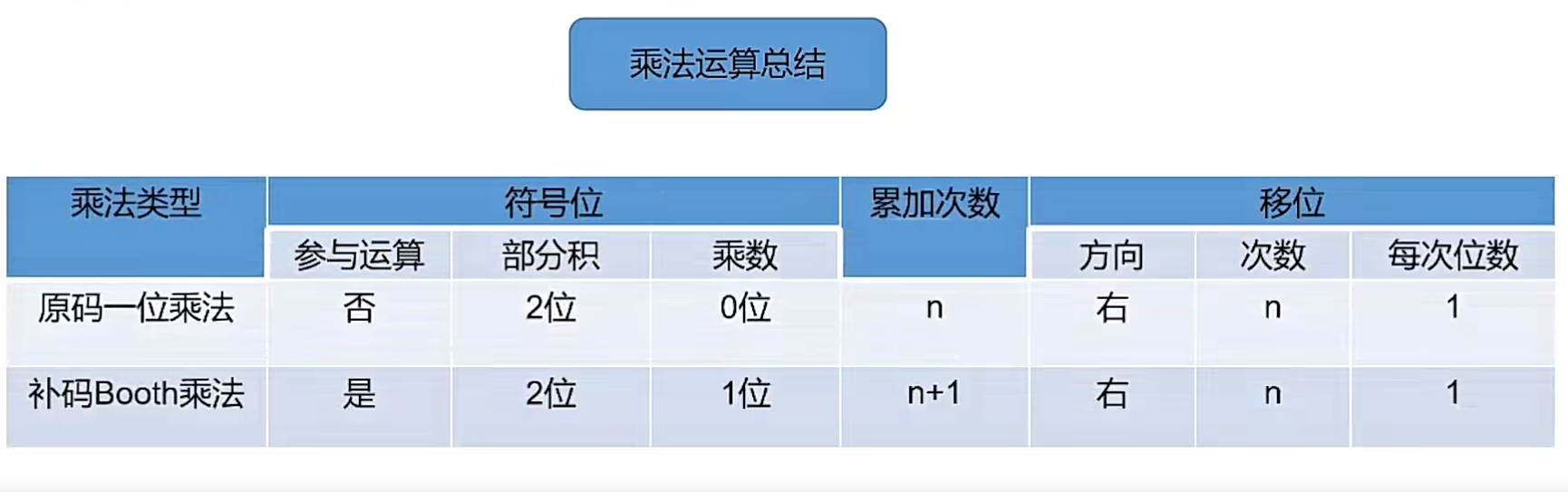

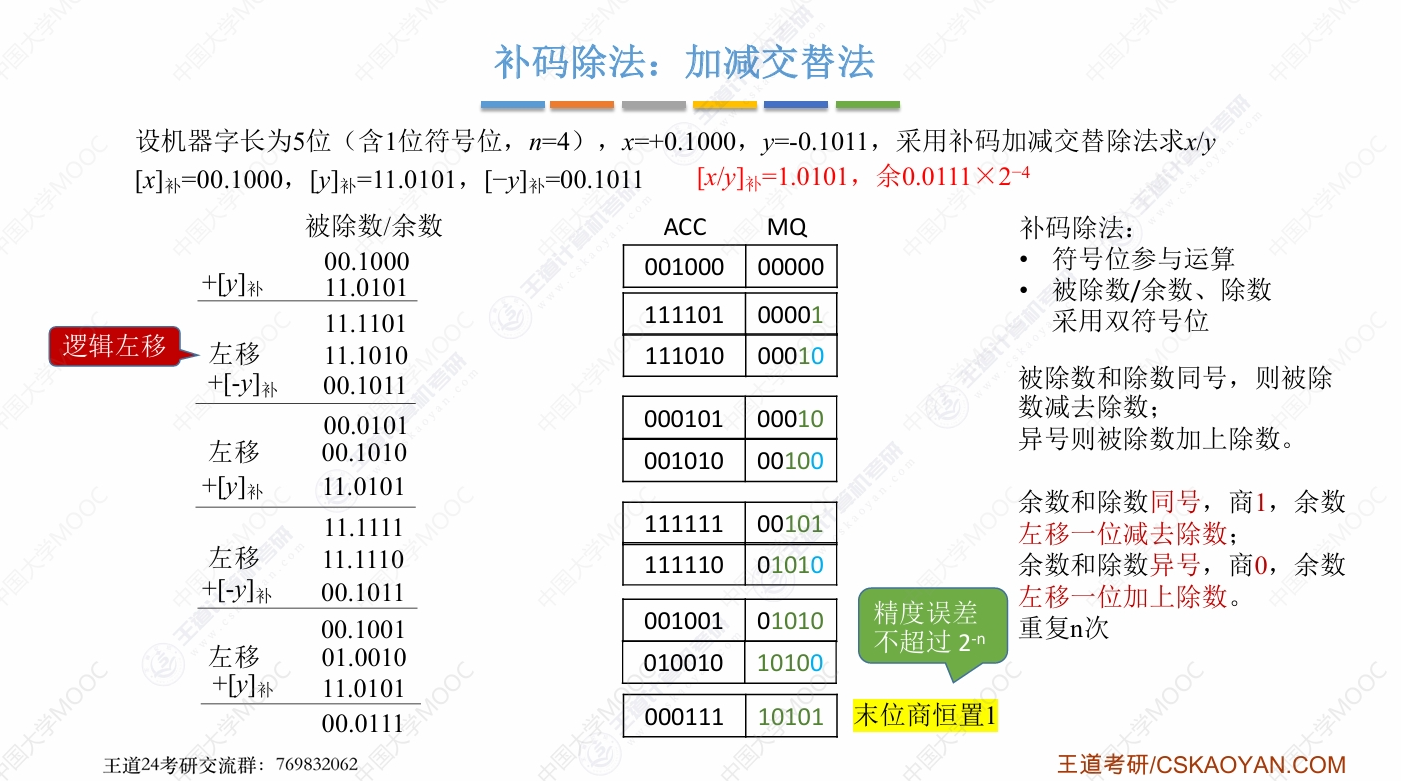

- n是数值位的个数

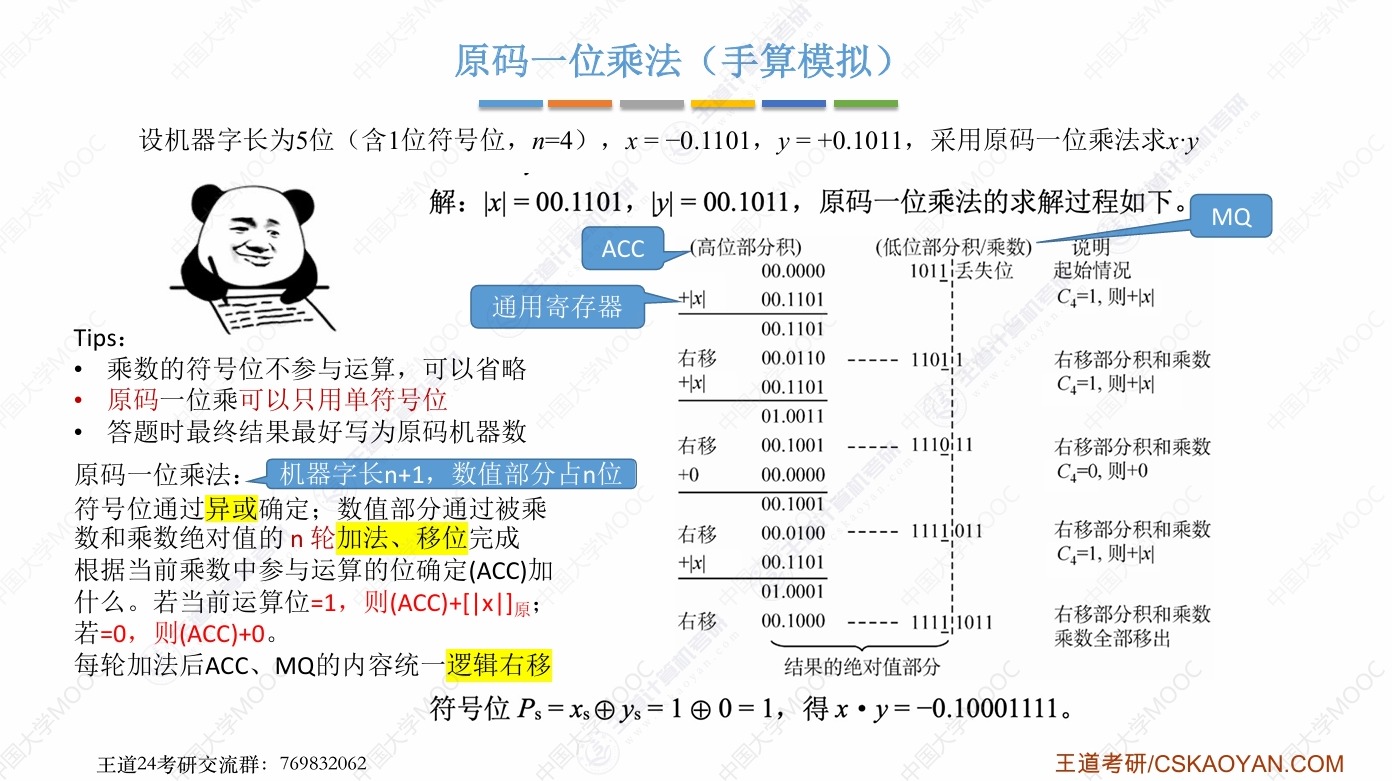

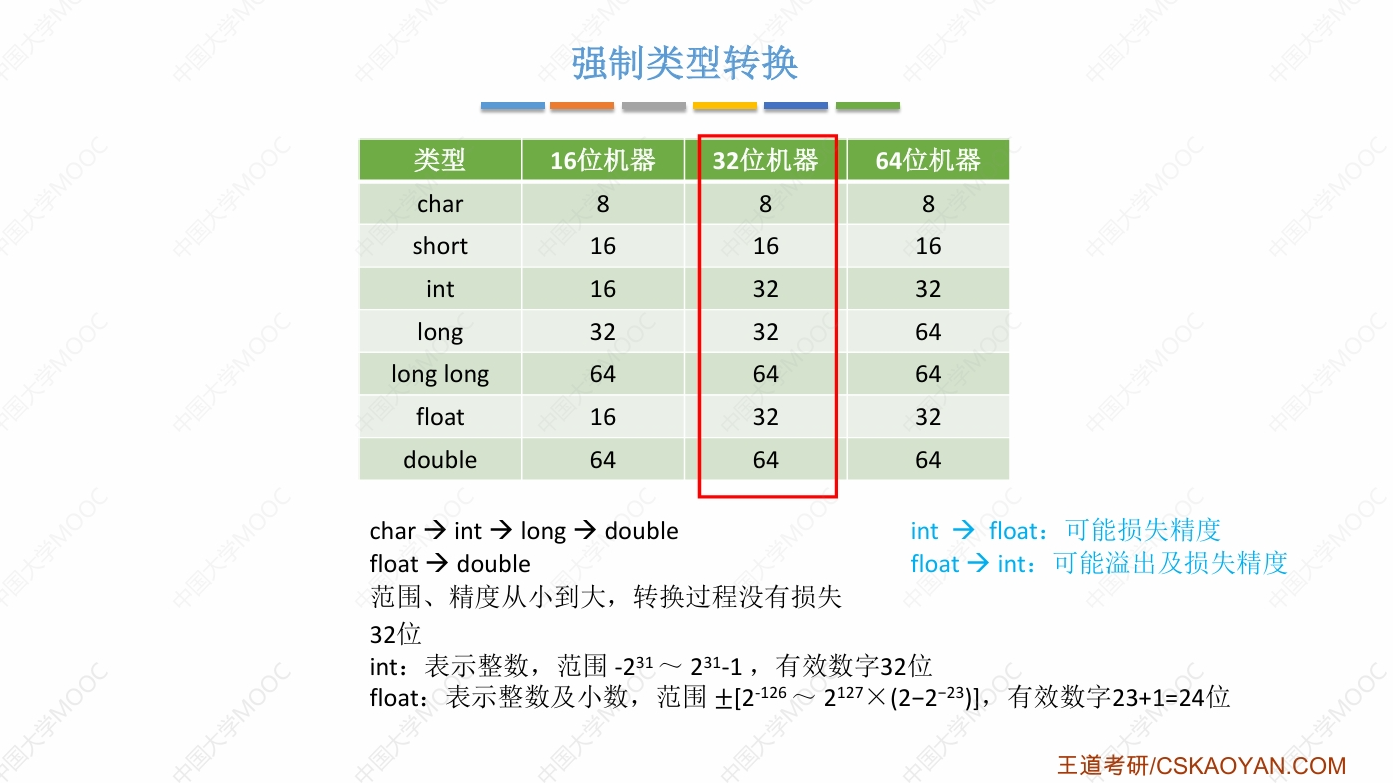

- 乘积位数 : 原码乘法n位,补码乘法n+1位(多了一个符号位)

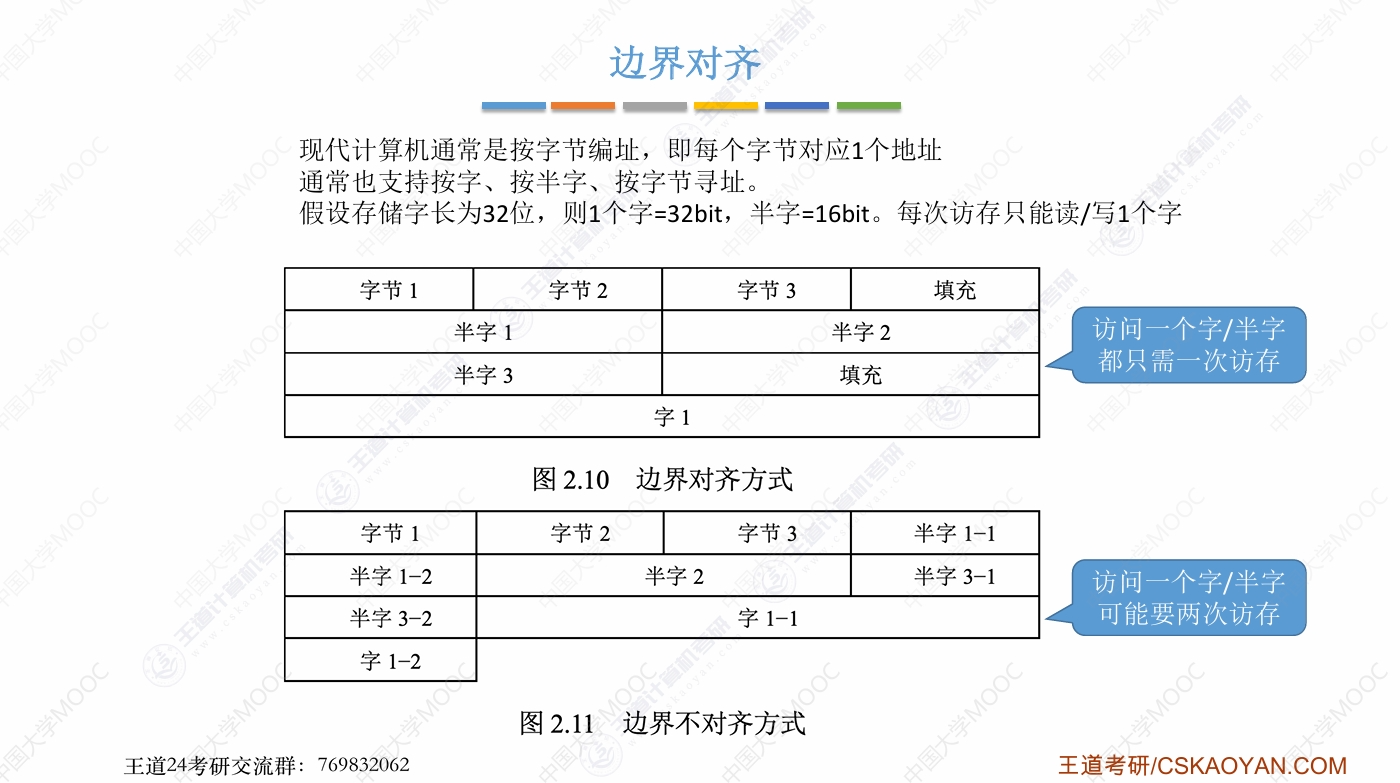

- 在边界对齐方式中,一个结构体所占用的空间一定是机器字长的整数倍,数据存放的首地址一定是数据自身长度(字节)的整数倍

- 边界对齐问题中,告诉我们数据的类型就是告诉我们他们占几个字节

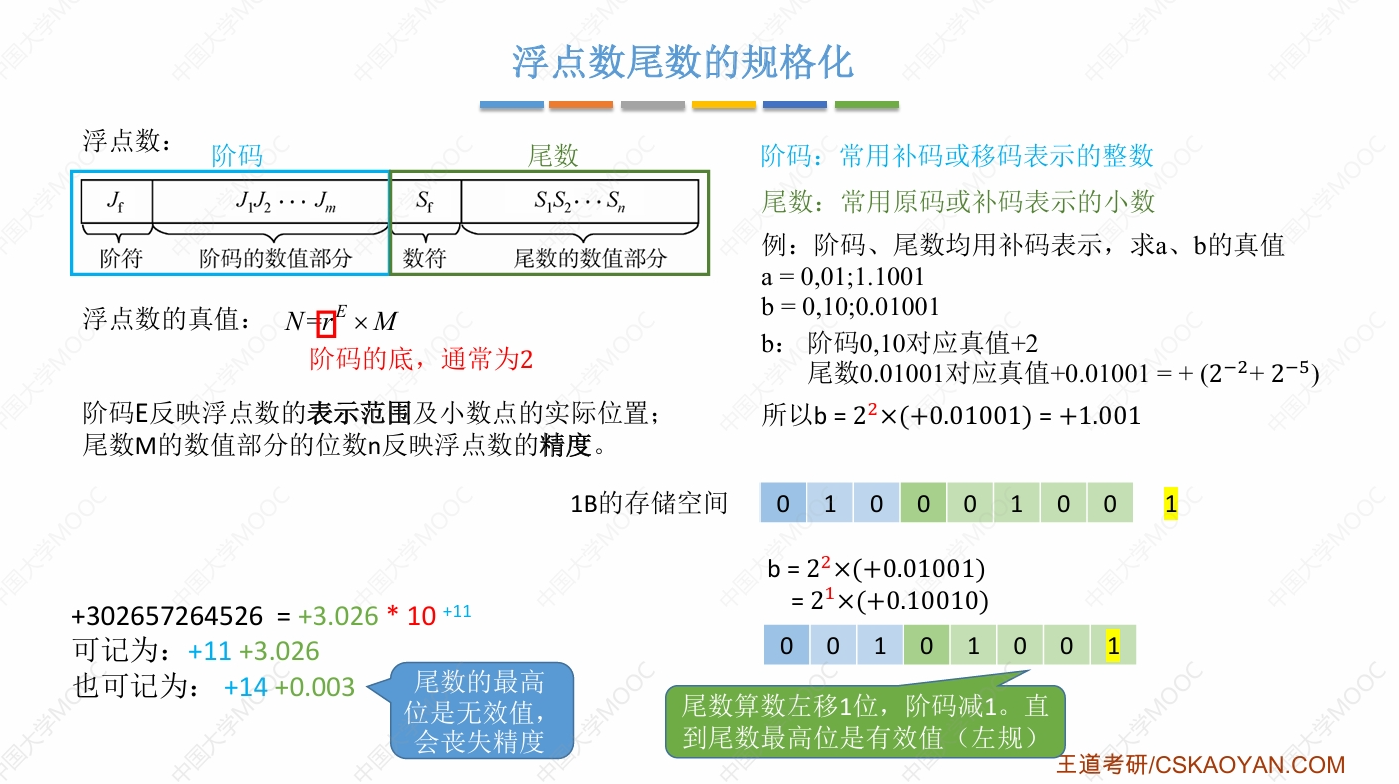

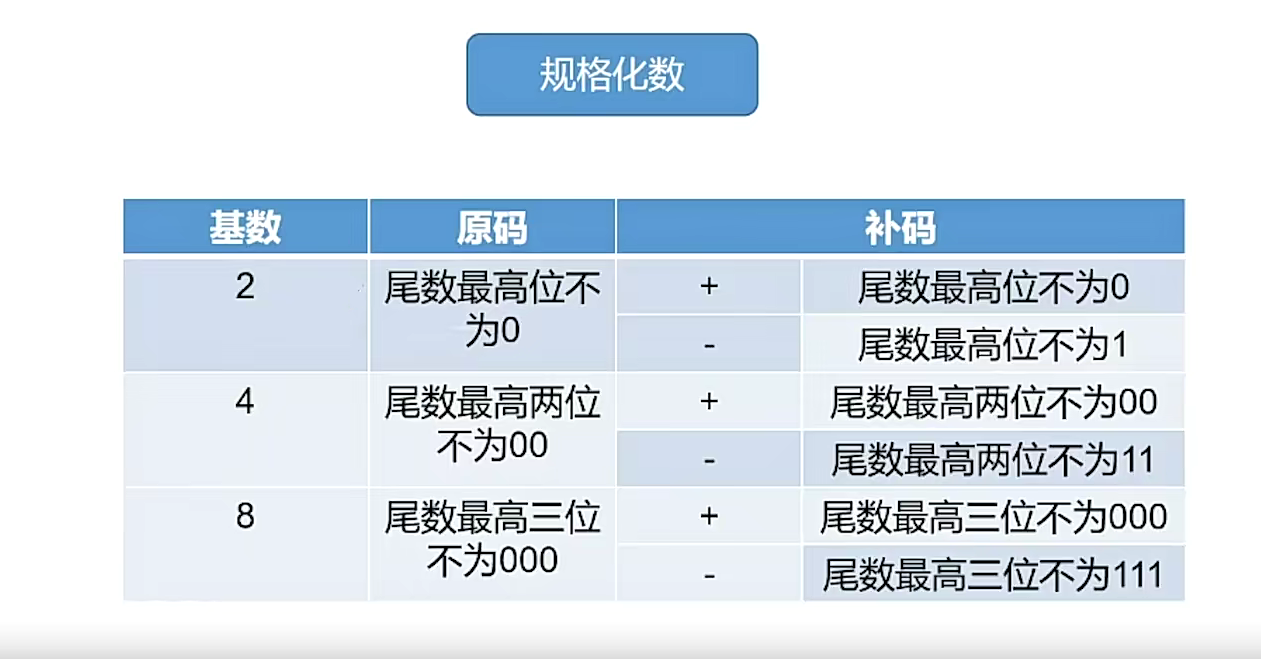

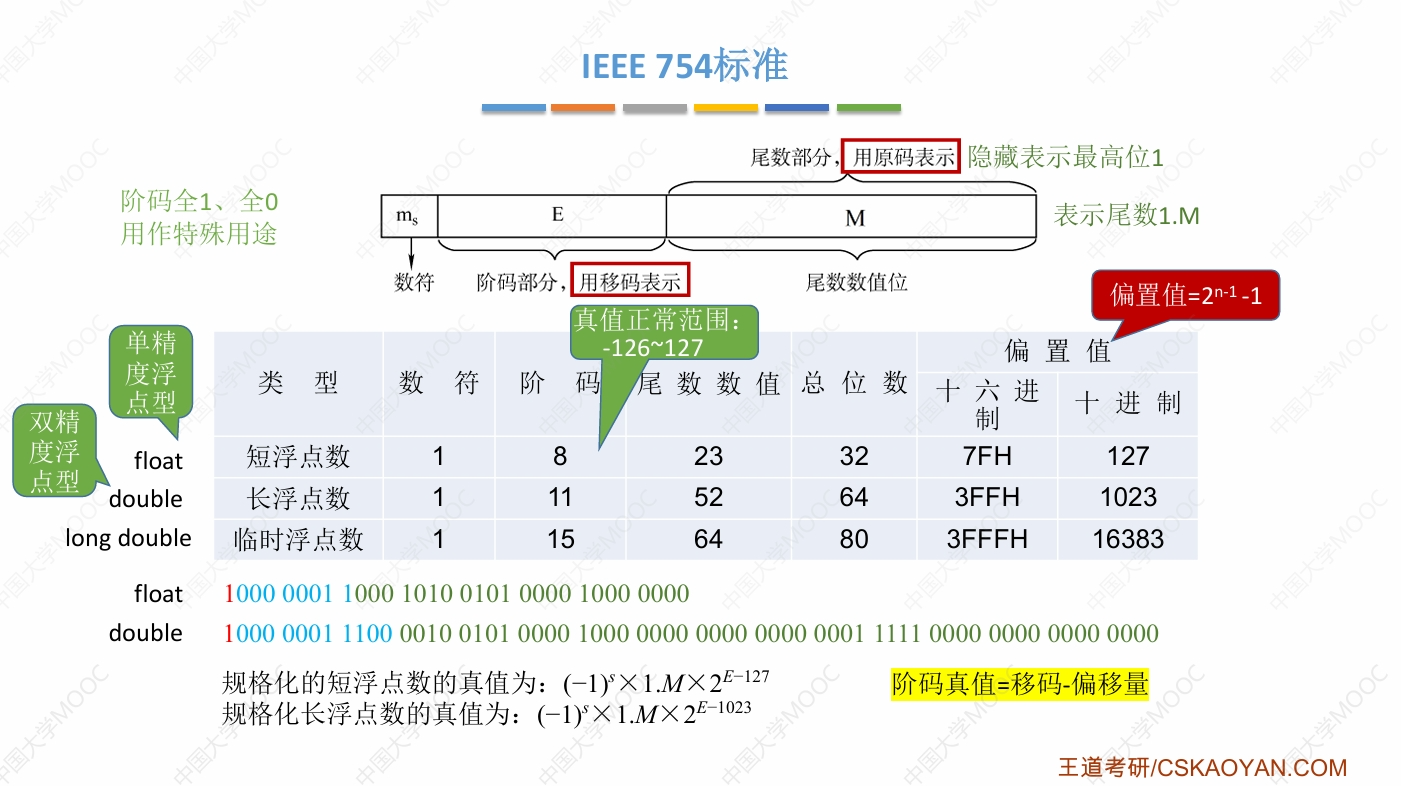

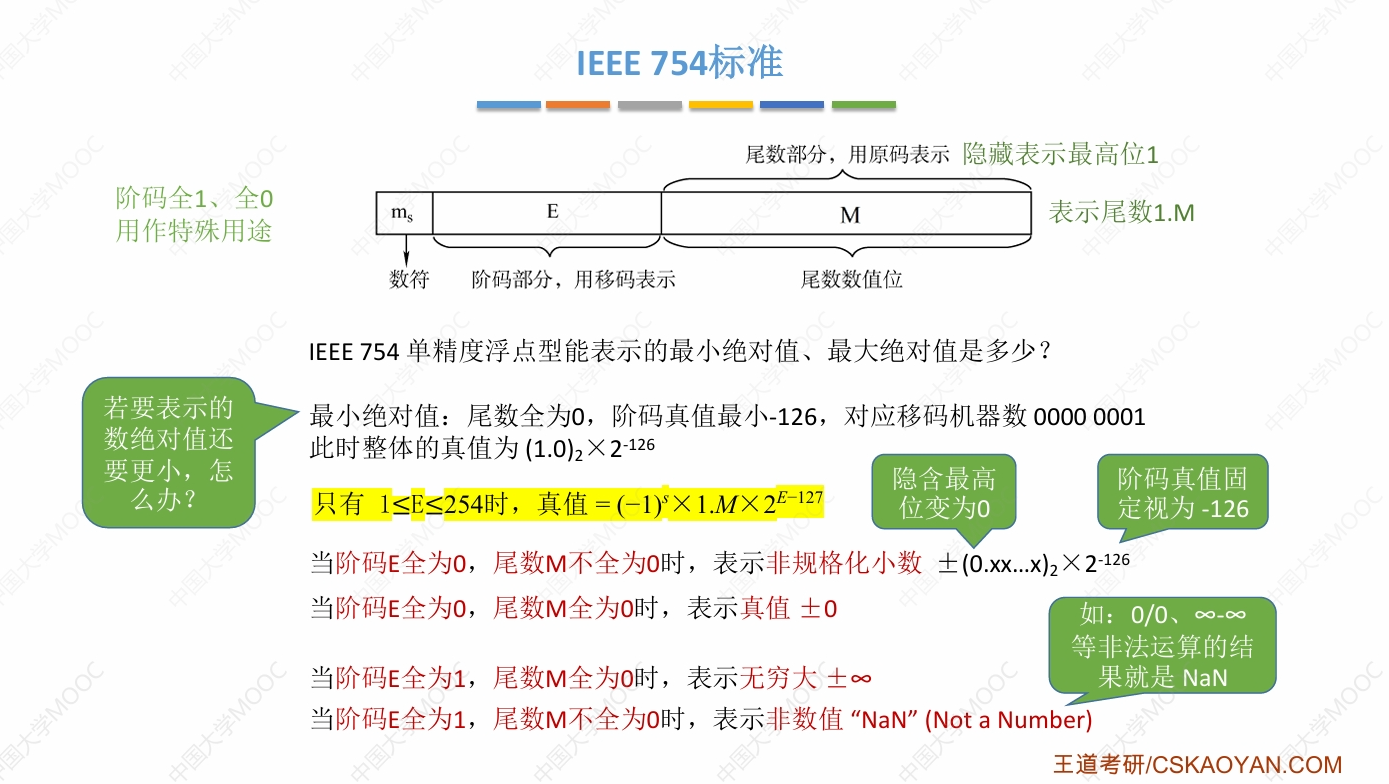

- 基数(隐含) :阶码的底,常为2,4,16等

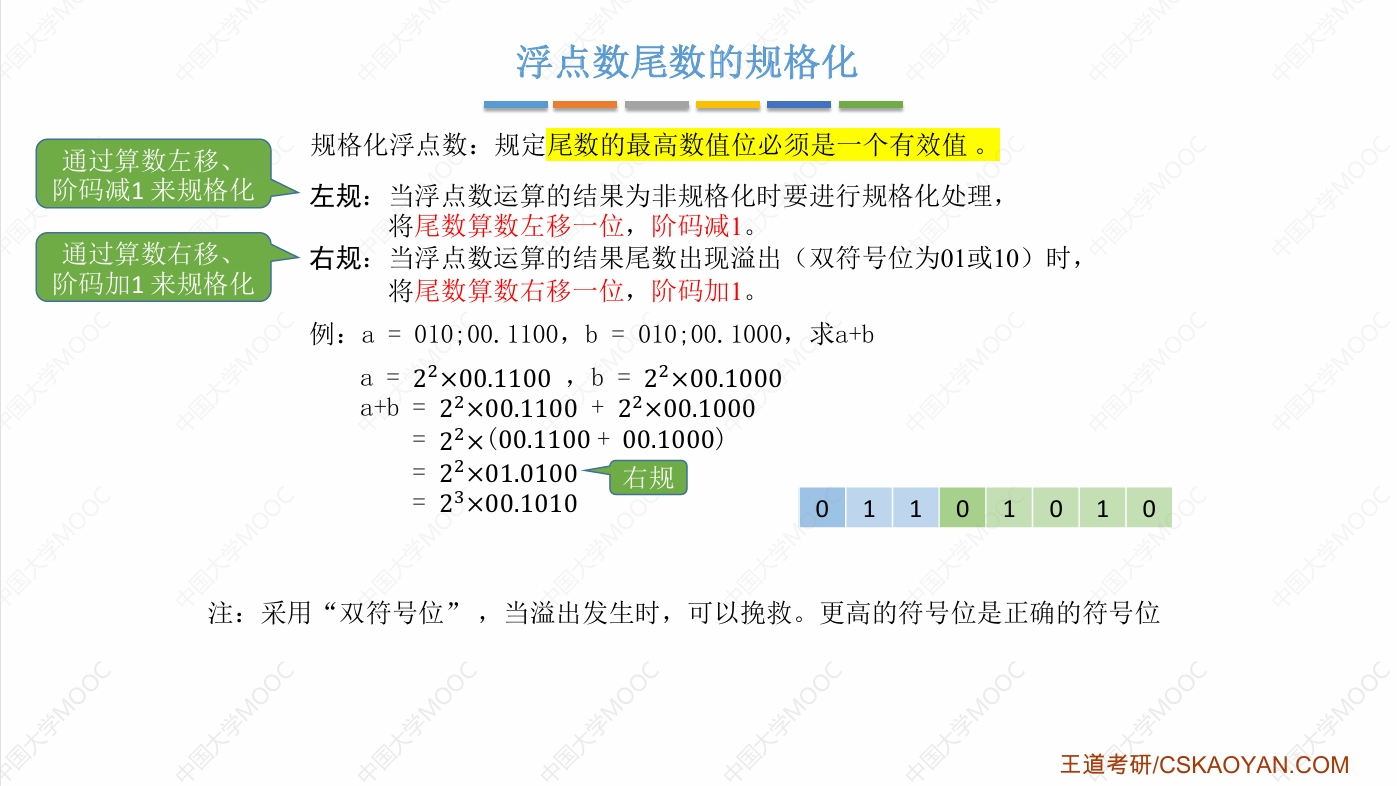

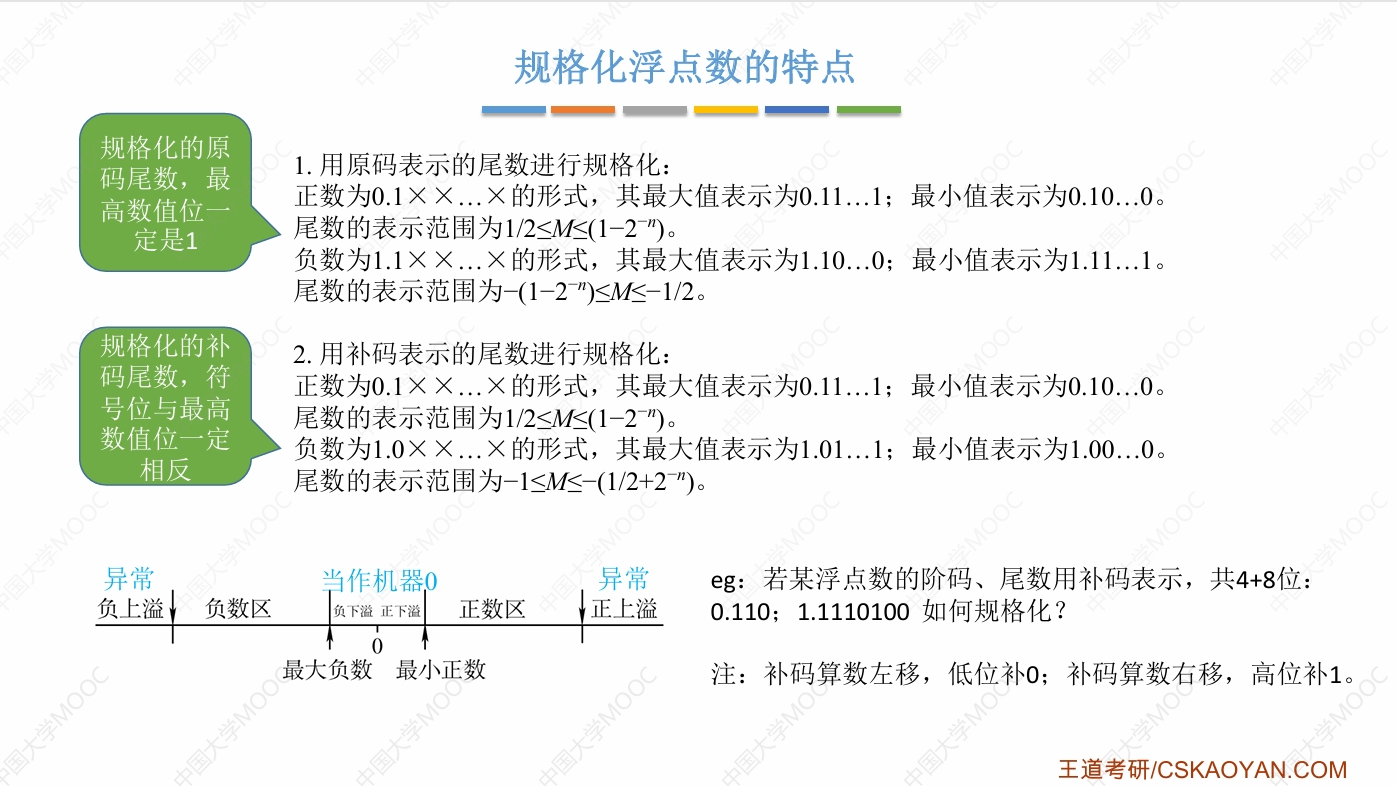

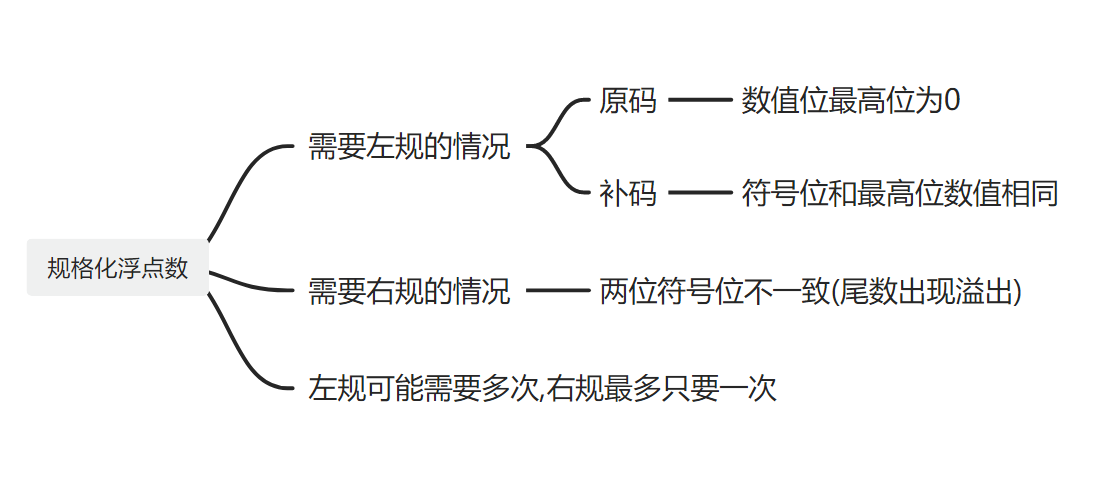

- 浮点数的规格化主要是为了增加数据的表示精度

- 移码的表示范围为1-127(全0全1另作他用)

- 十进制小数->IEEE数,先化成二进制数再移位

- 一个数值能否用IEEE格式精确表示 : 把他转换成分数,看分母是不是2的倍数

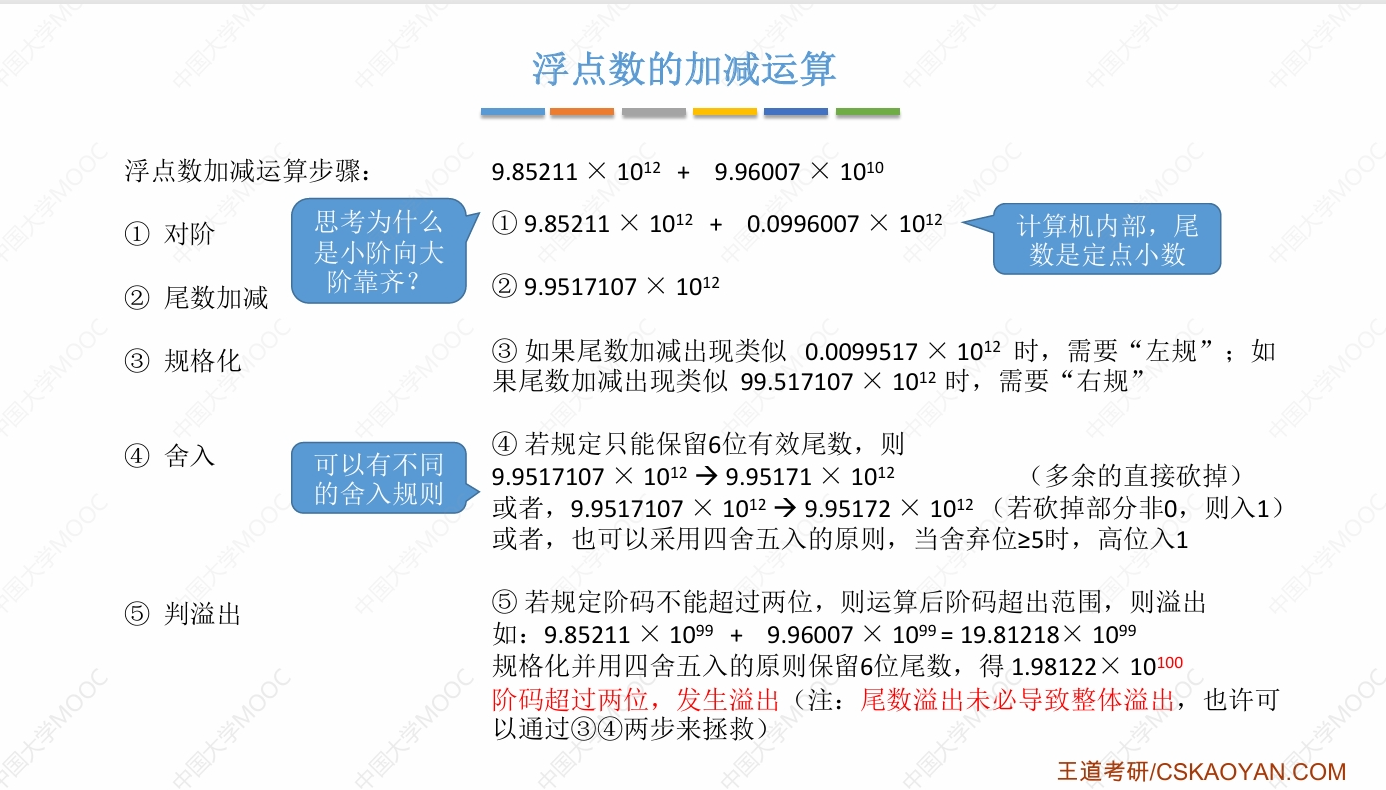

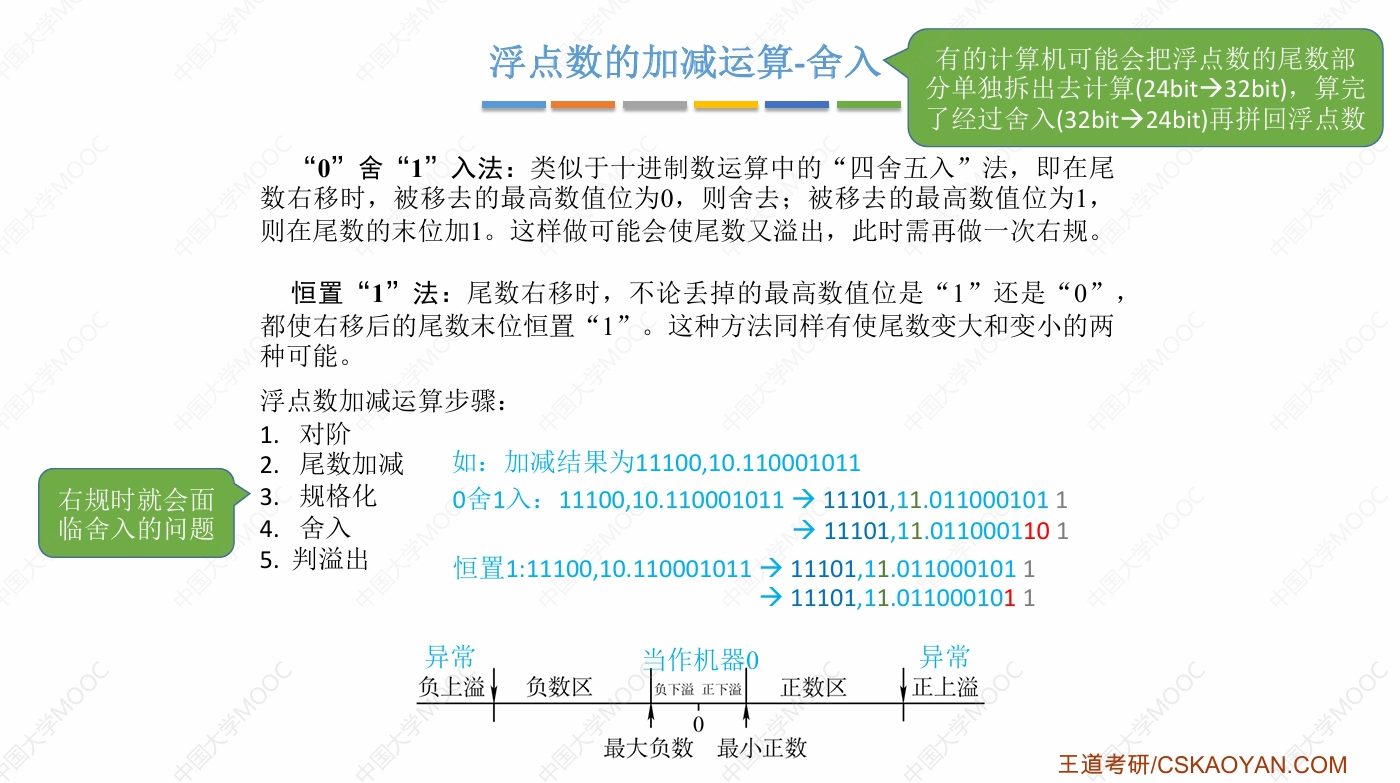

- 只有浮点数运算才有舍入

- 浮点数在对阶和右规时需要考虑舍入

- 浮点数的上溢 : 运算结果的绝对值大于机器所能表示的最大绝对值

- 浮点数的下溢 : 运算结果的绝对值小于机器所能表示的最小绝对值

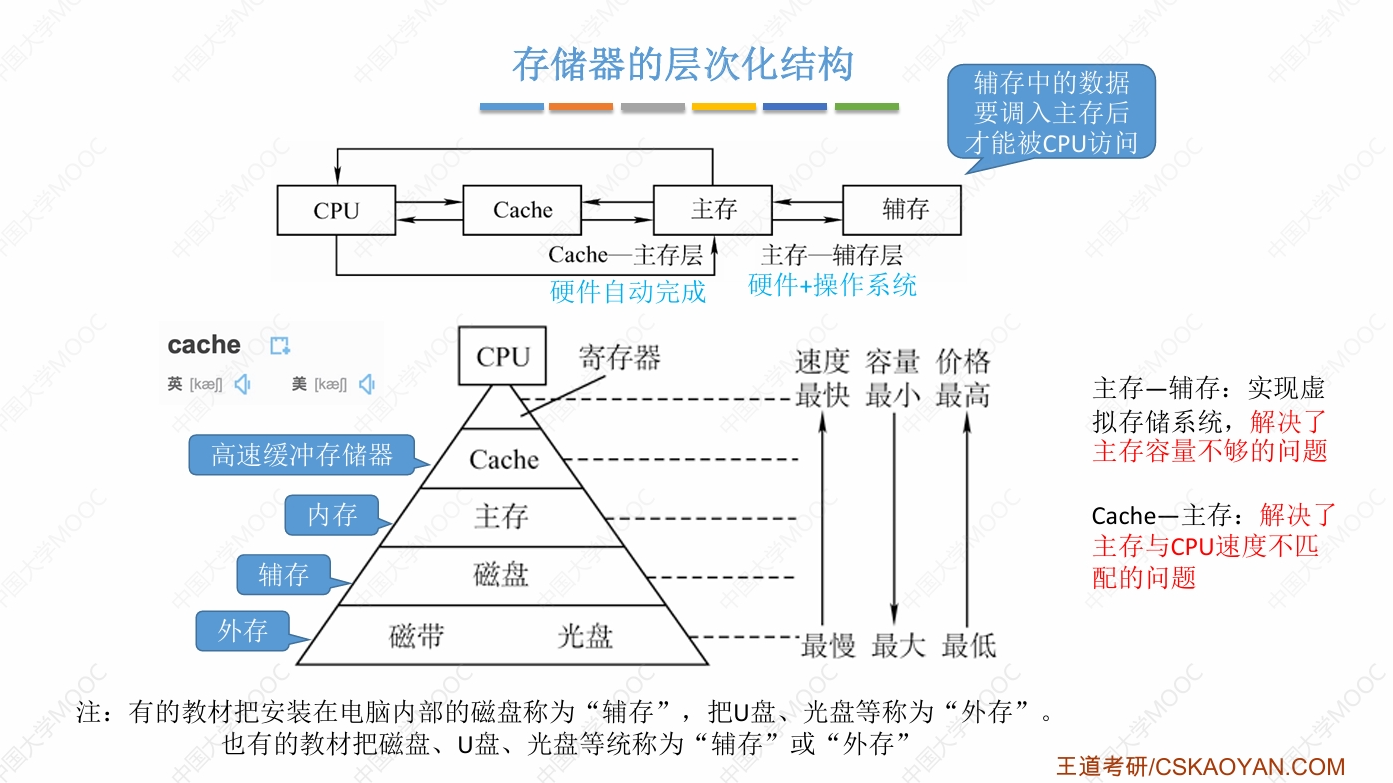

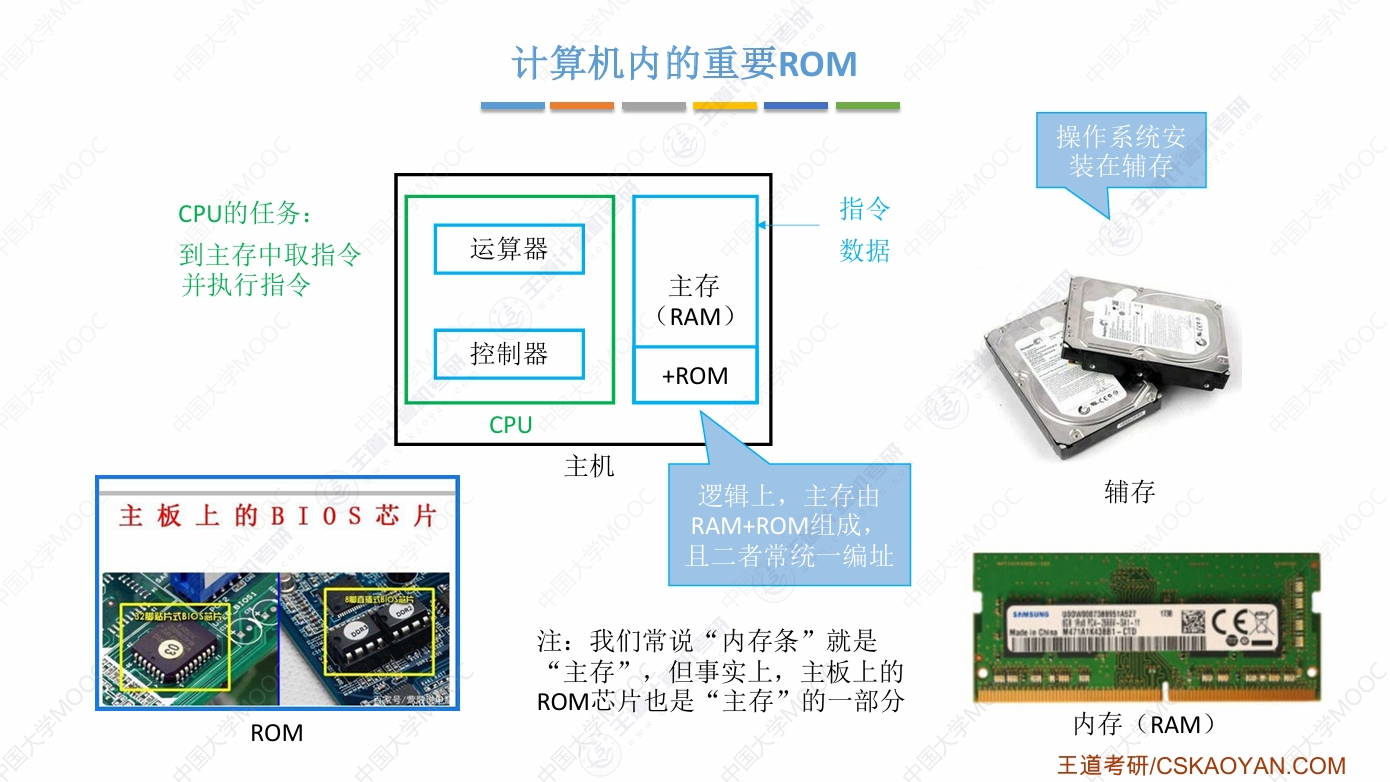

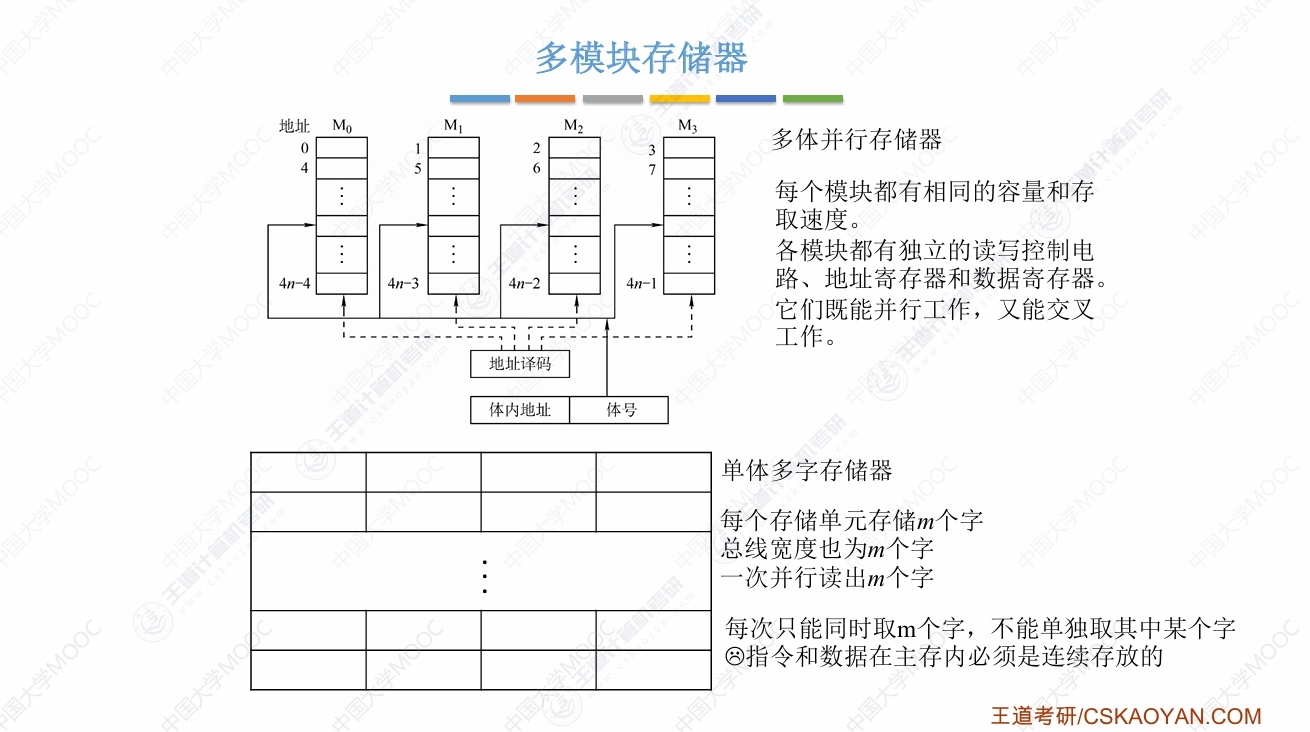

三丶存储系统

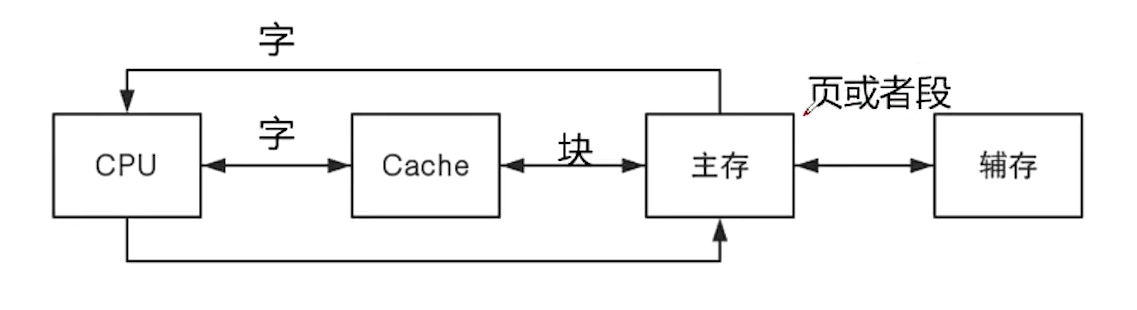

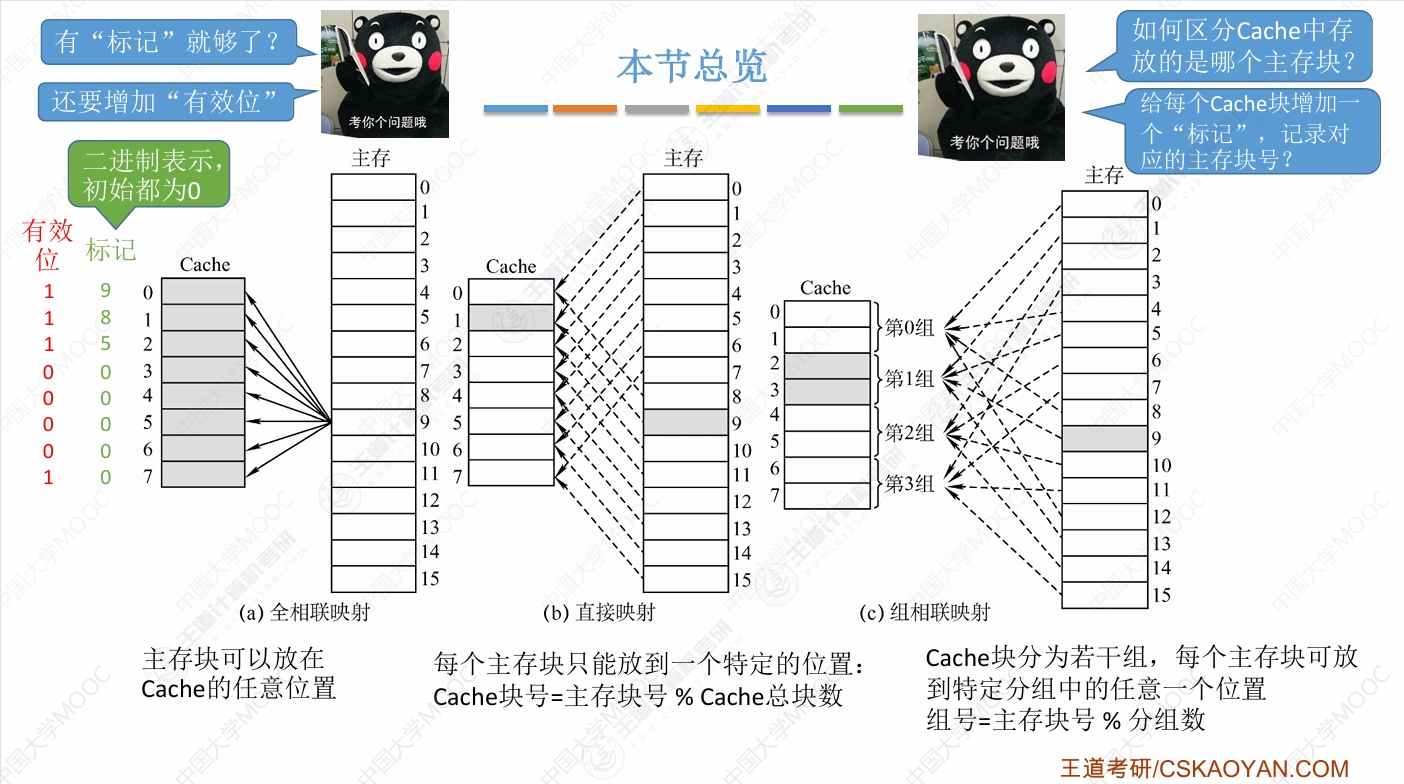

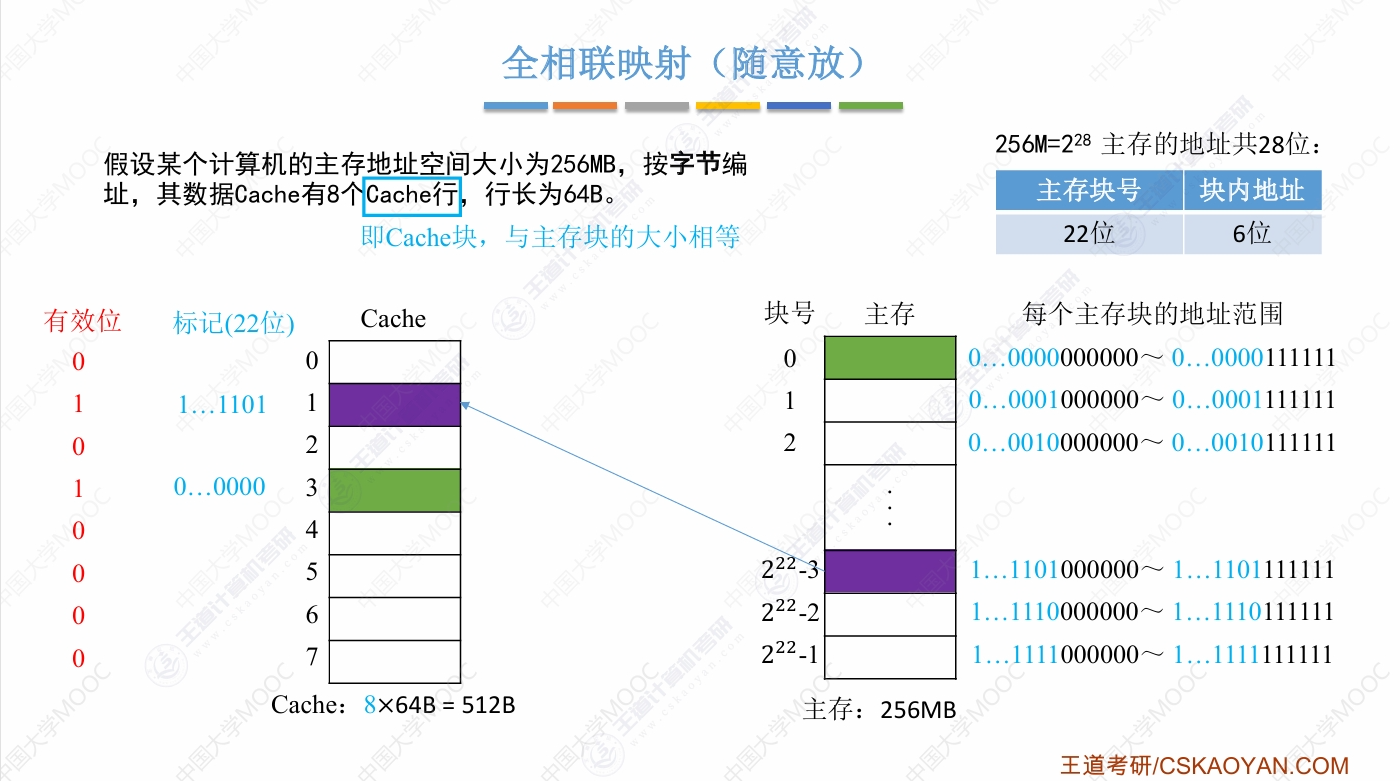

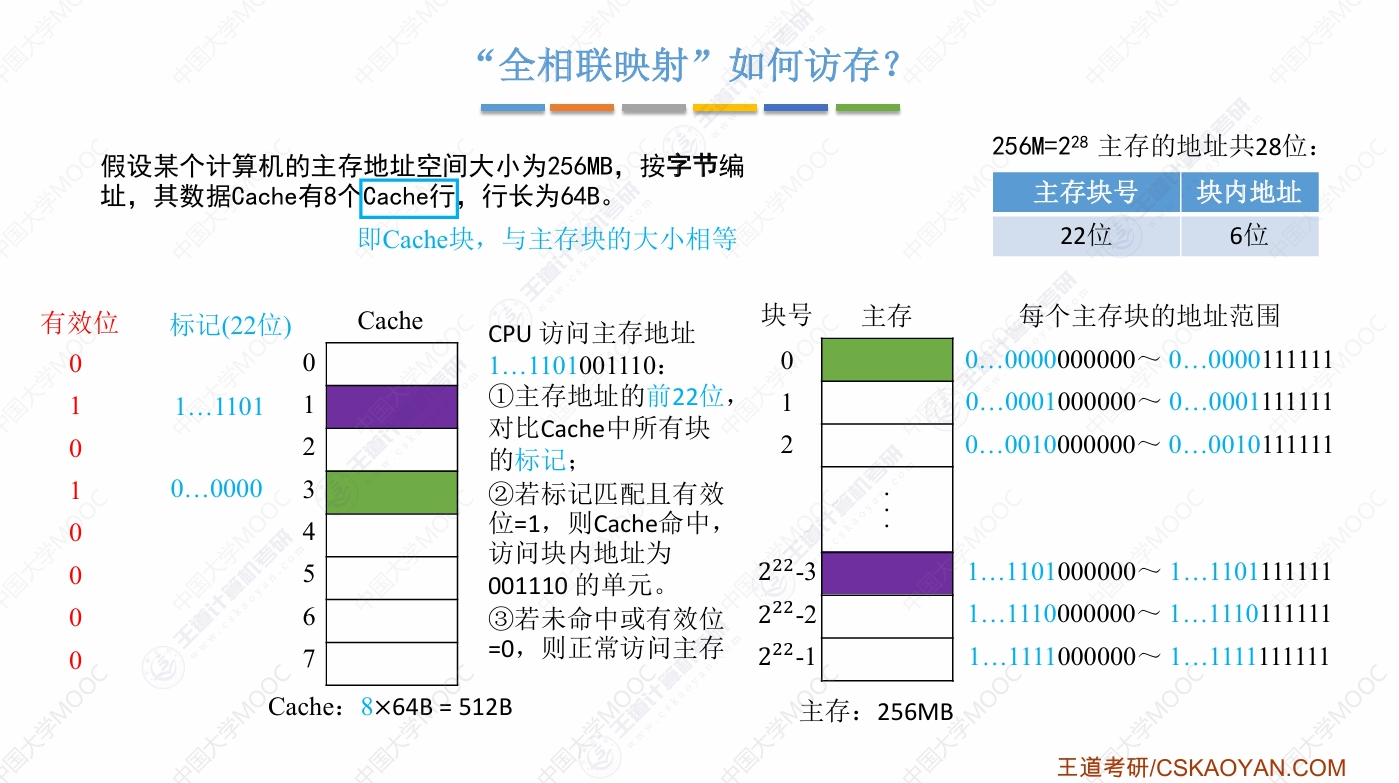

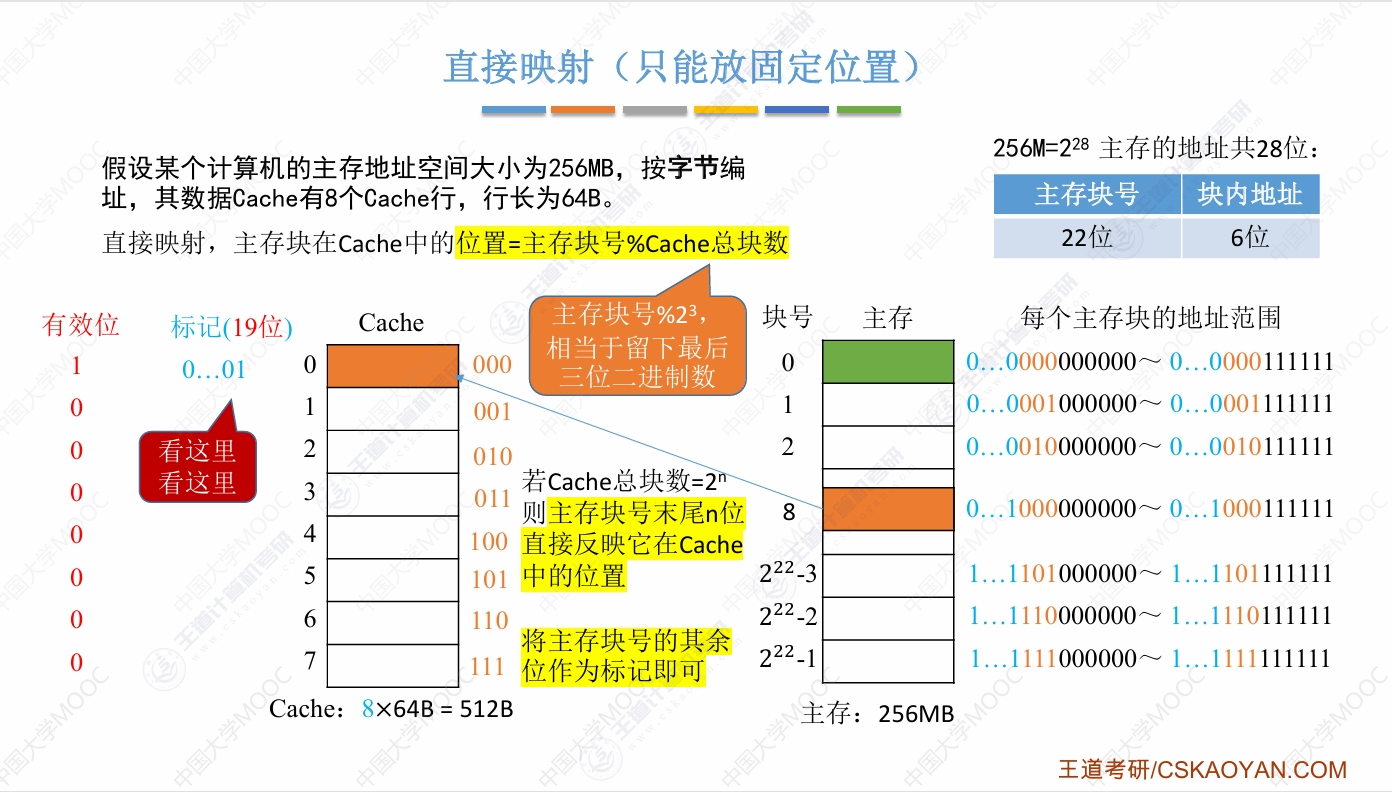

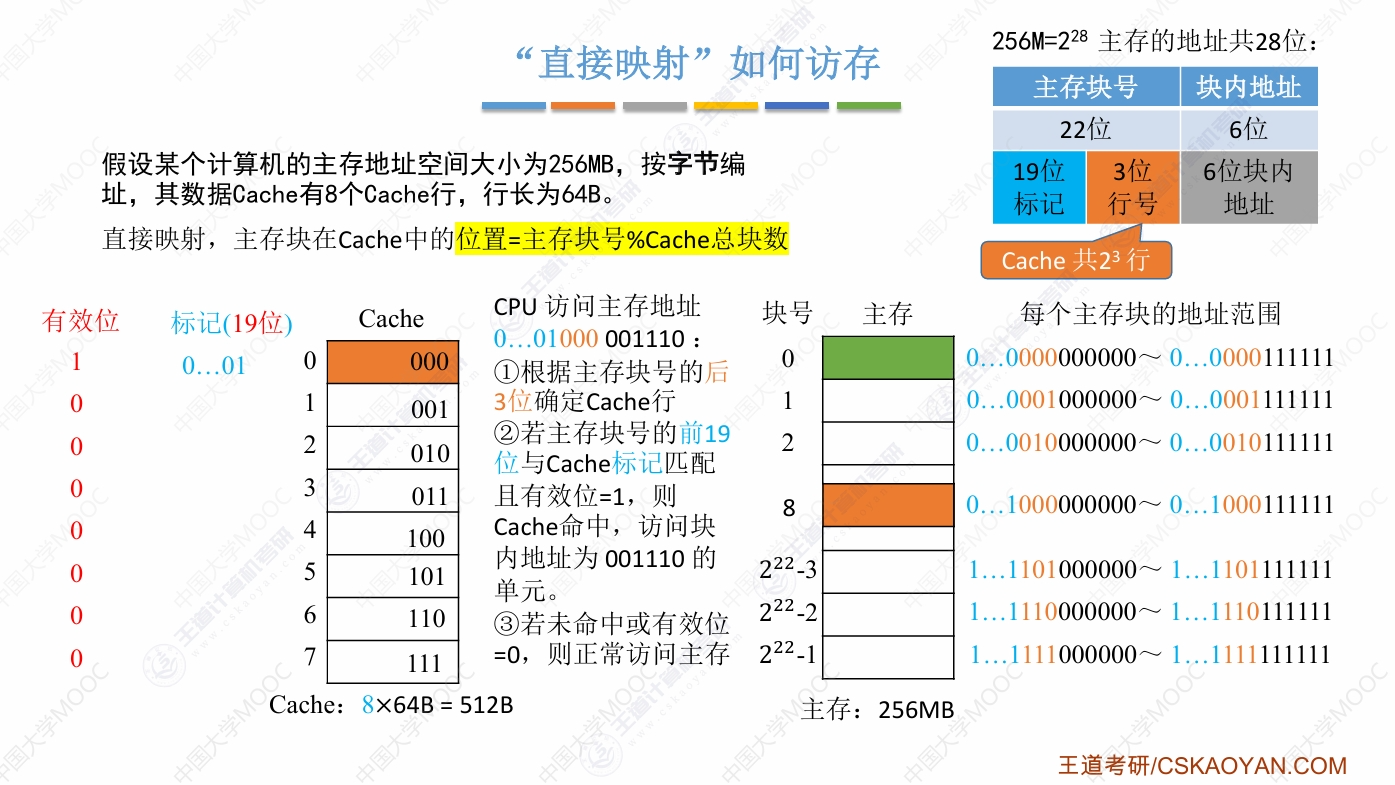

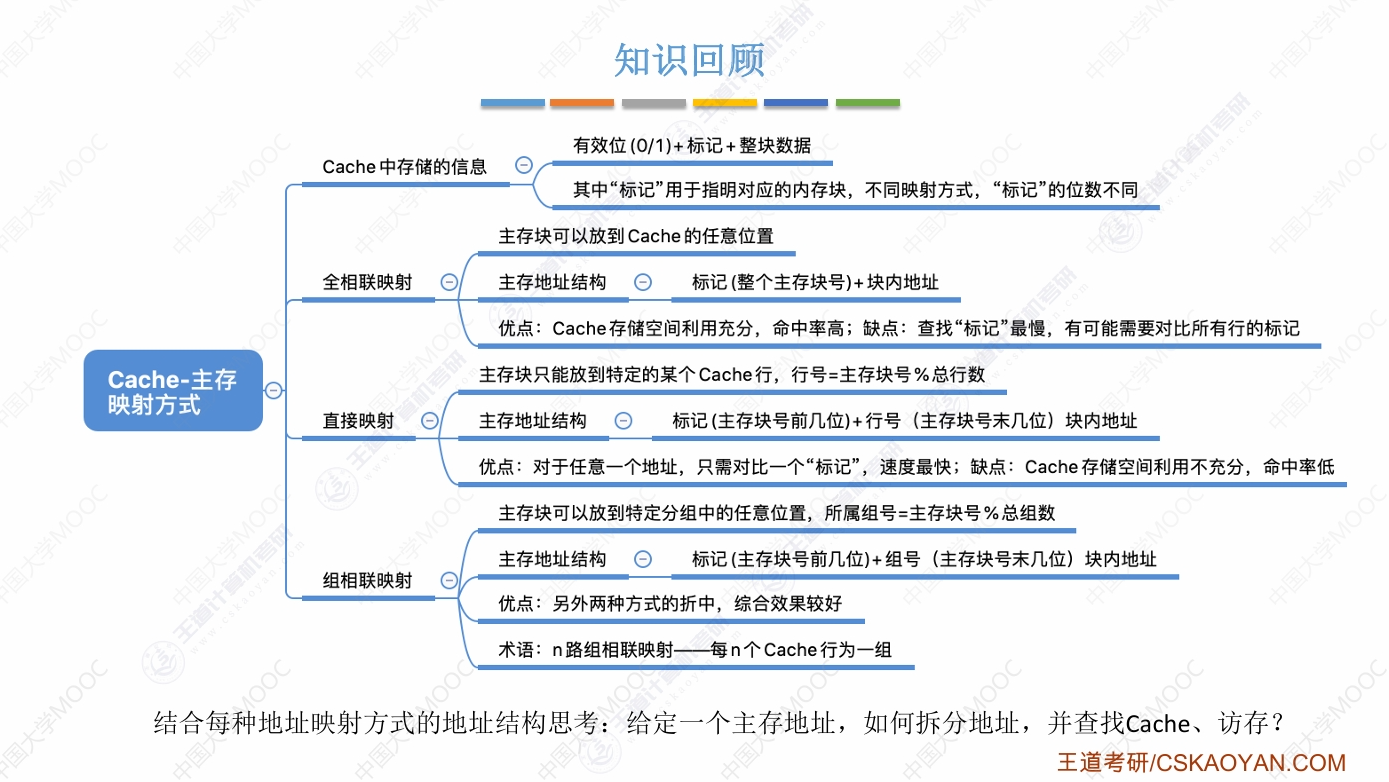

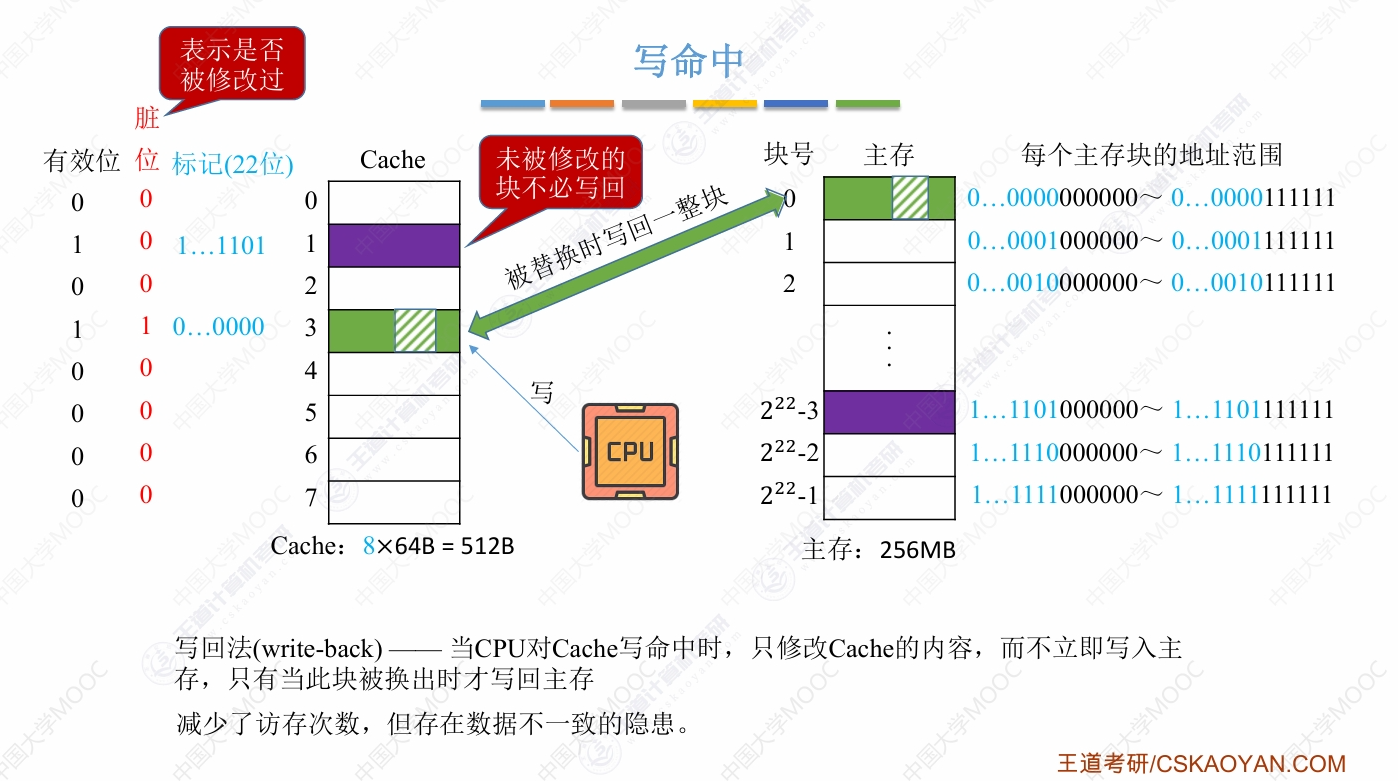

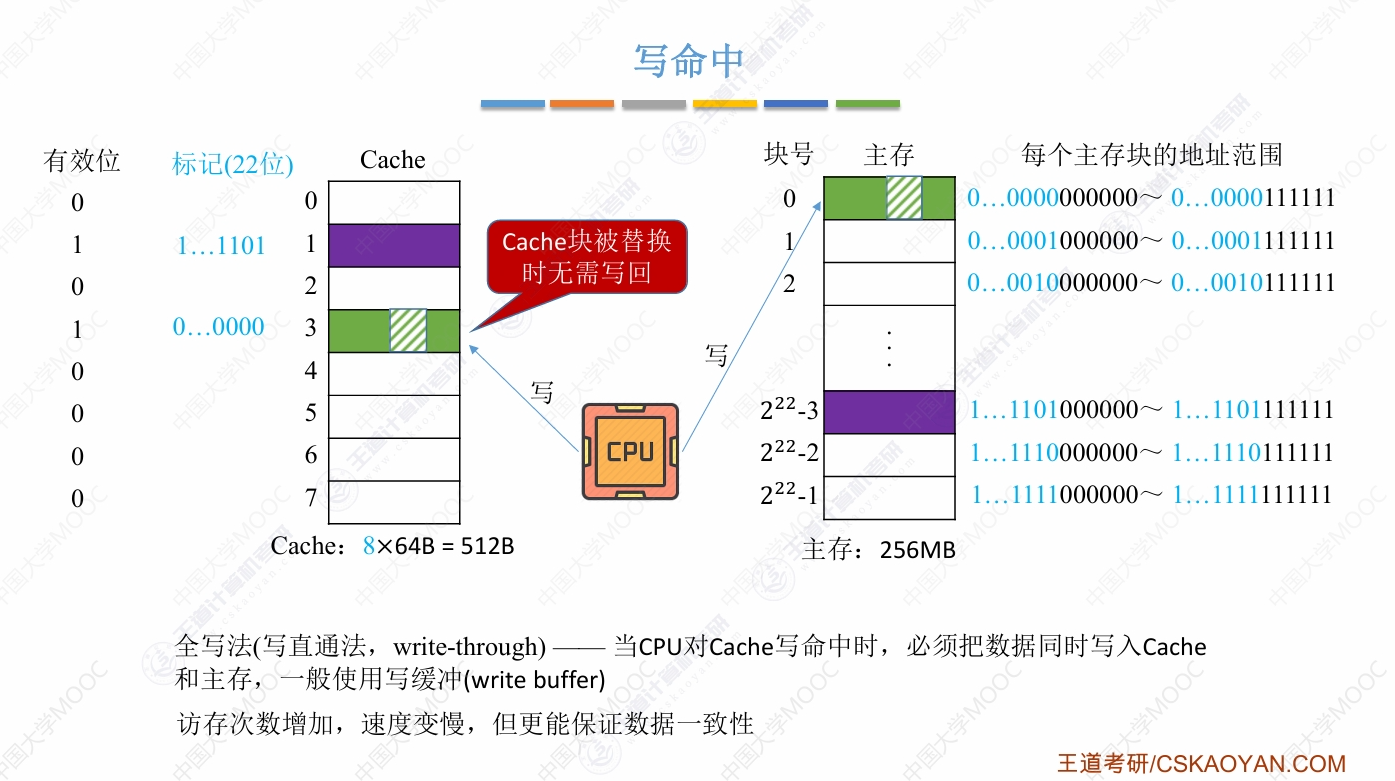

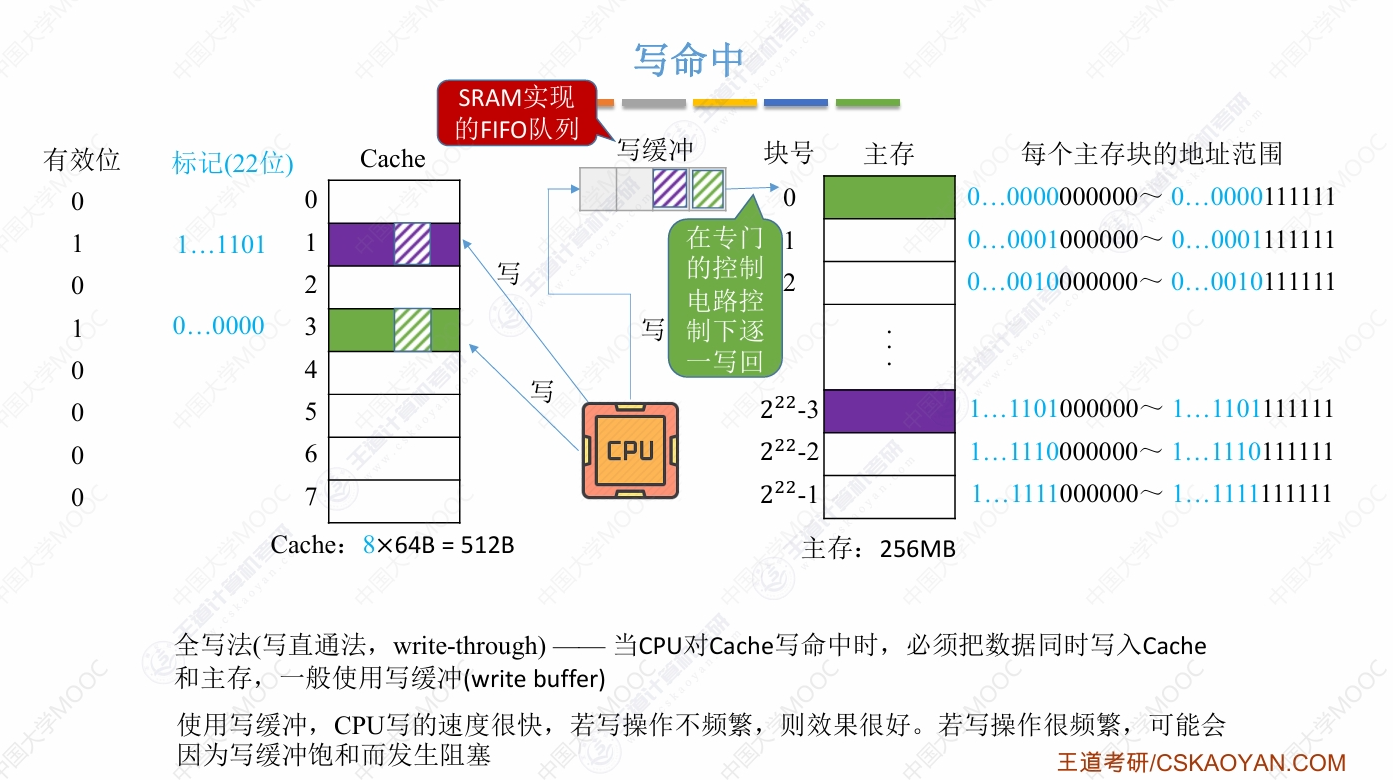

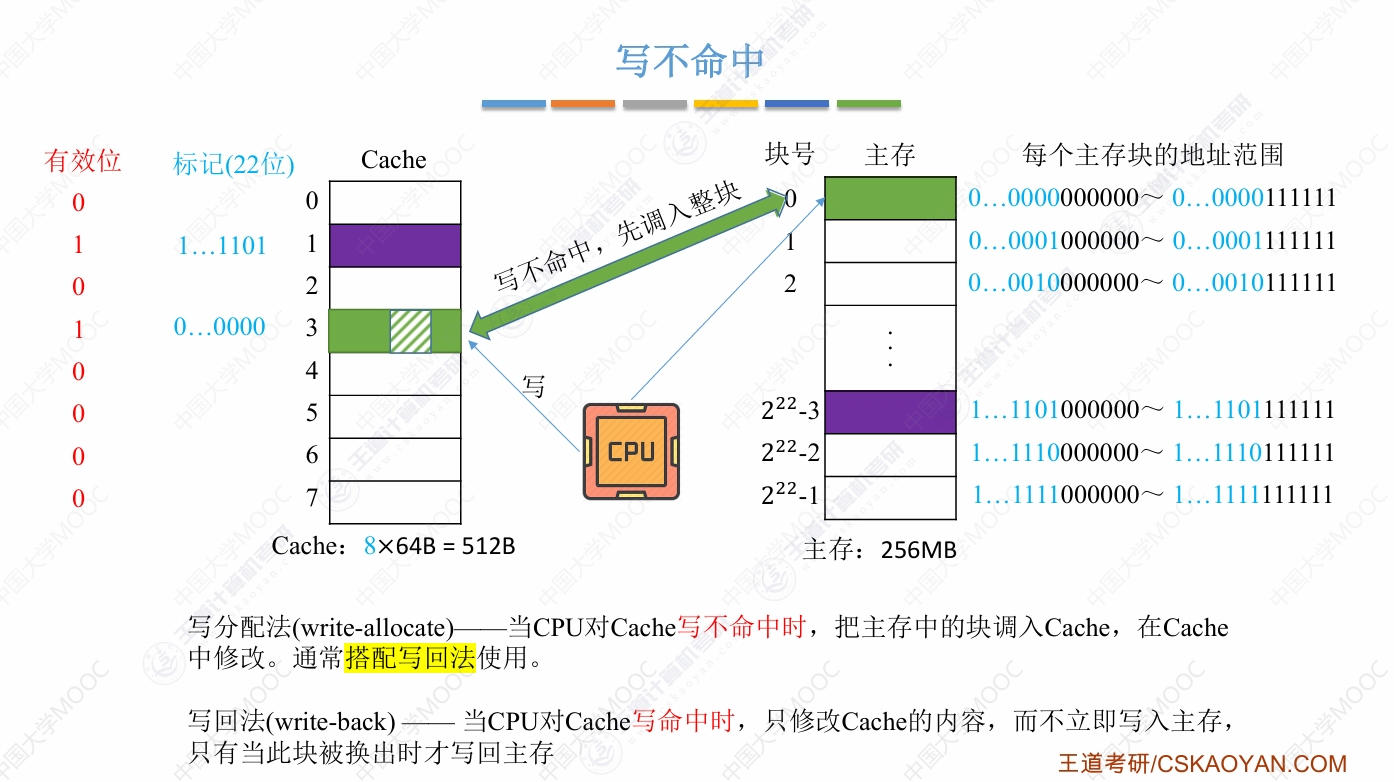

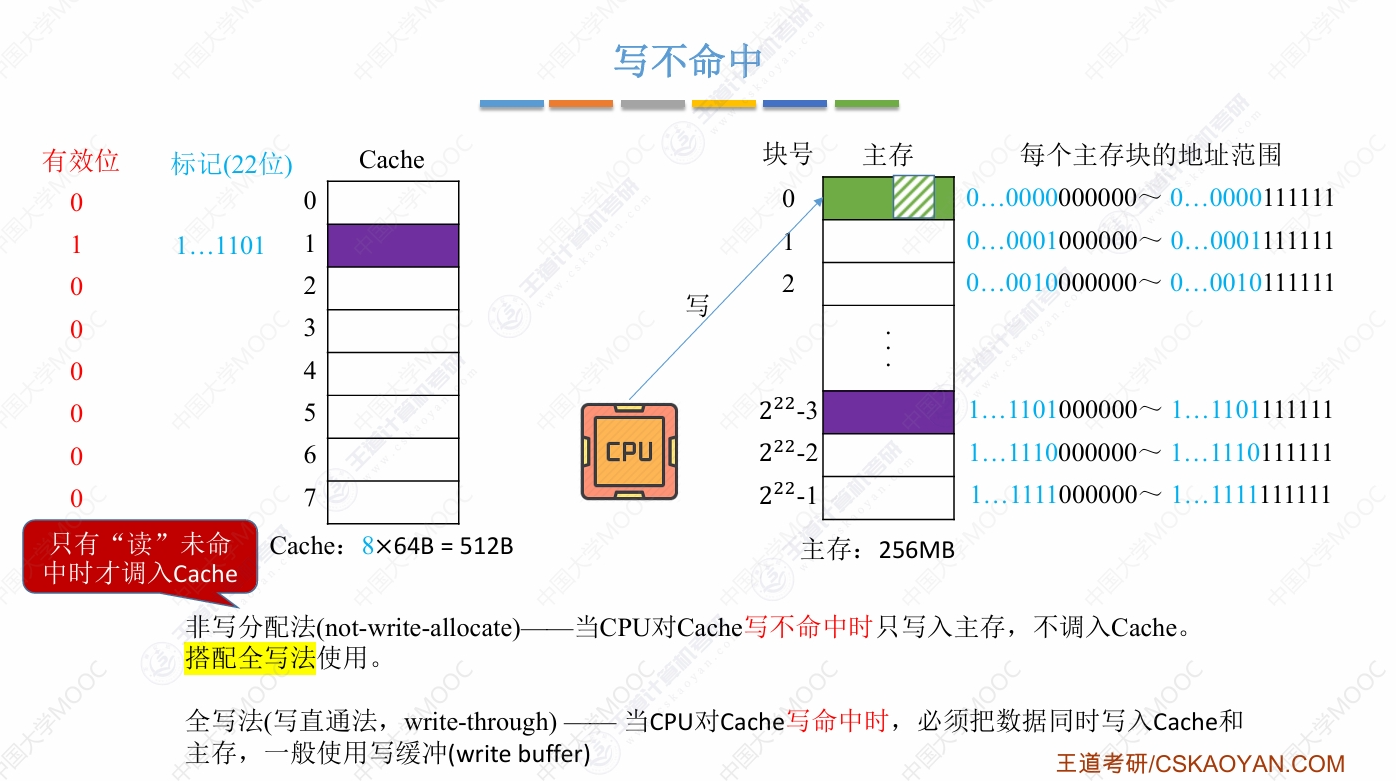

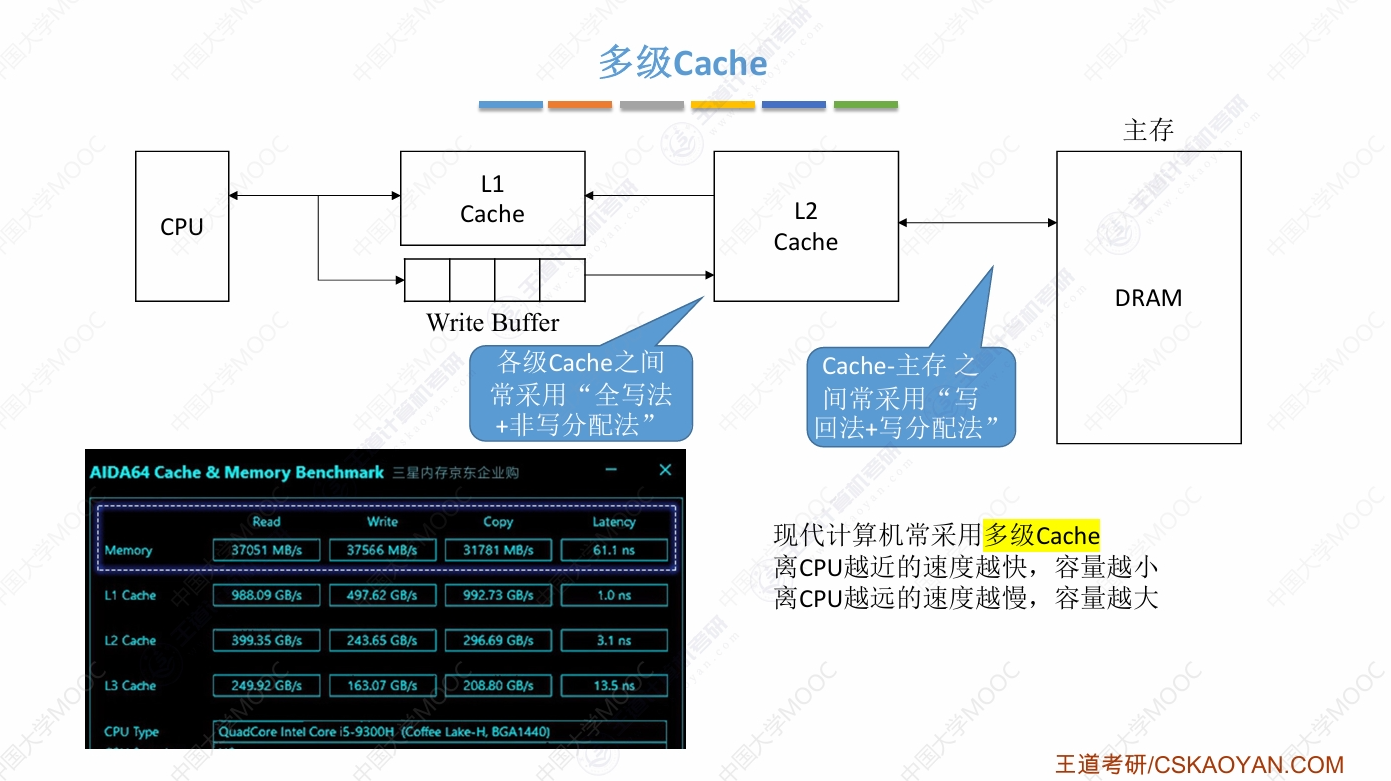

- 命中率 : CPU从Cache中获得信息的概率(CPU可以同时从主存和Cache中获得信息),缺失率=1-命中率

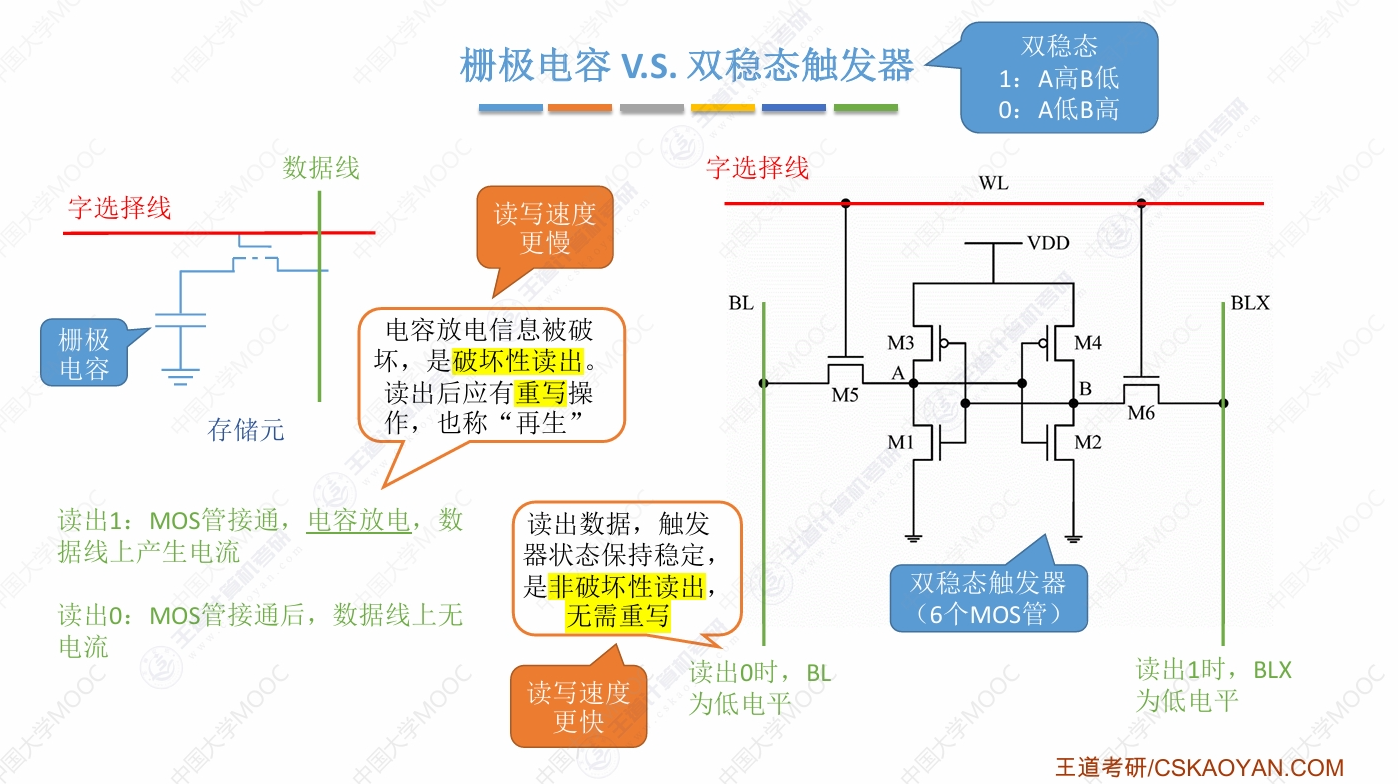

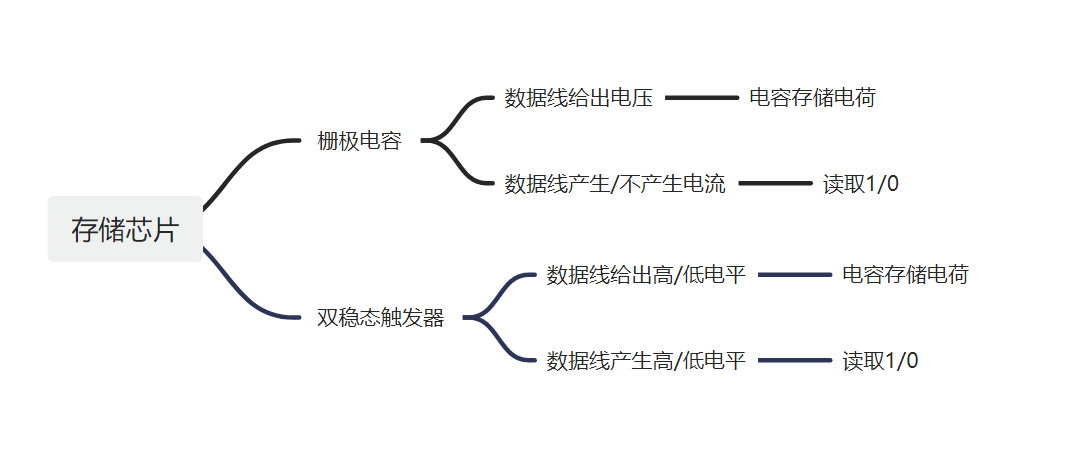

- 写入1 : 在导线的一端接上电压,给MOS管的一端加上高电平信号,MOS管就可以接通,电容下接地线(为0v),当上方有电压时,电容就会保存一定的电荷

- 读取1/0 : 给MOS管的一端加上高电平信号,MOS管就可以接通,此时若电容内有电荷,导线的另一端就会检测到电流,即输出了1,反之则输出了0

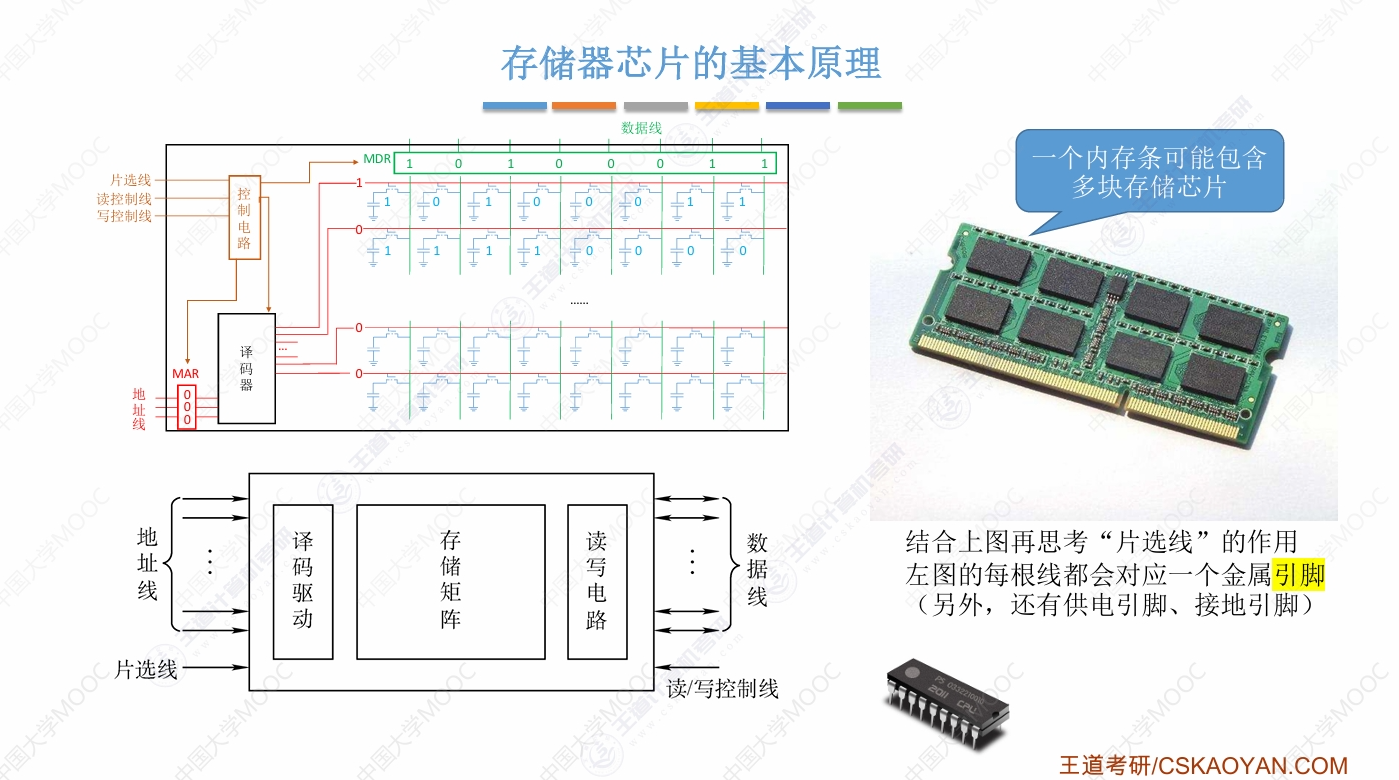

- 一个地址对应一条字选线

- CPU通过地址总线发送地址,通过数据总线接收数据

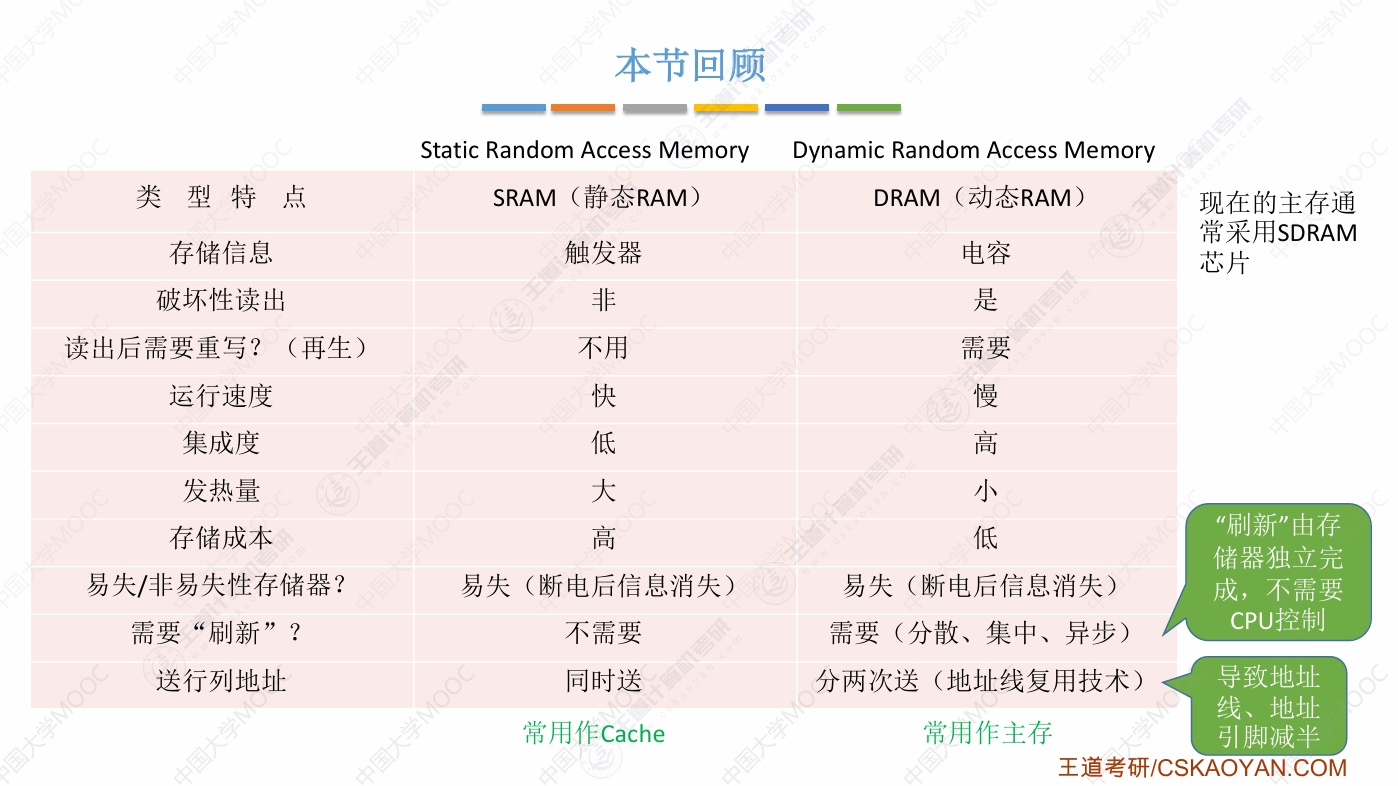

- DRAM和SRAM芯片的核心区别 : 存储元不一样

- DRAM芯片使用栅极电容存储信息,SRAM芯片使用双稳态触发器存储信息

- 数据线=数据位数,地址线=地址位数,片选线=1,读/写控制线=1/2

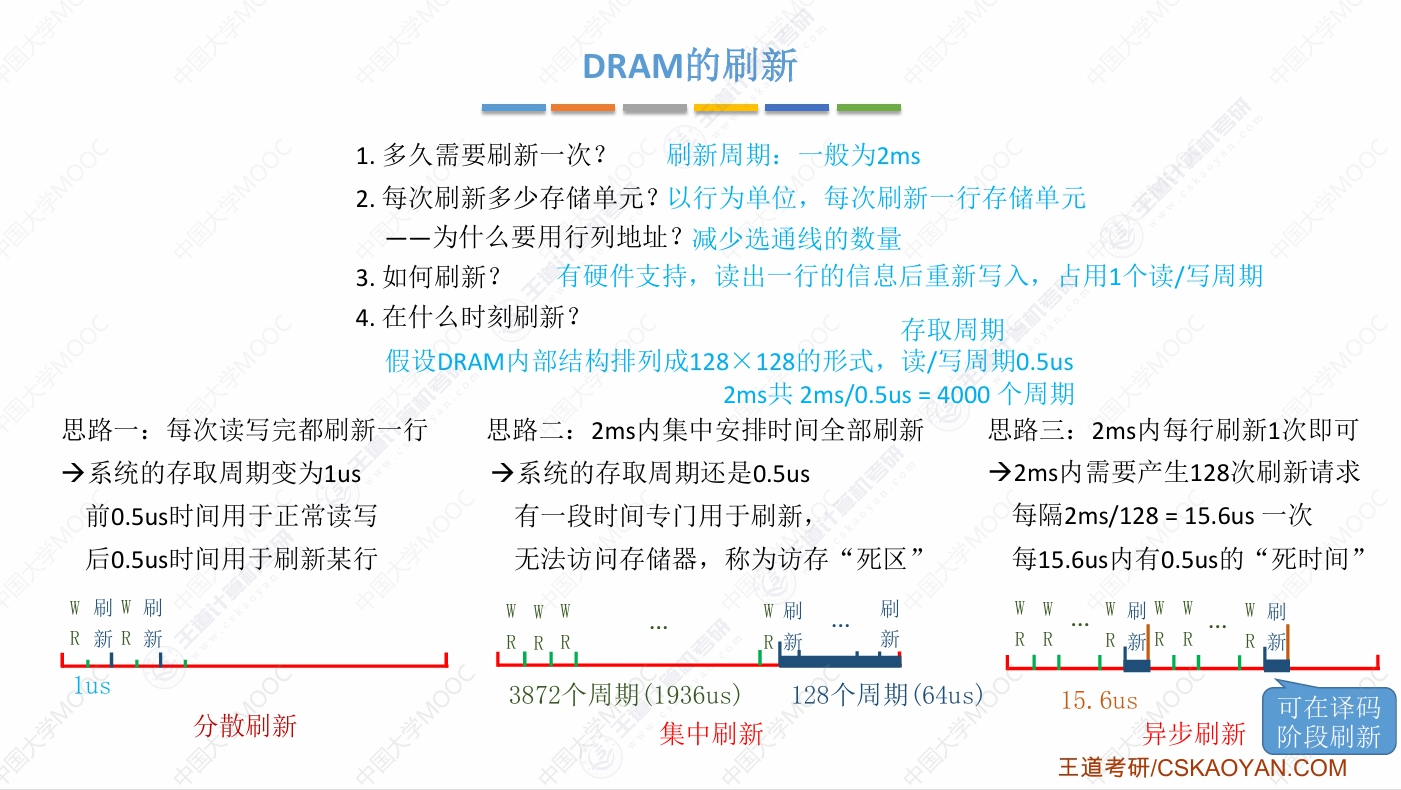

- 刷新 : 电容内的电荷会自己消失,而触发器只要不断电,状态就编号改变,所以DRAM需要刷新(给电容充电)

- 一次完整的刷新过程需要占用一个存储周期

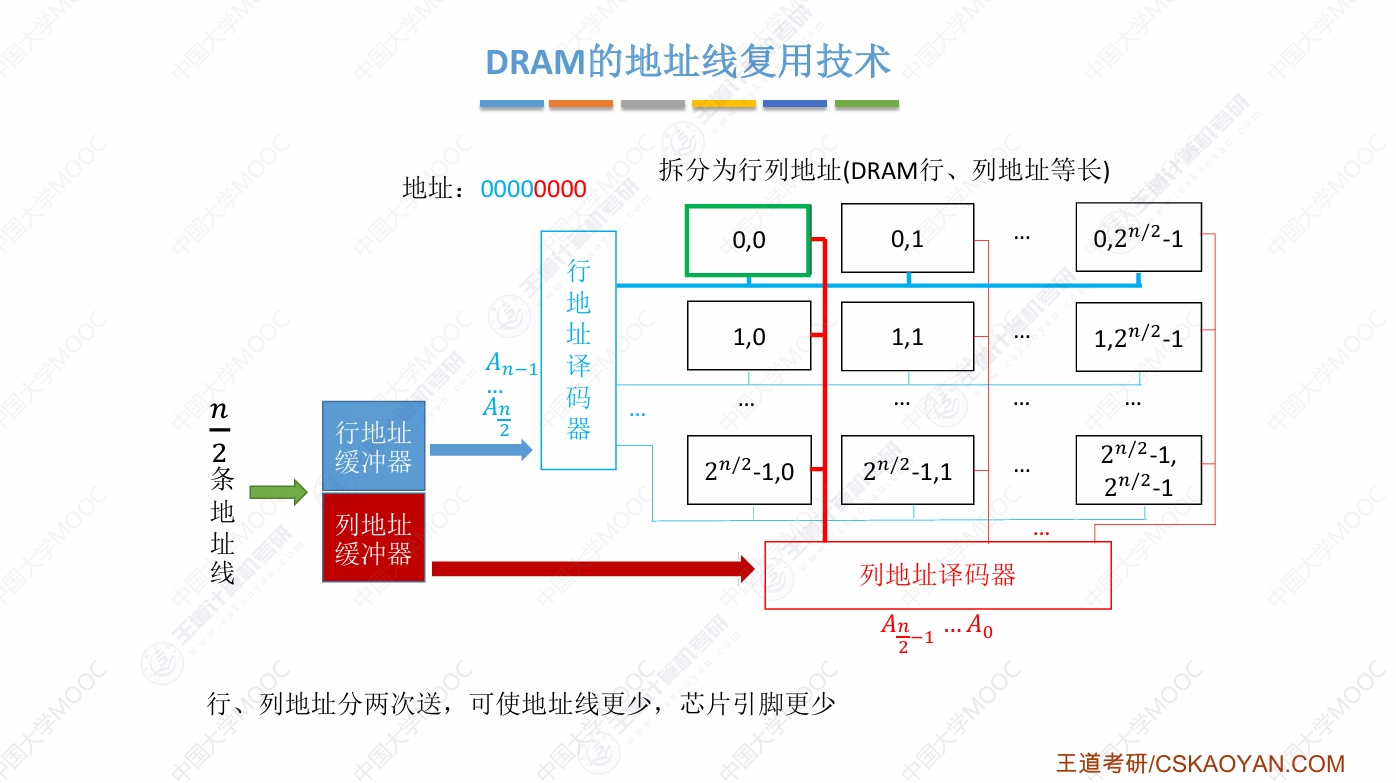

- 地址线复用技术 : 地址线是原来的一半,多了两条行列通选线(其中一条用片选线代替)

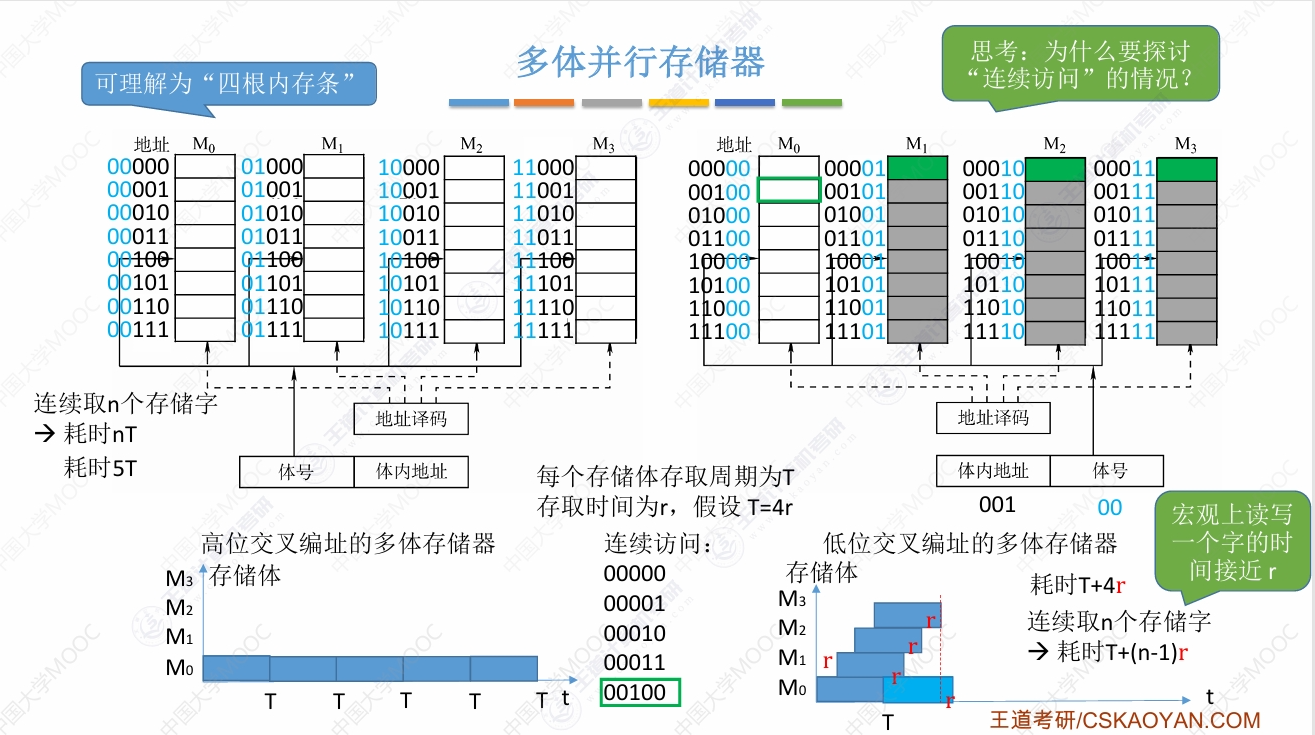

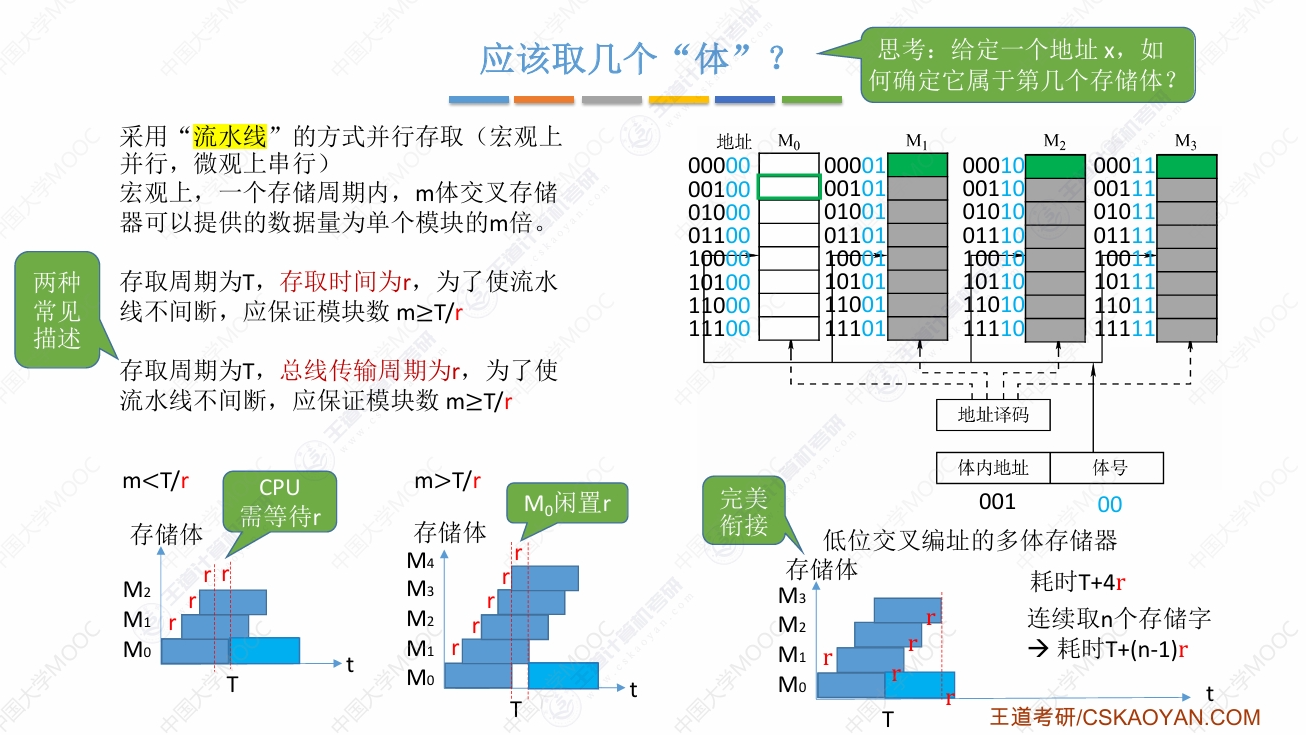

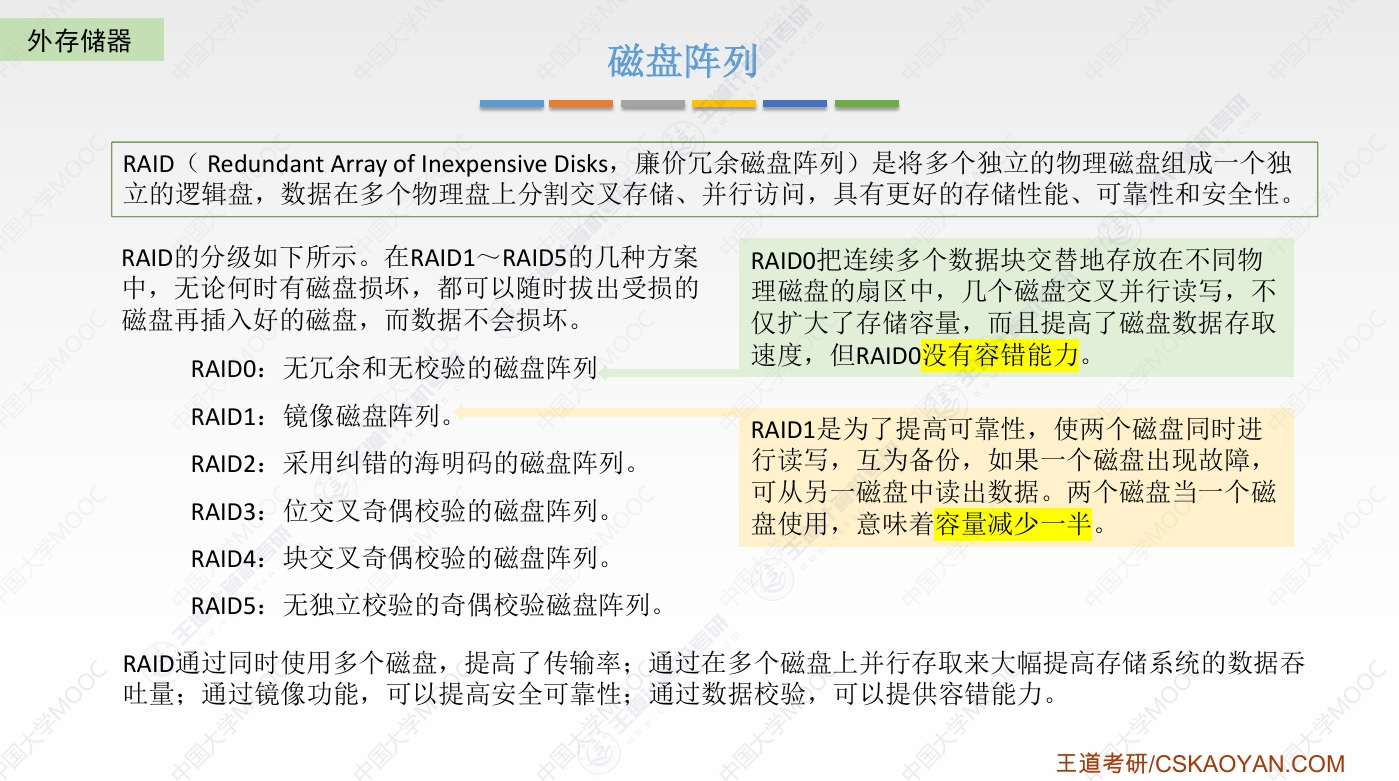

- 高位/低位交叉编址 : 存储元的体号从地址码的高位/低位取

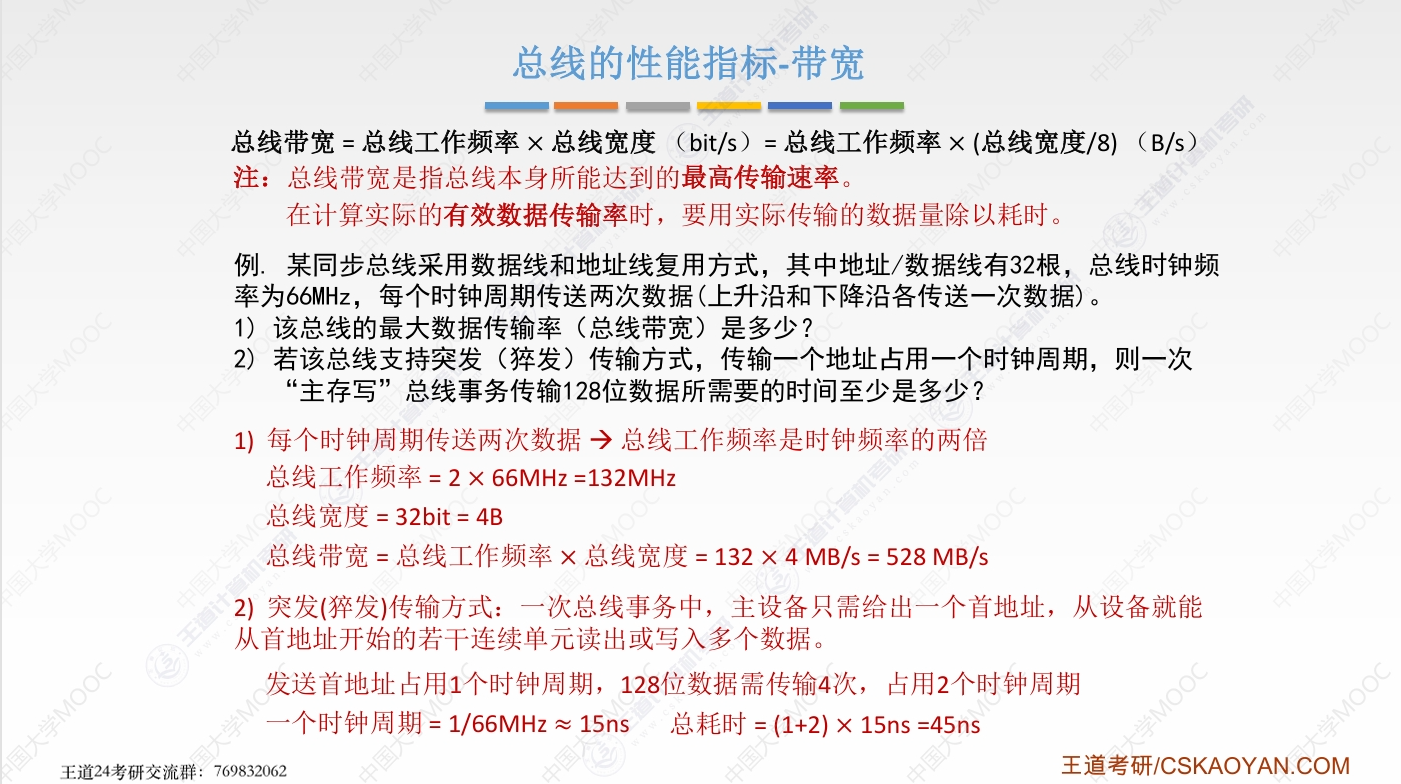

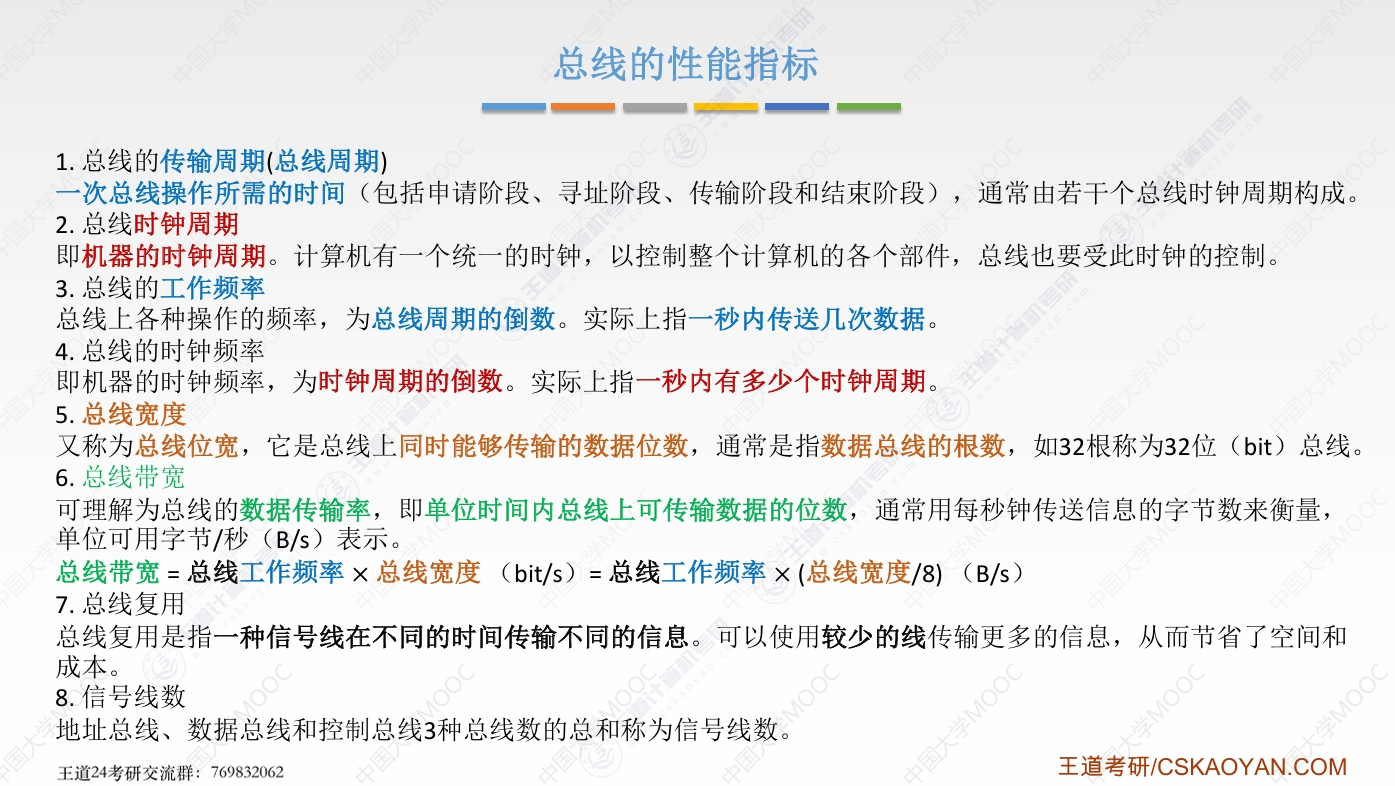

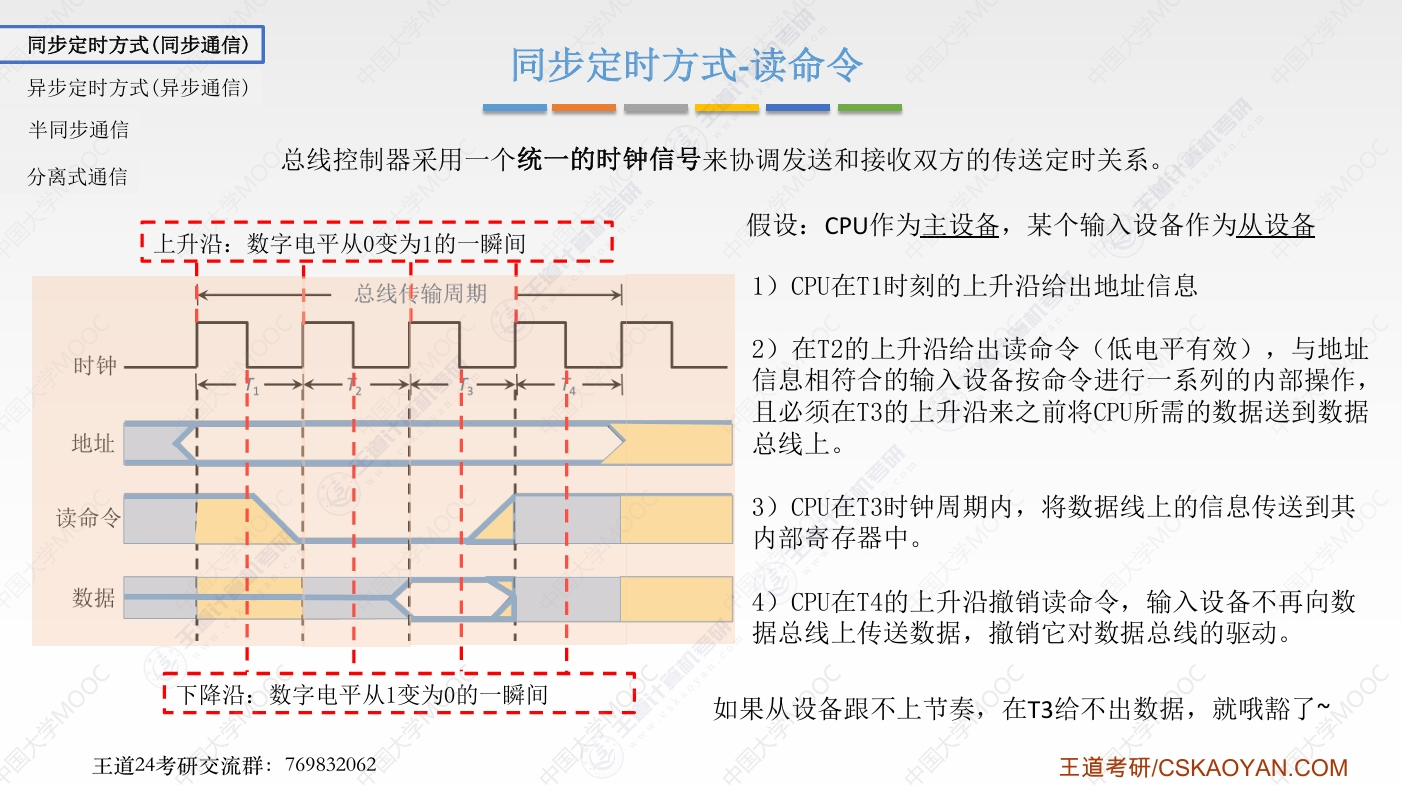

- 总线传输周期 : 通过数据总线把数据传输到CPU所用的时间

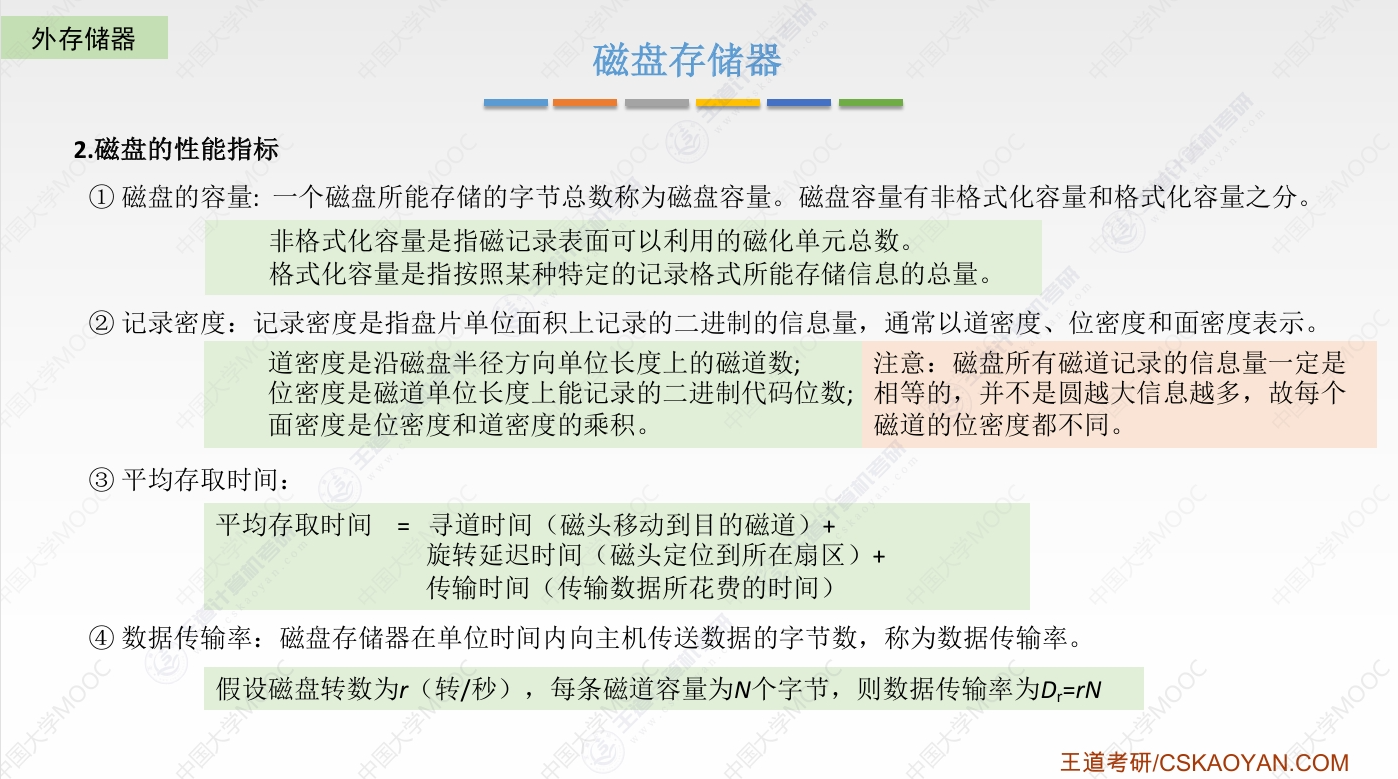

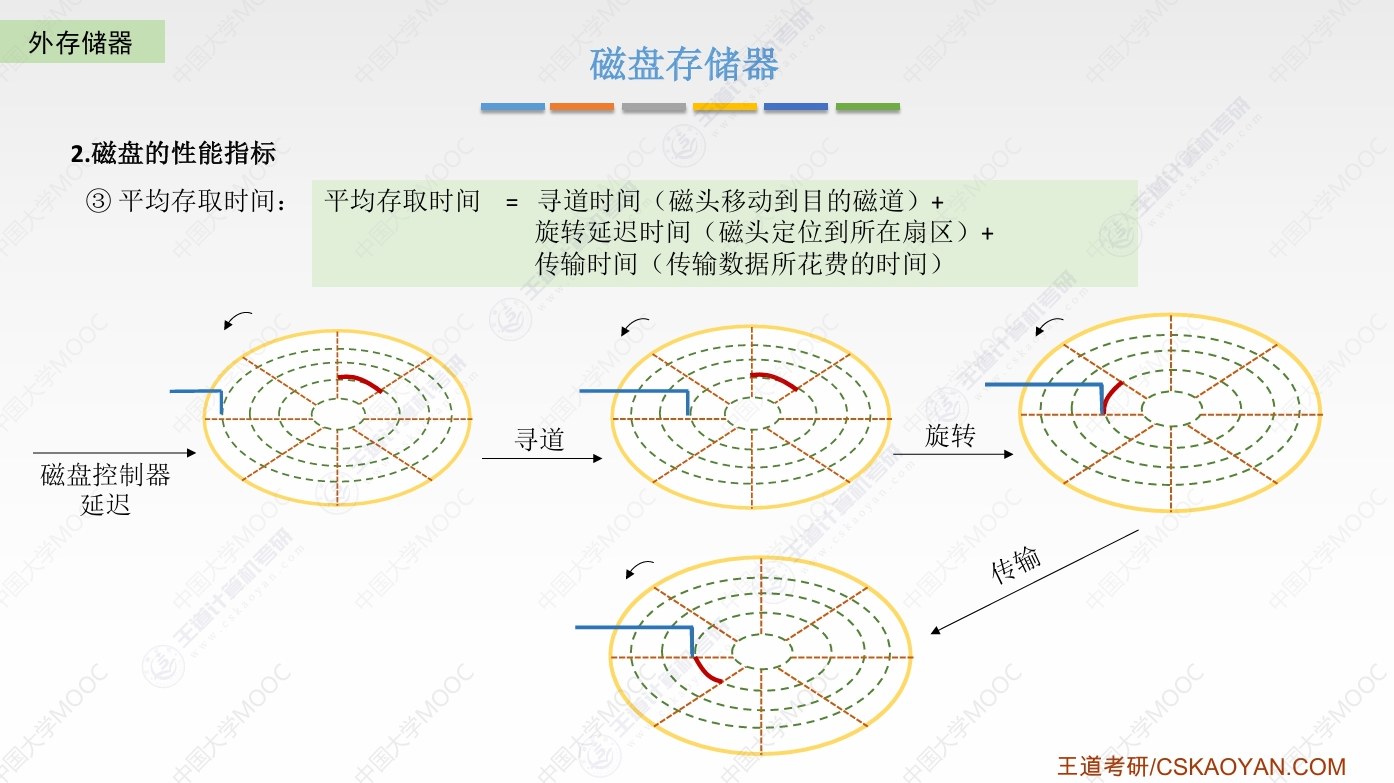

- 每个磁道存储的信息量一致(磁道长度x位密度)

- 旋转延迟时间默认取转半圈所需的时间

- 传输时间=磁头扫过一个扇区的时间

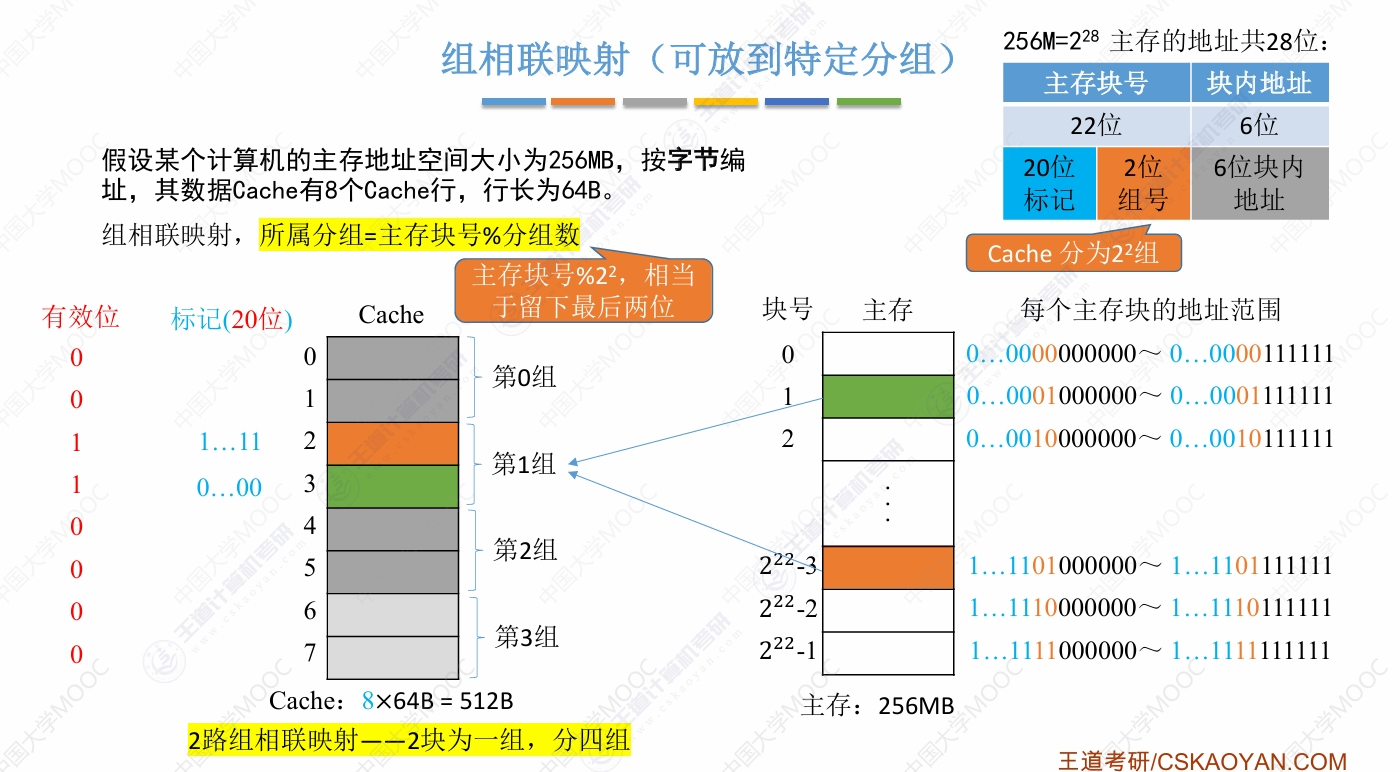

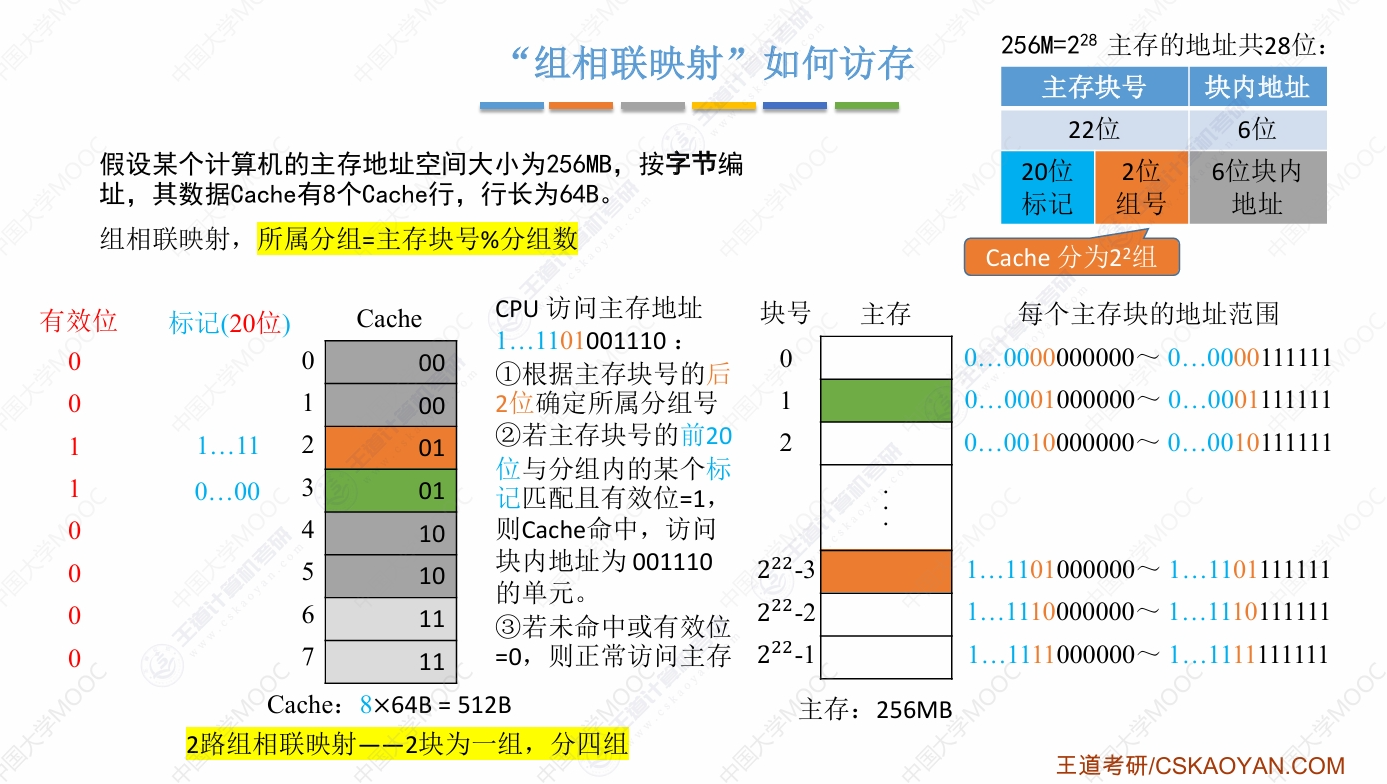

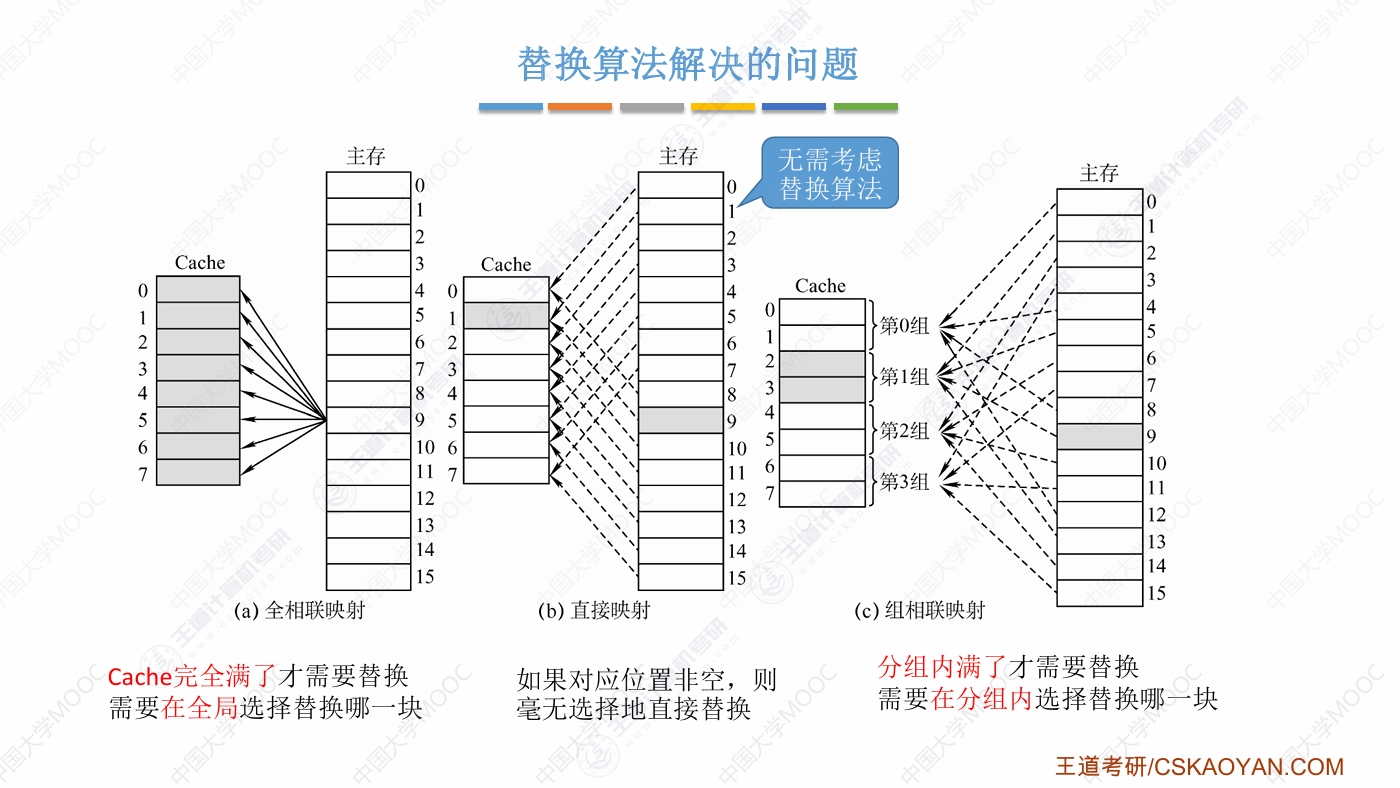

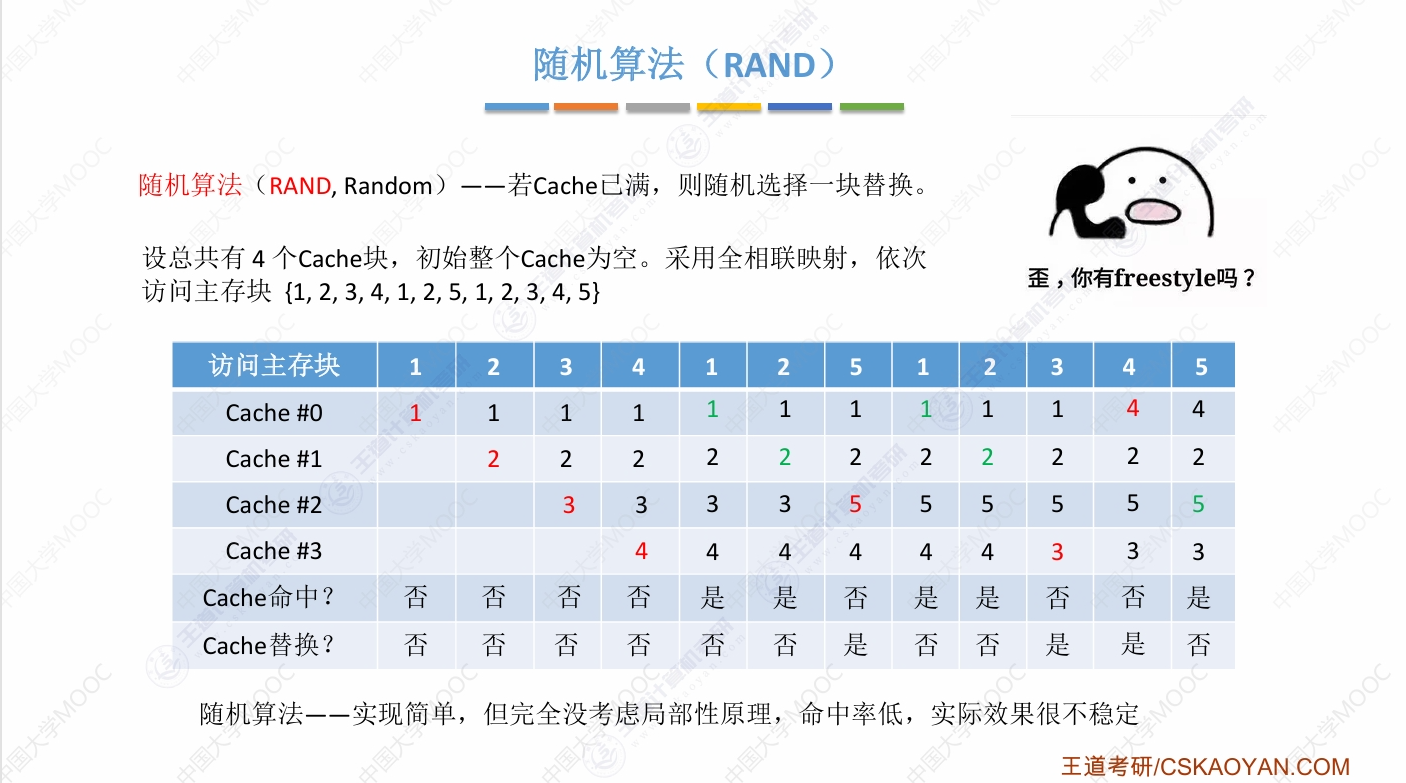

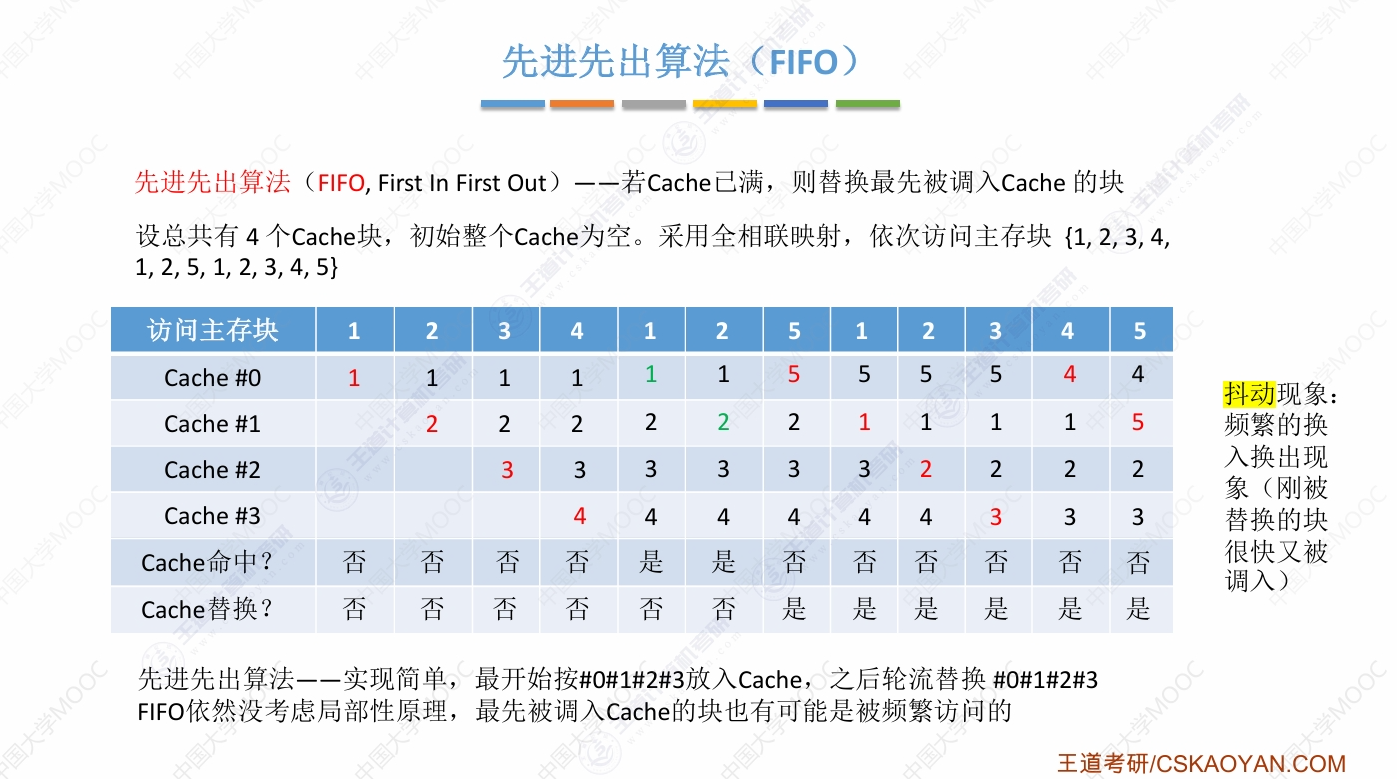

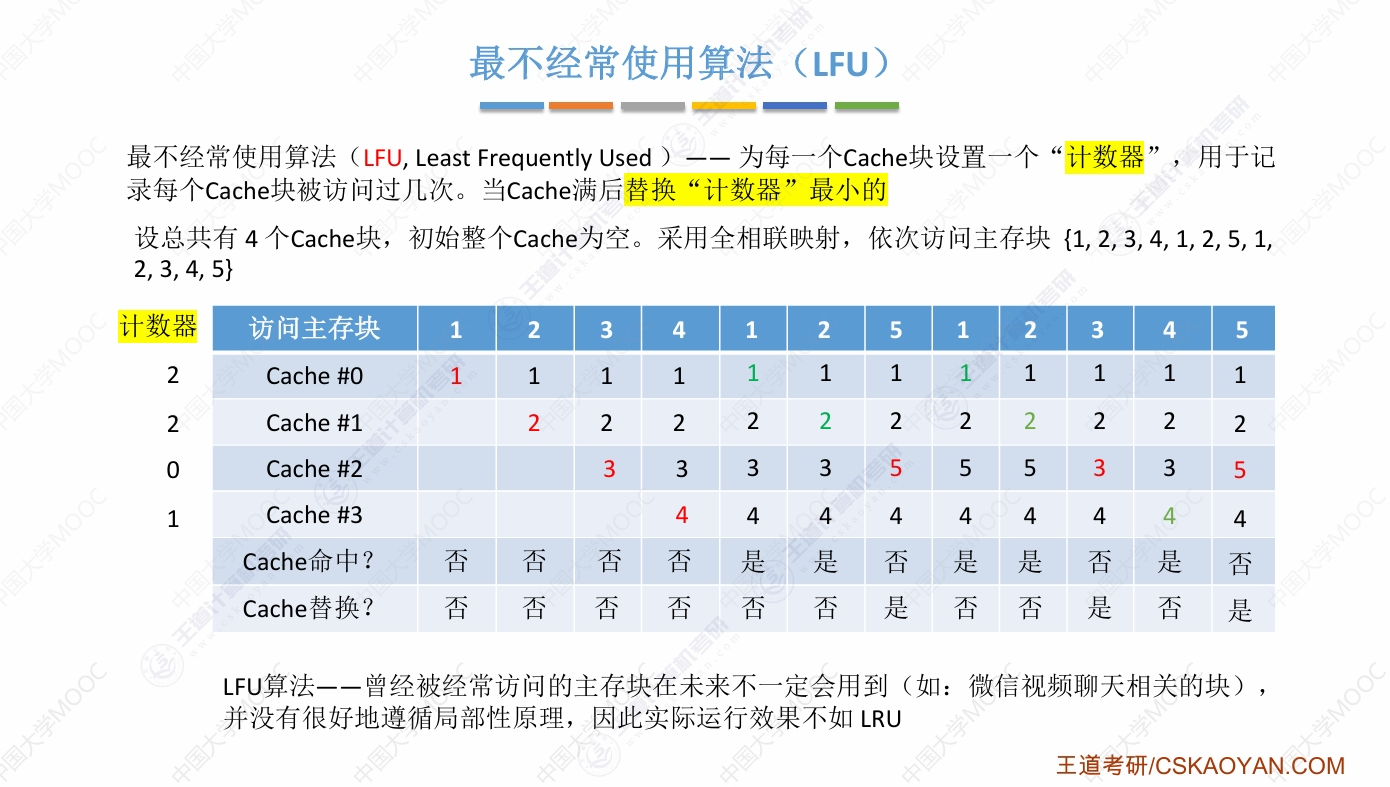

- n路相联映射 : 每n个Cache分为一组

- 地址映射表大小=Cache行数x主存容量与Cache容量之比+1

- 若有多个计数器最小的行,可按行号递增进行选择

- 对于虚拟存储器,主存的页和虚存的页一样大

- 逻辑地址=虚页号+页内地址

- 物理地址=实页号+页内地址

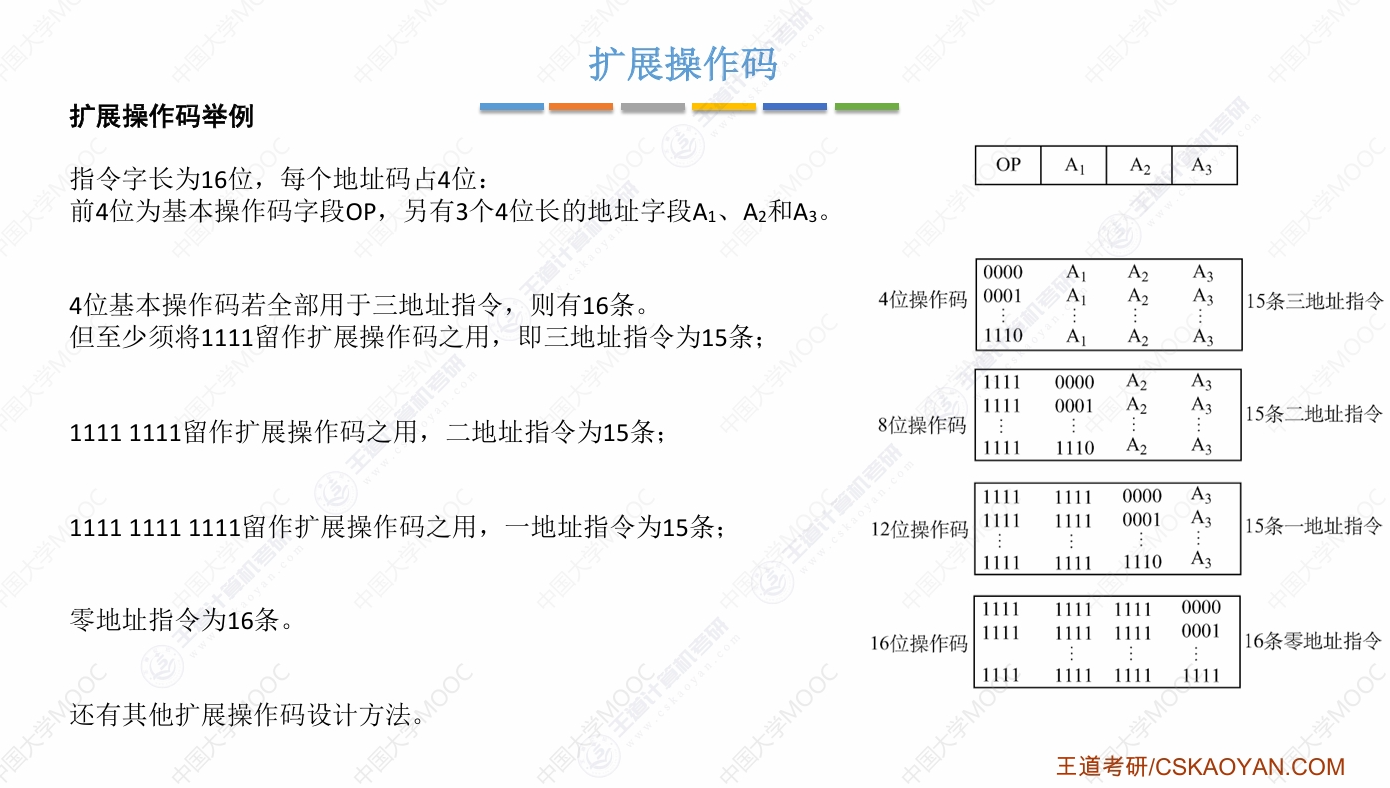

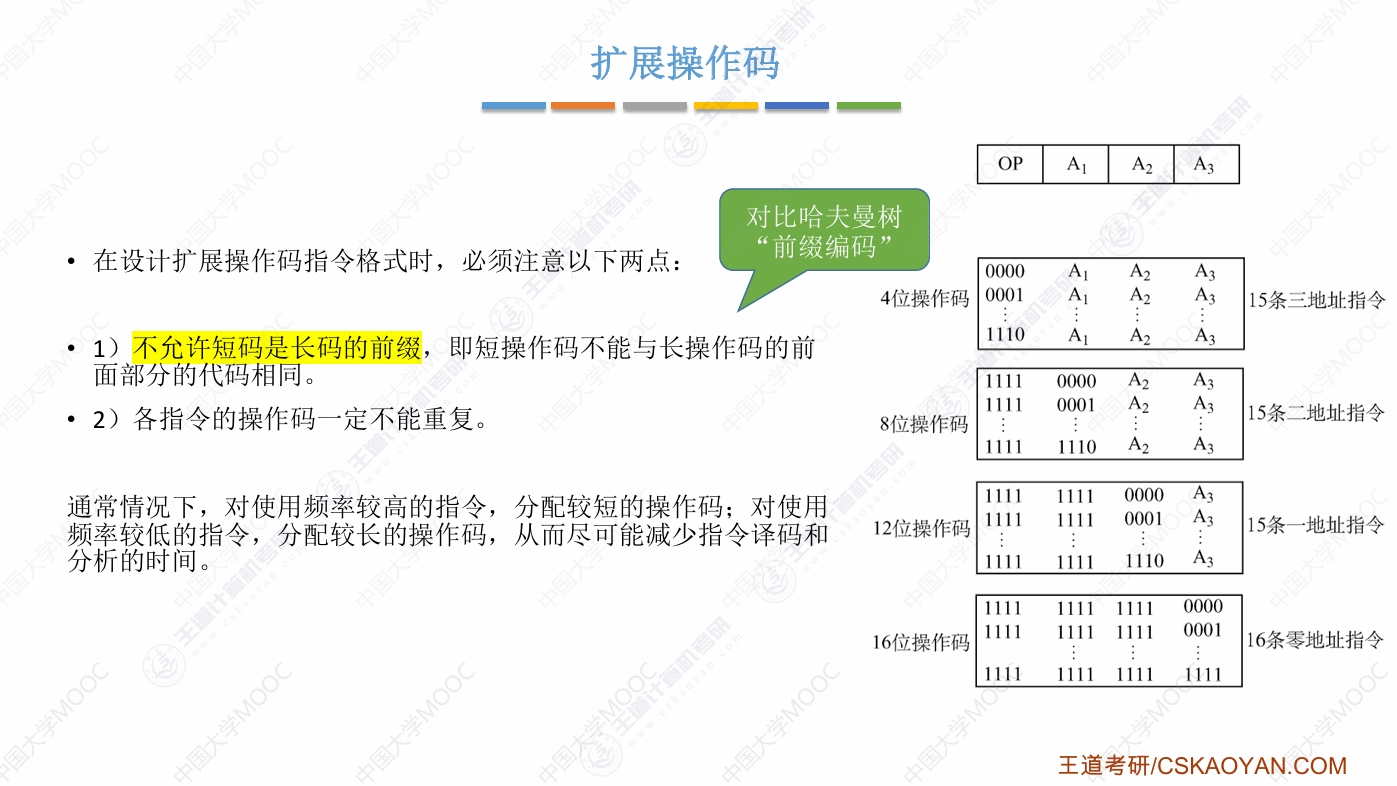

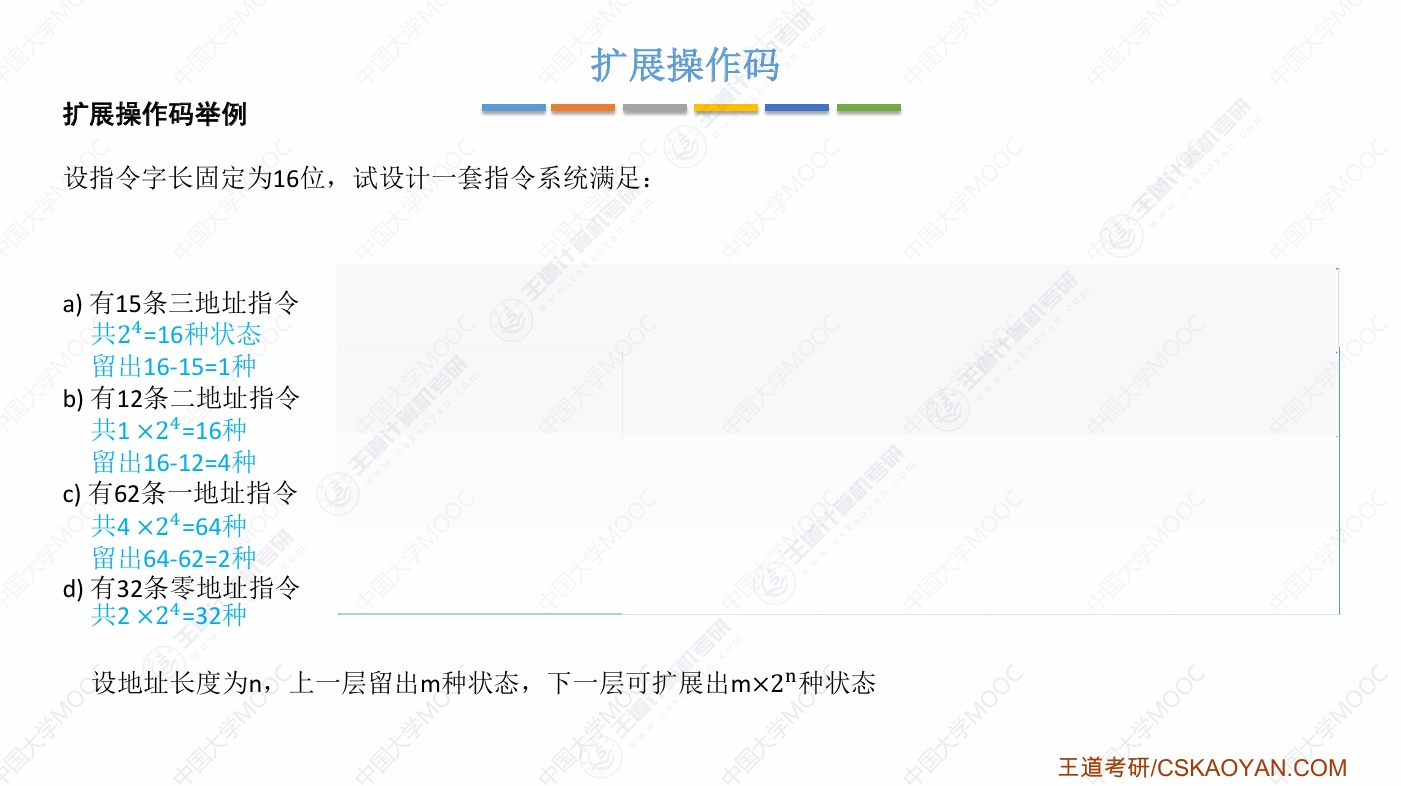

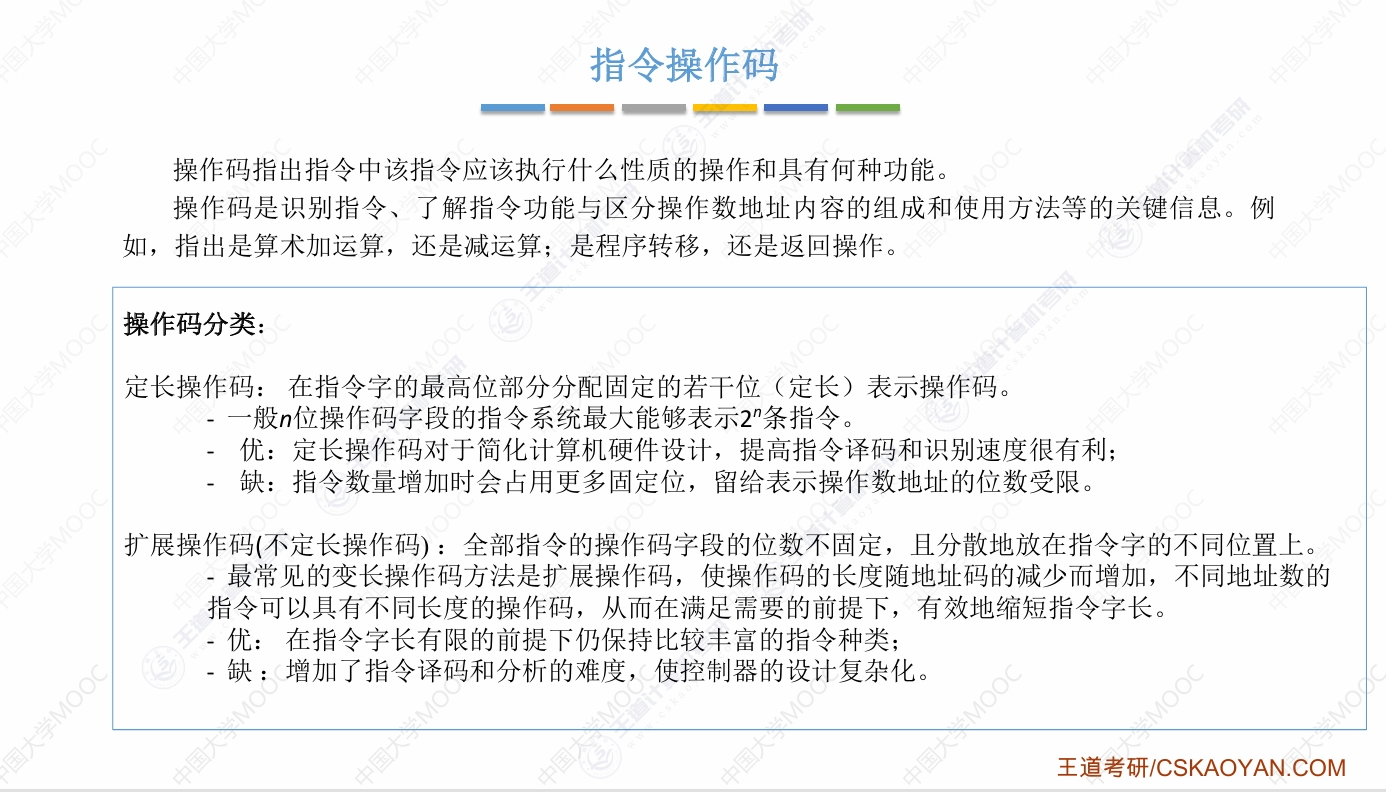

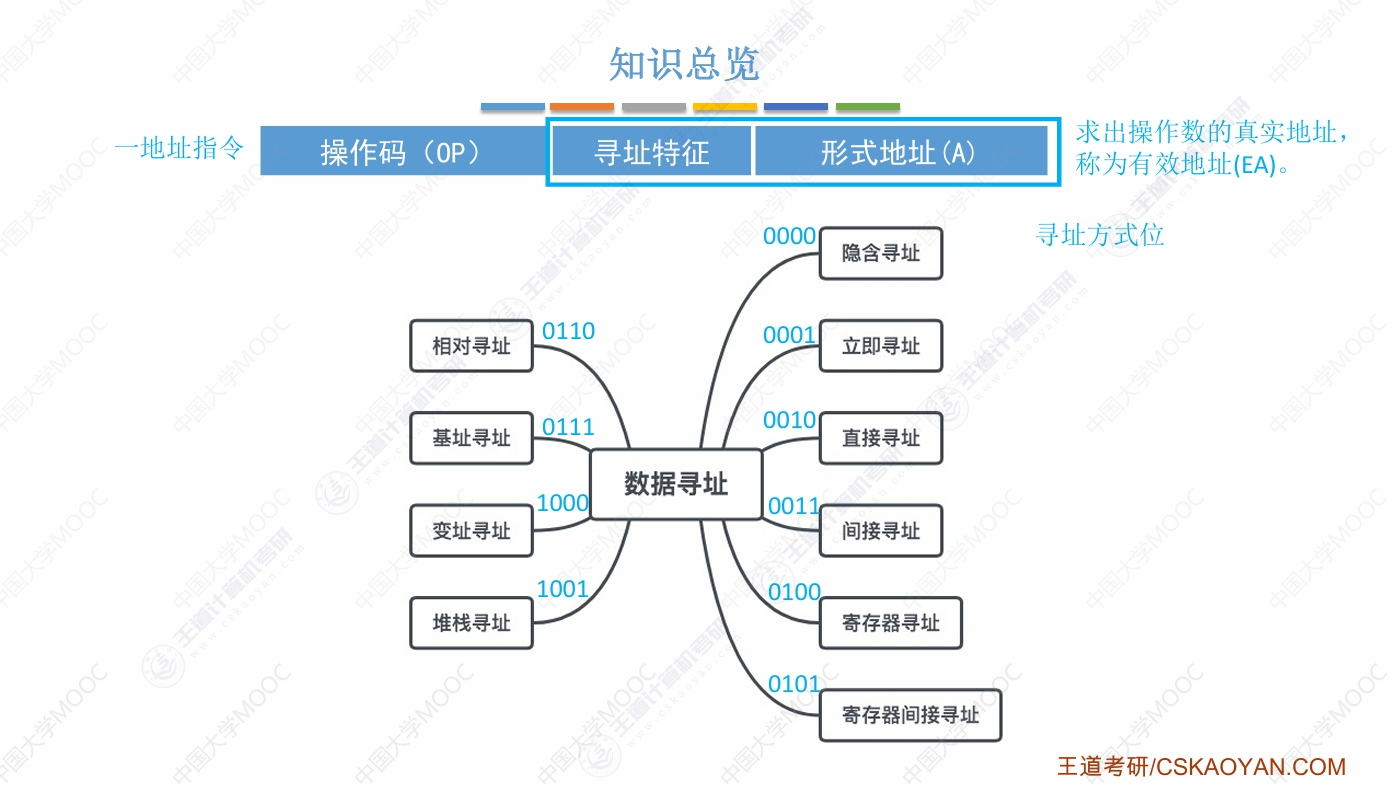

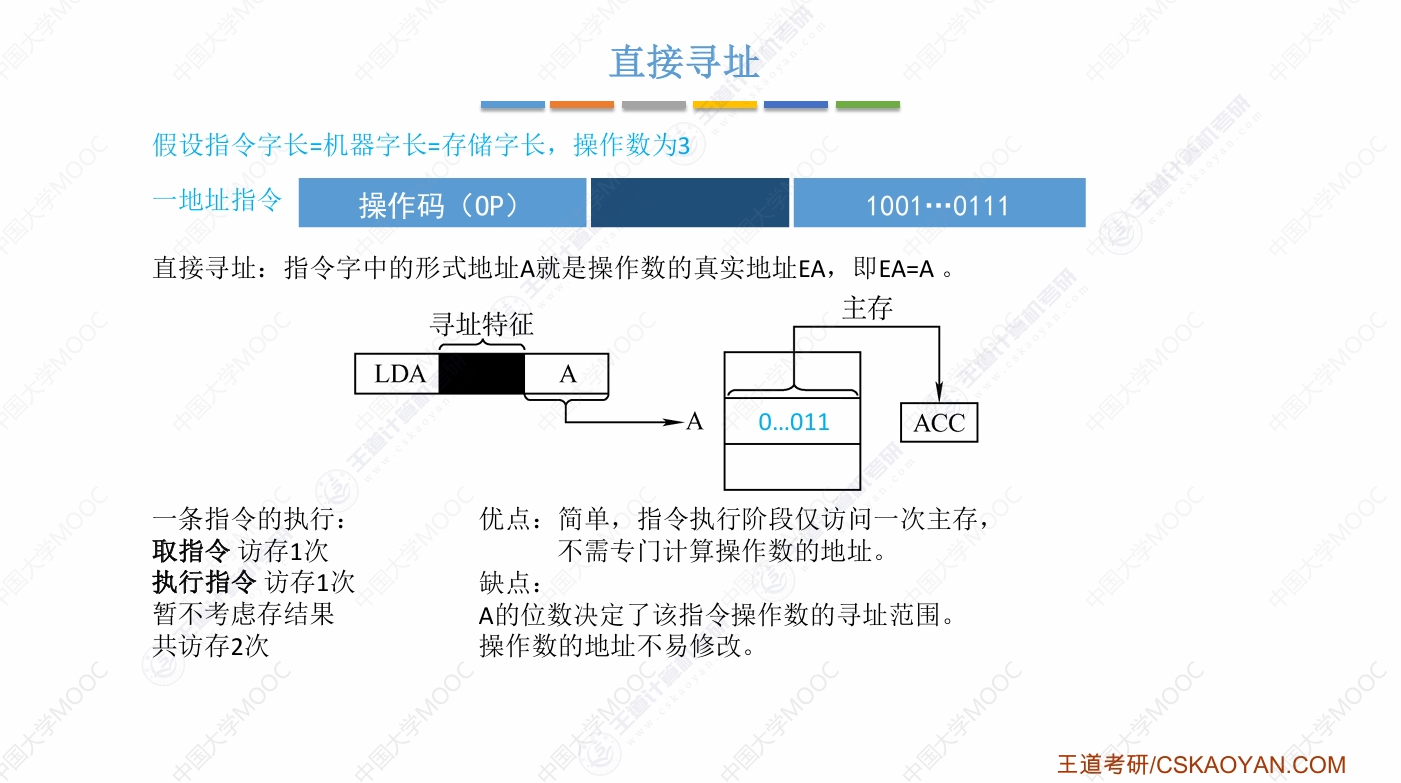

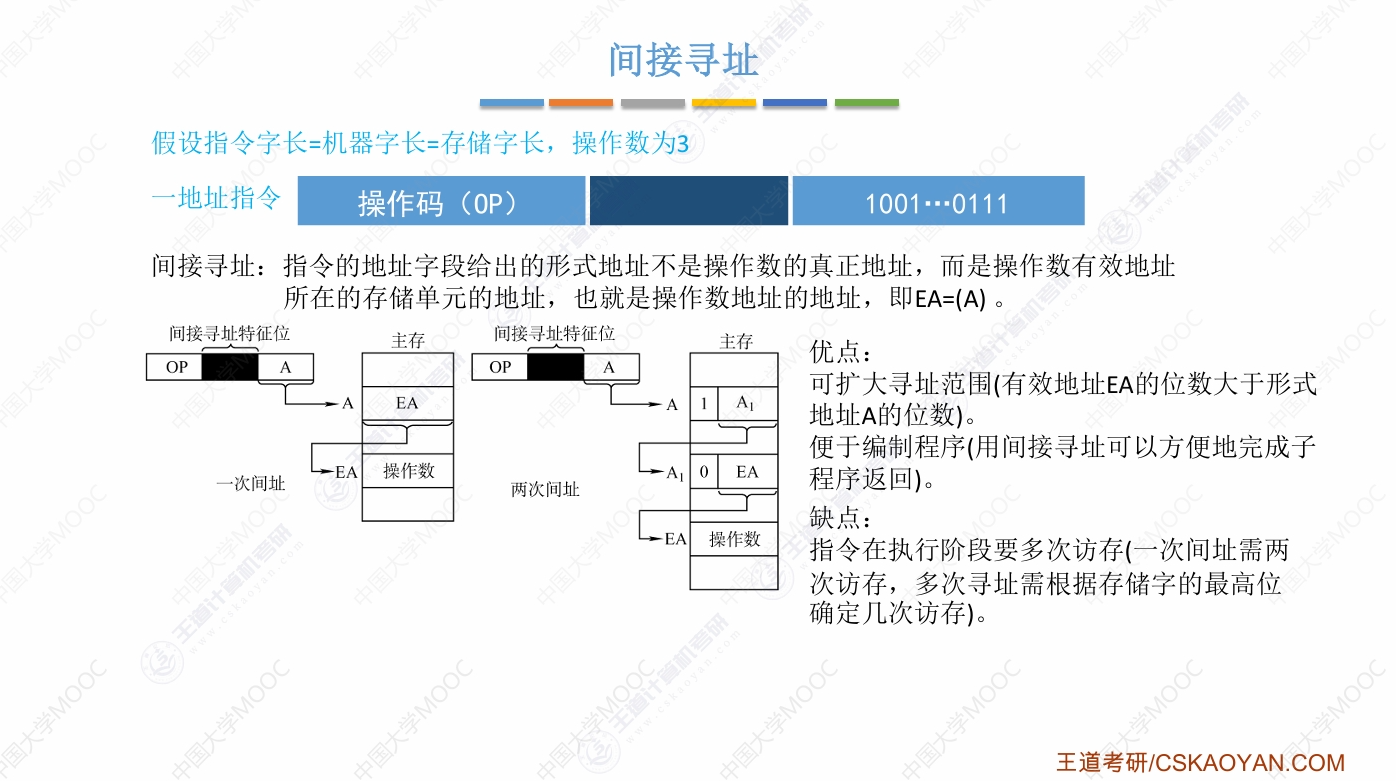

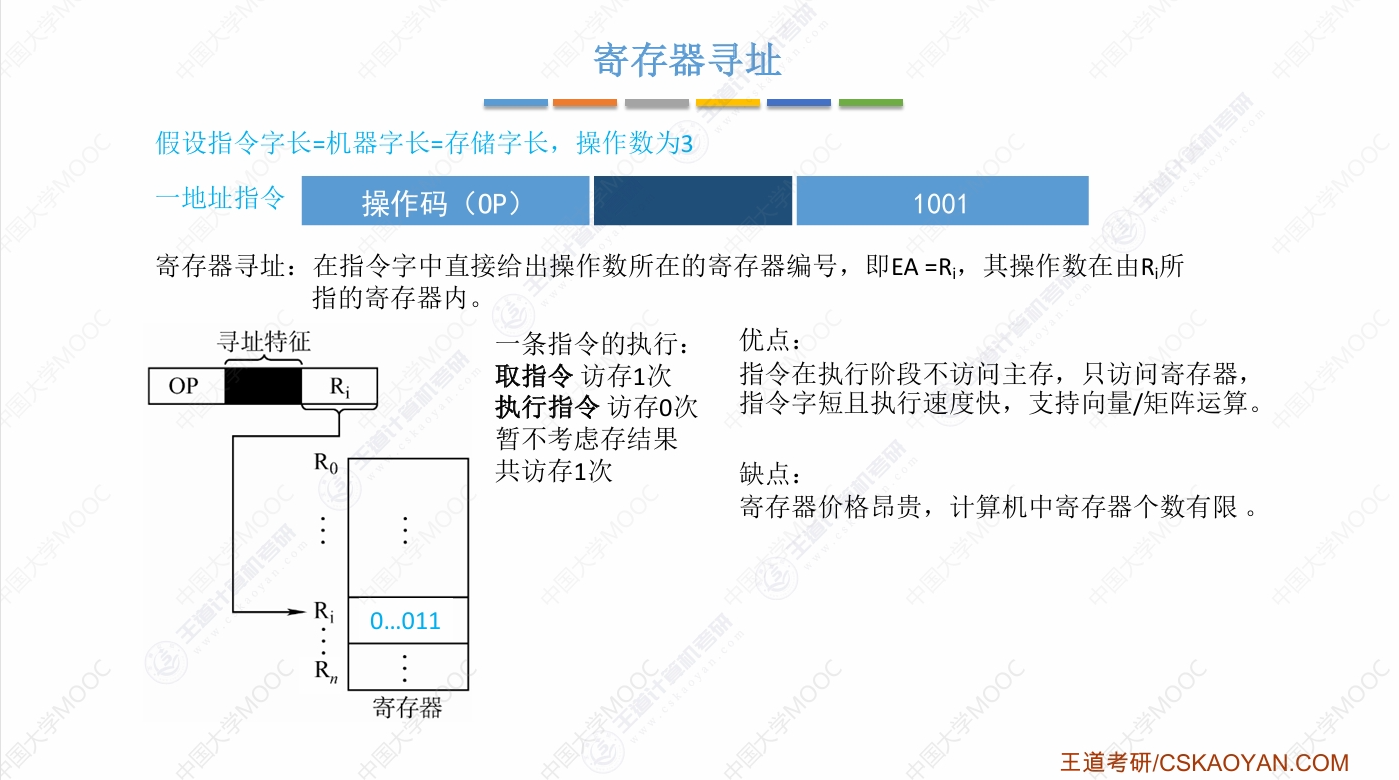

四丶指令系统

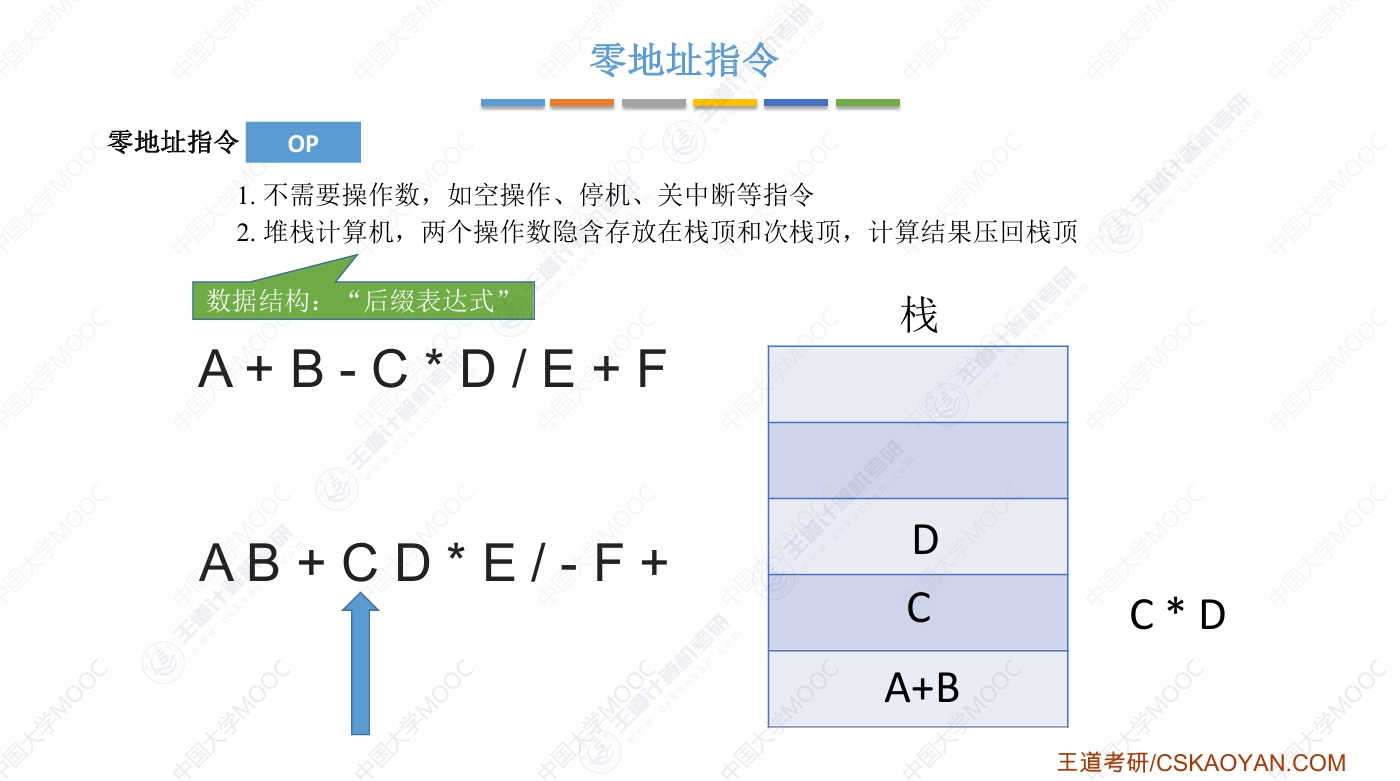

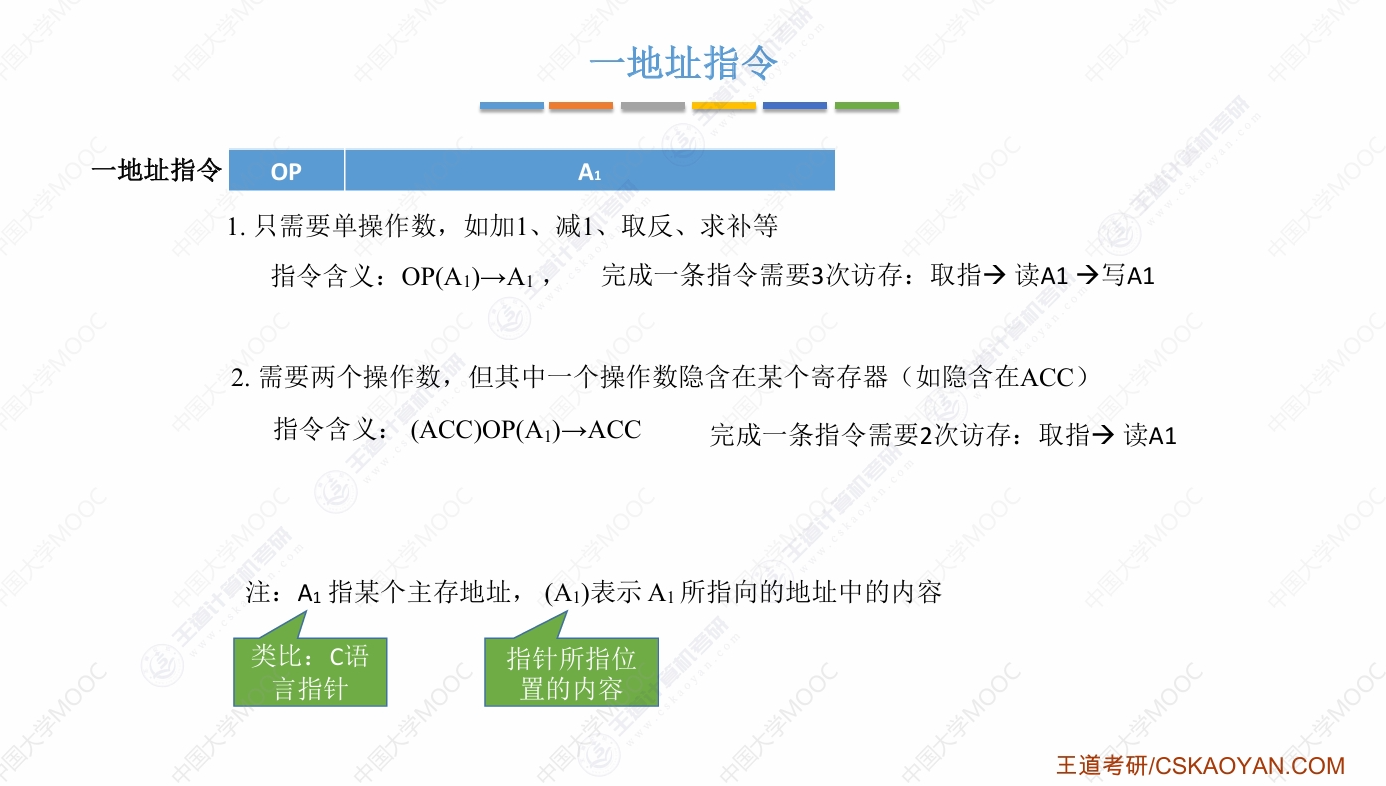

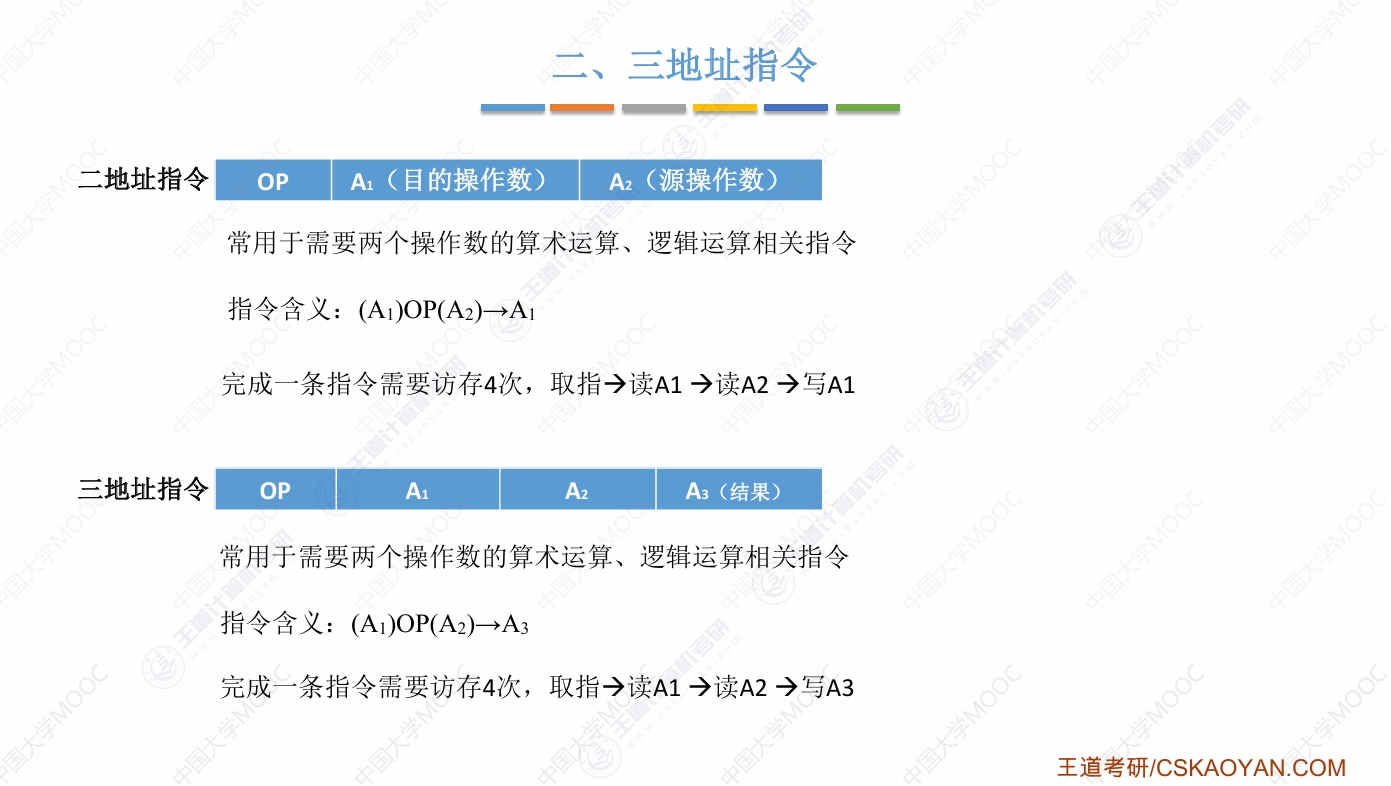

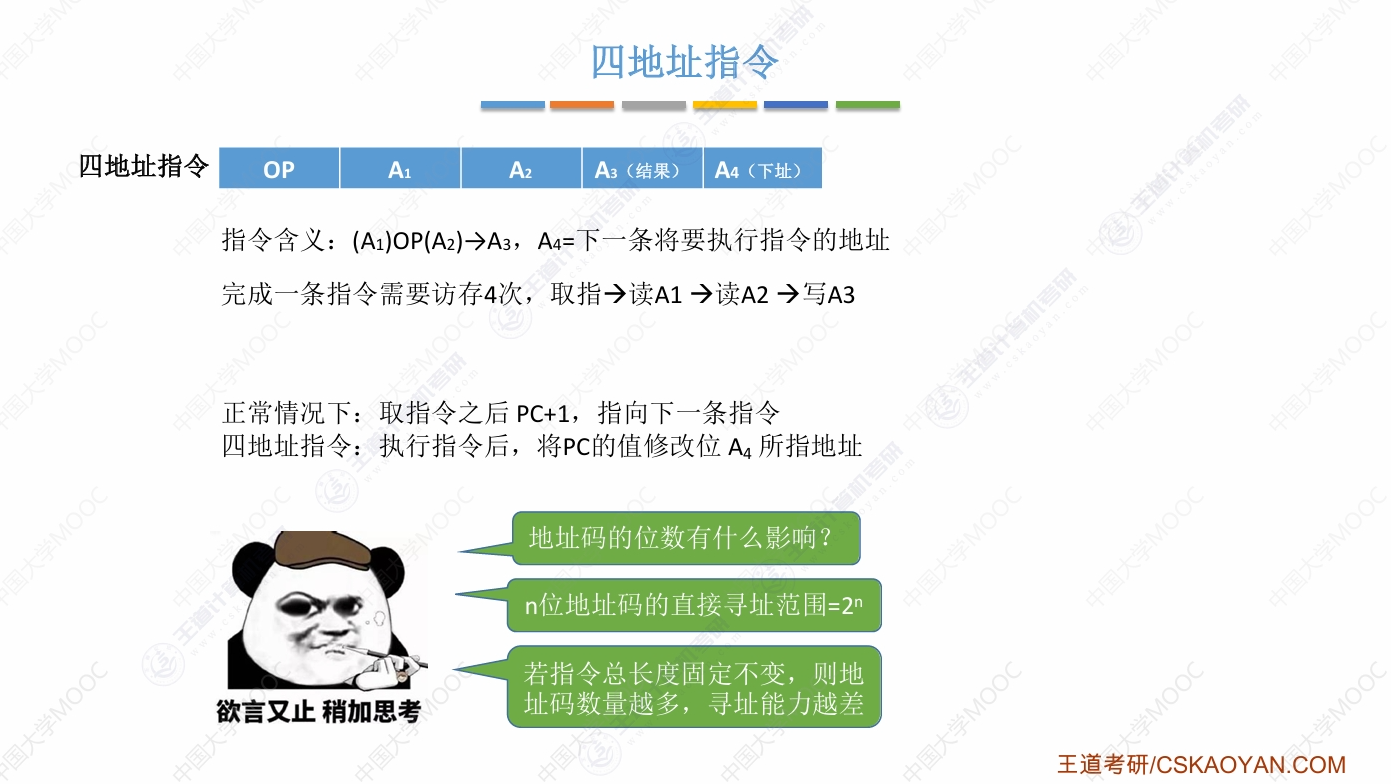

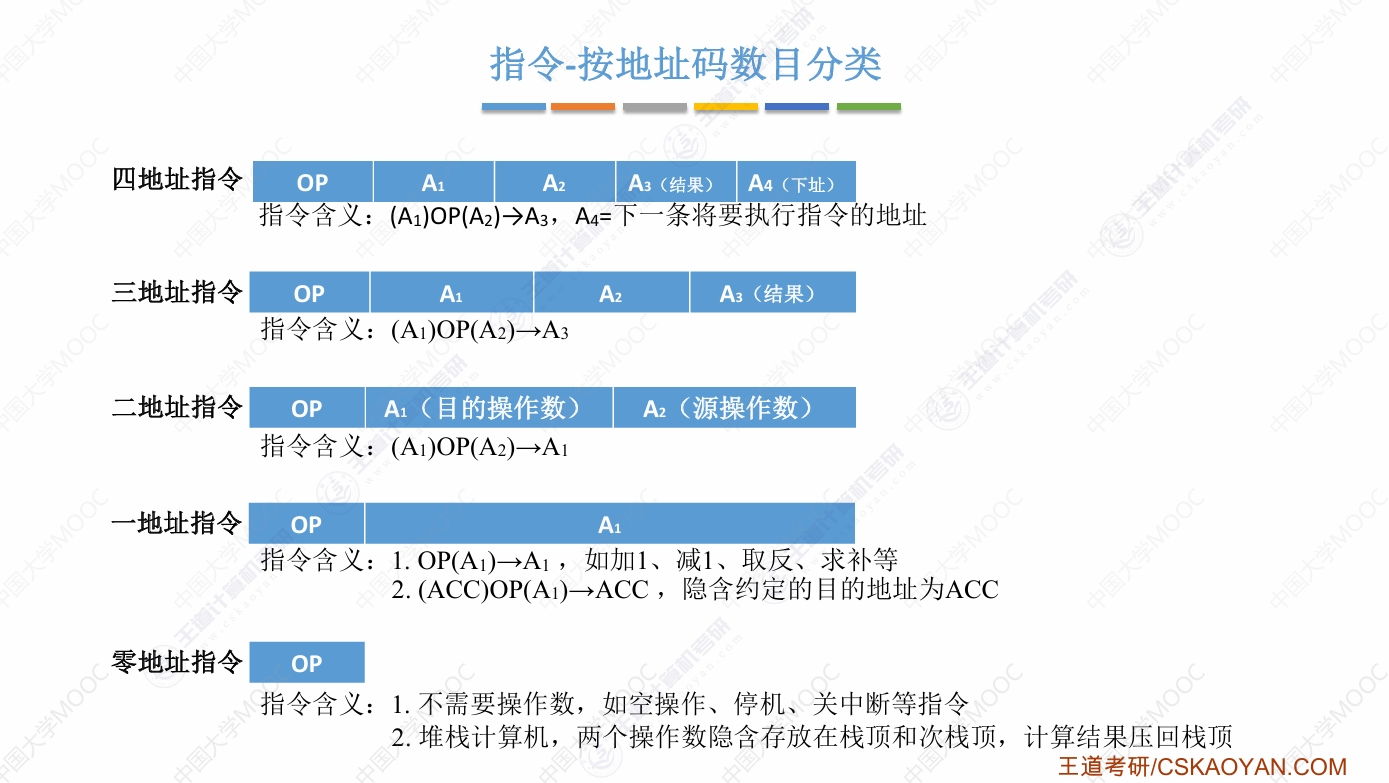

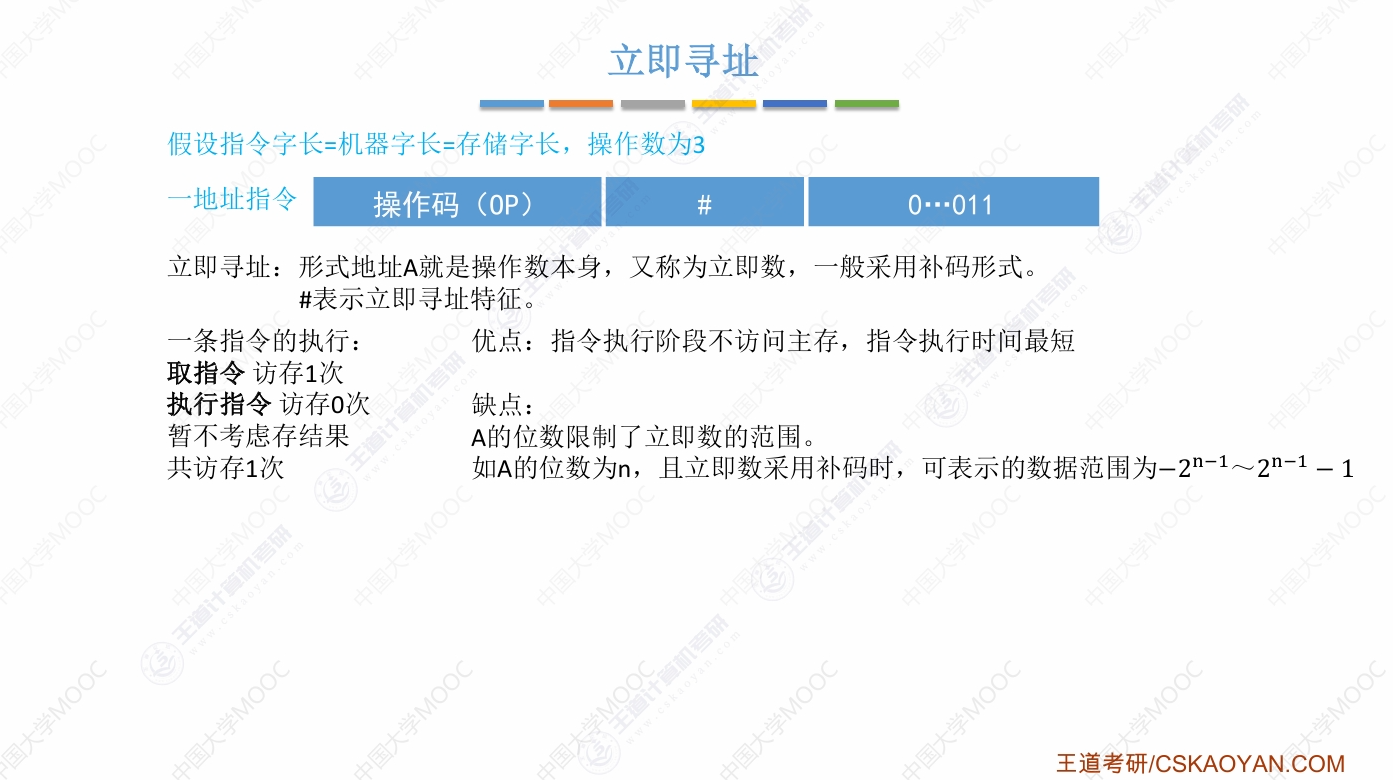

- 地址码存储的是形式地址(存储单元地址)

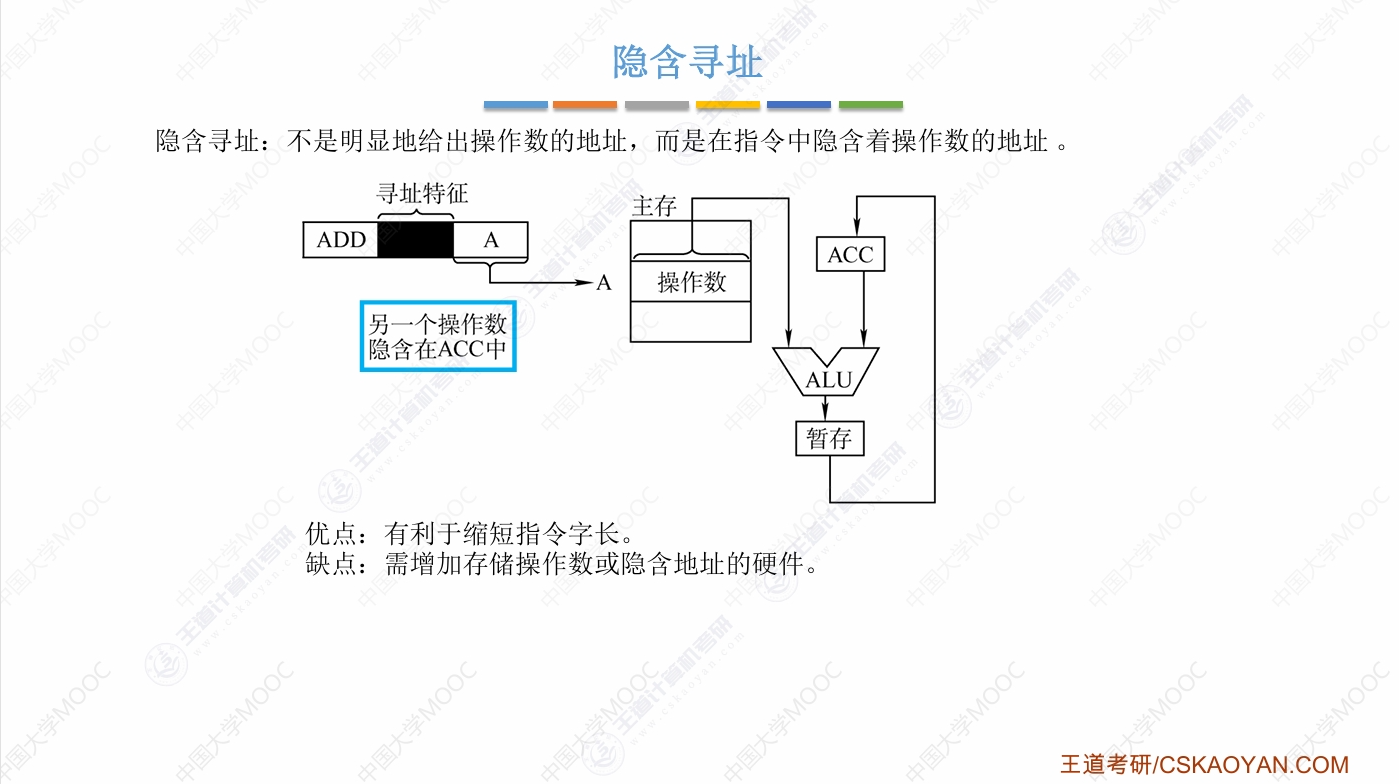

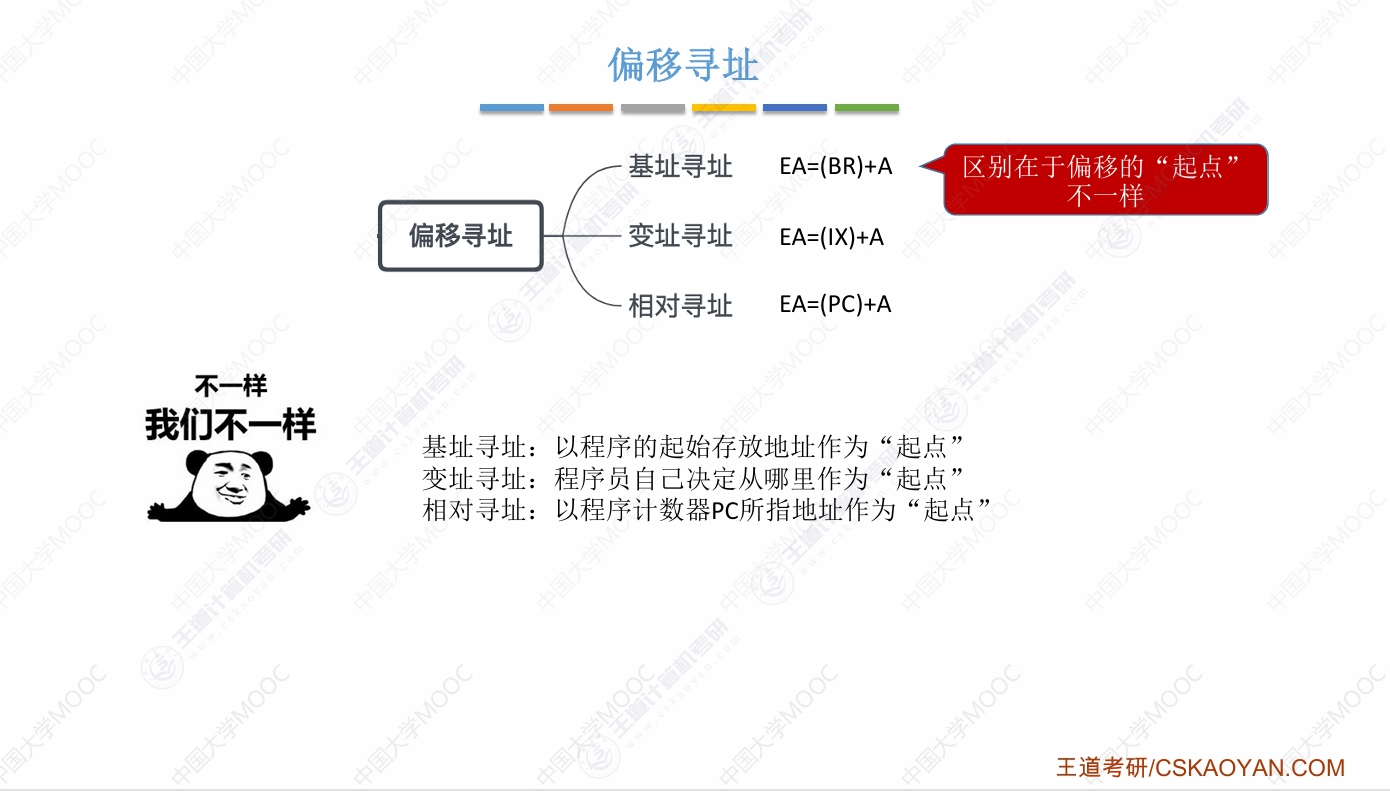

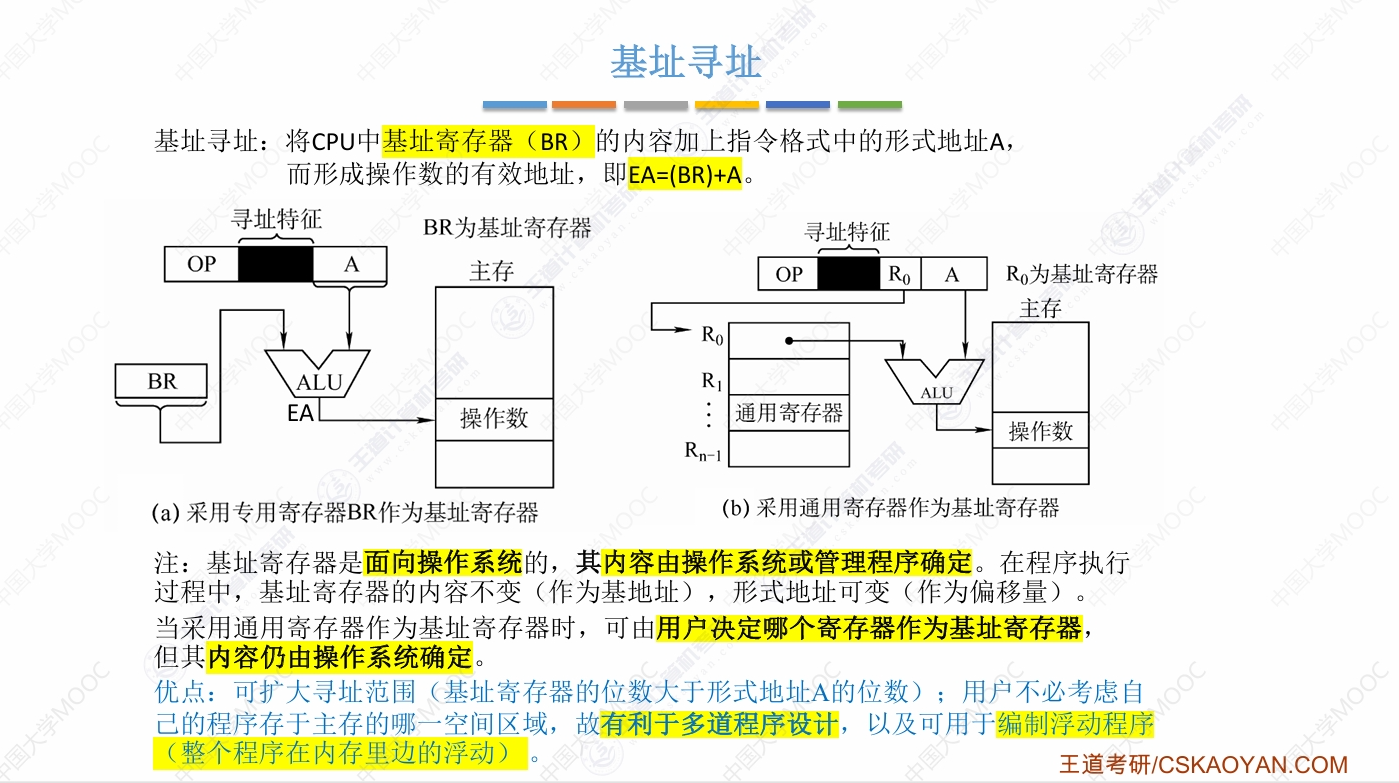

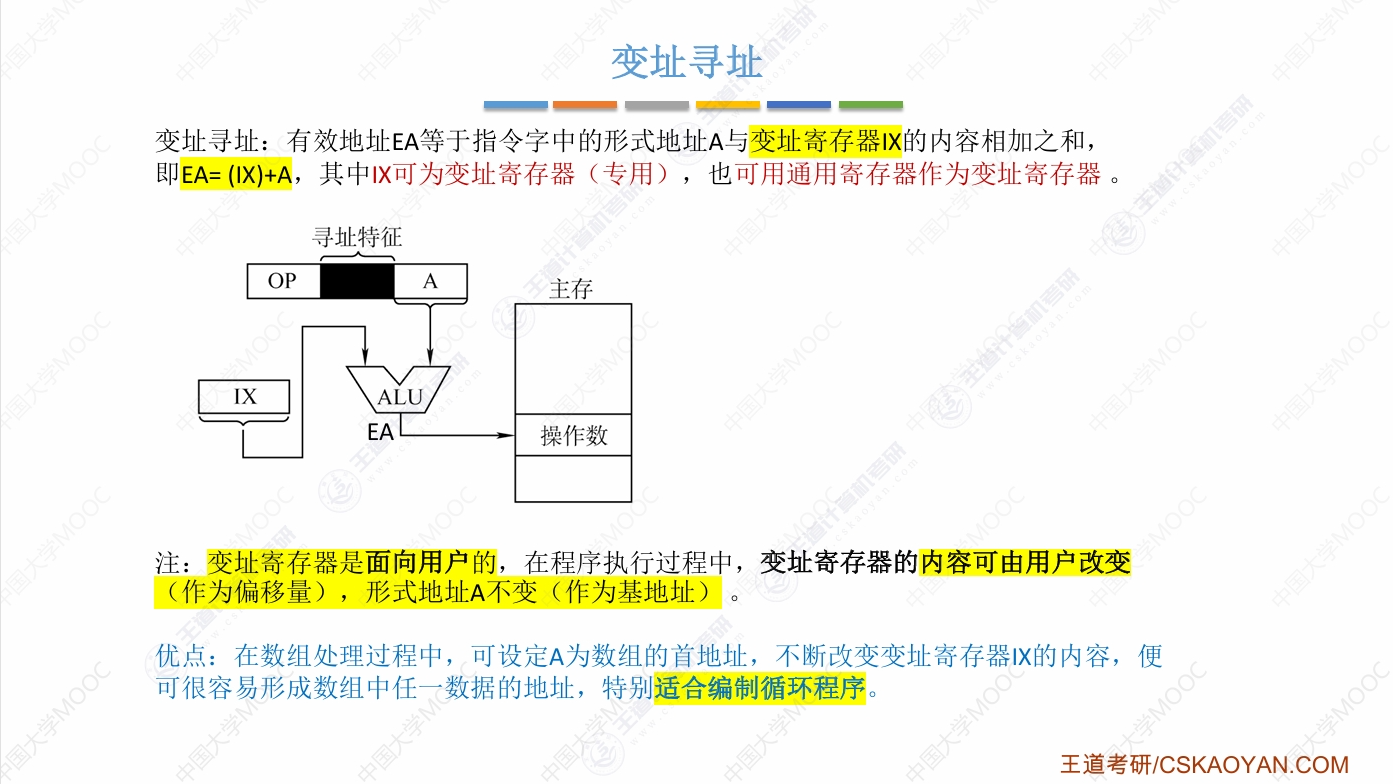

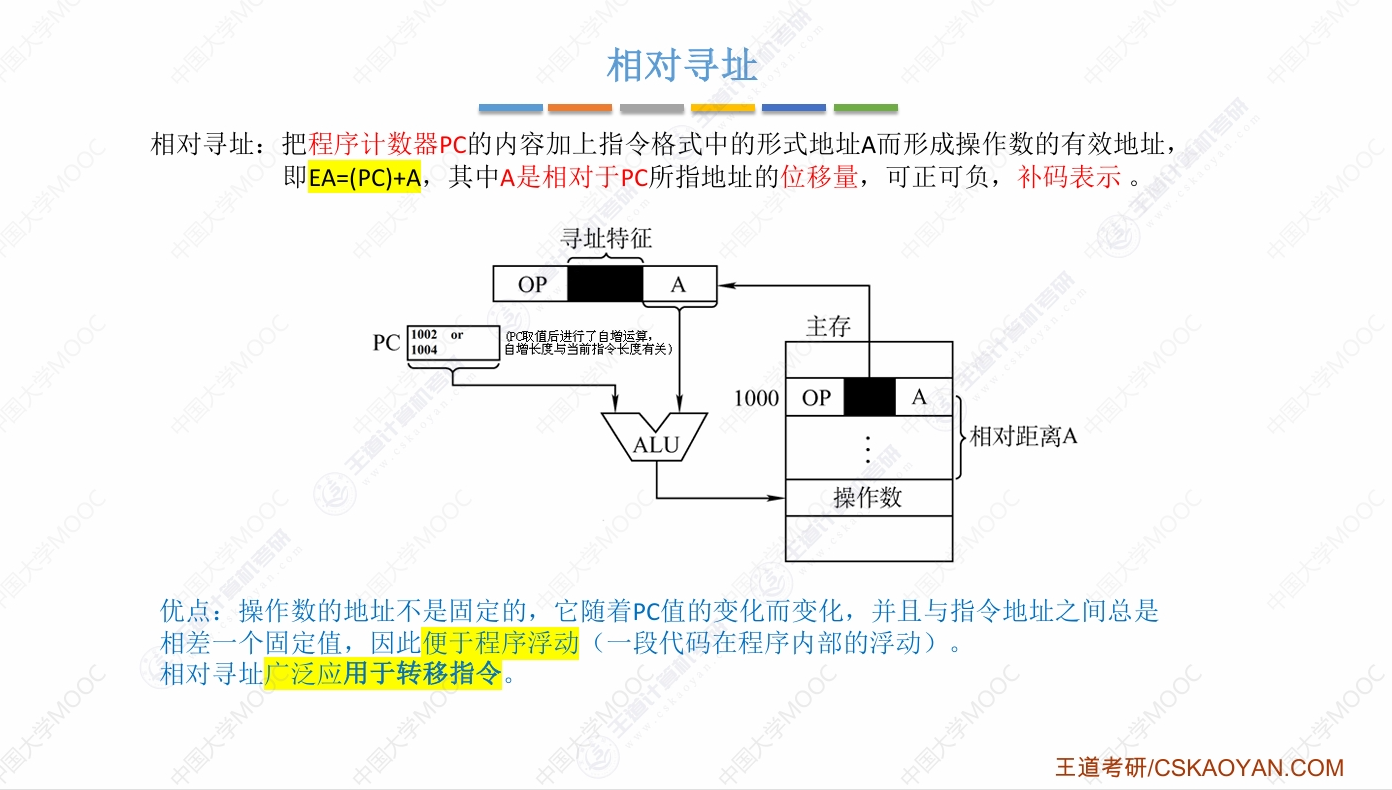

- 基址寻址优点 : 便于程序浮动,方便实现多道程序并发运行(采用基址寻址时,更改初始地址无需修改指令中的地址码)

- 实际应用中往往需要多种寻址方式复合使用

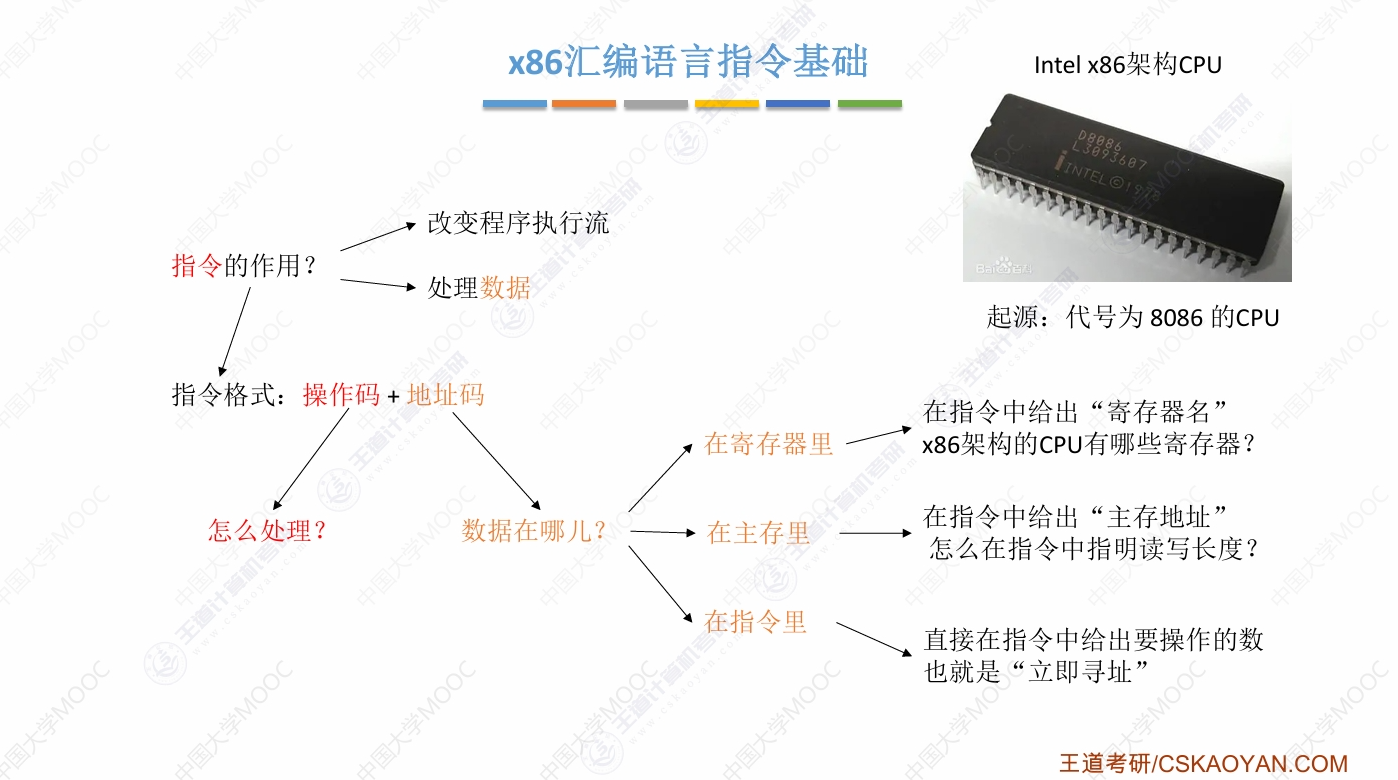

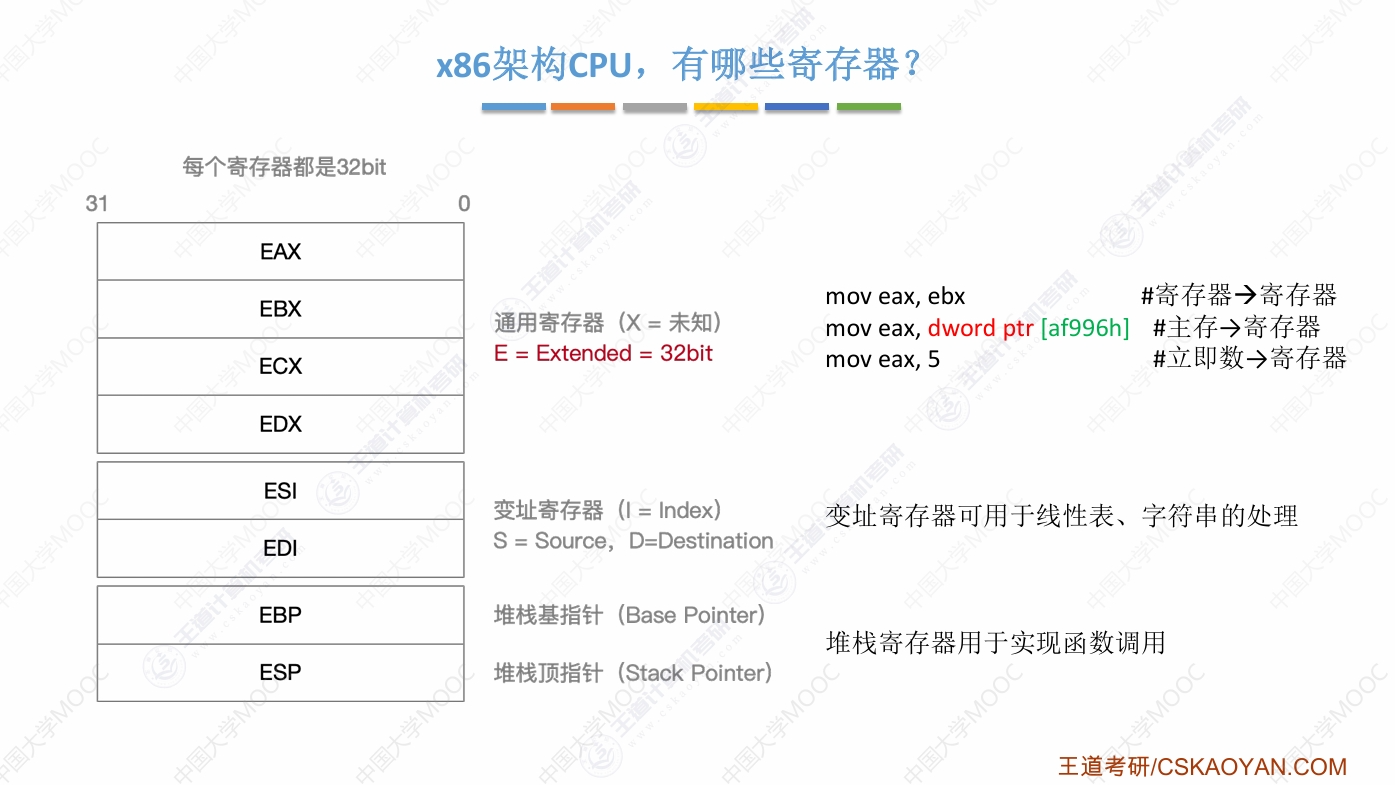

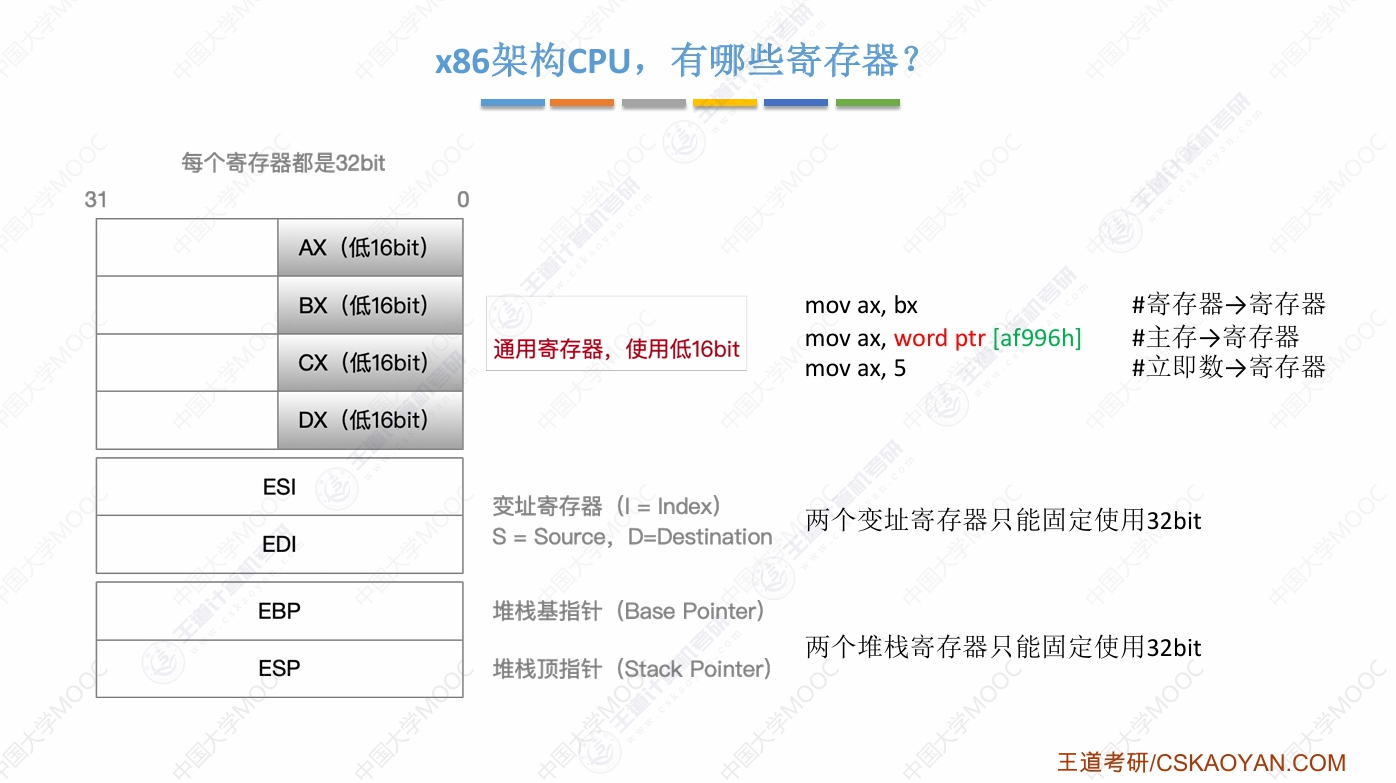

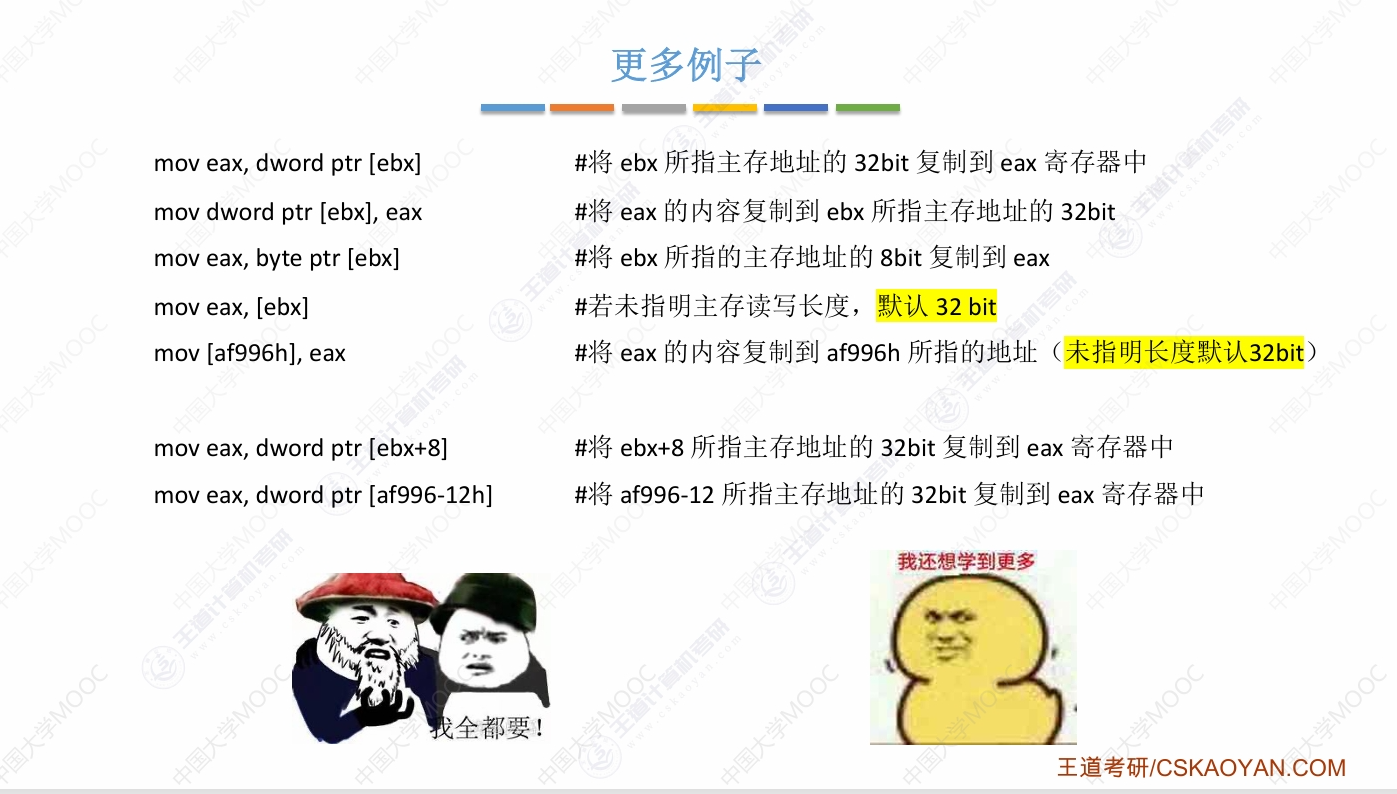

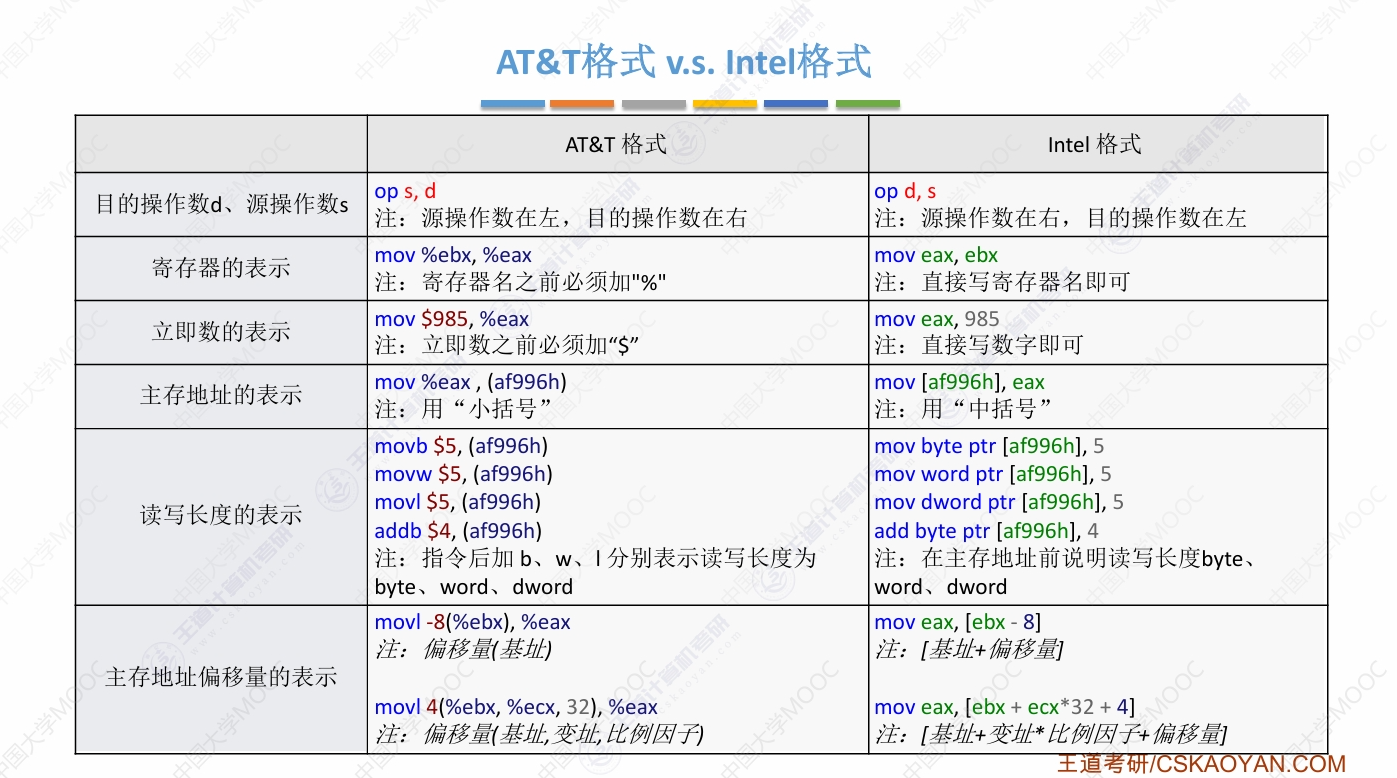

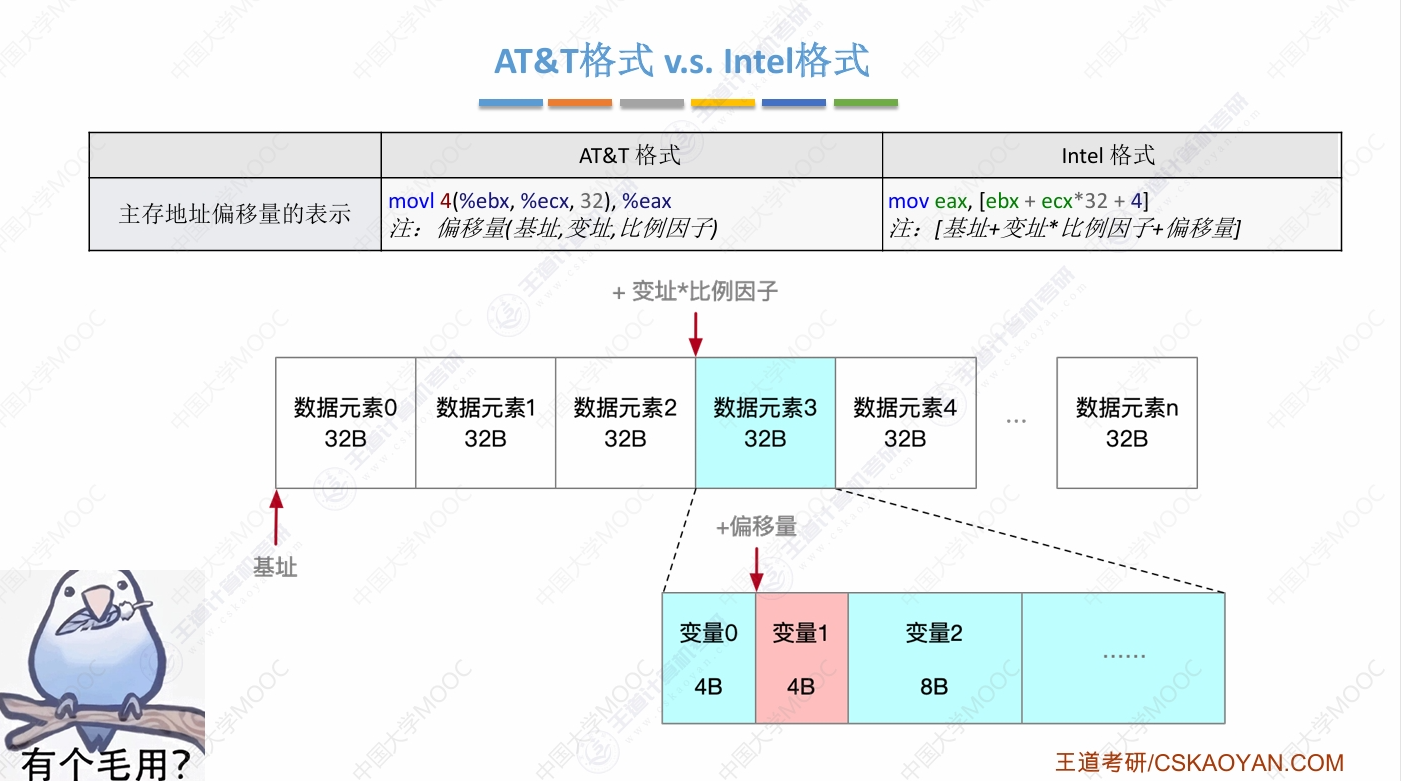

- integer 有符号整型

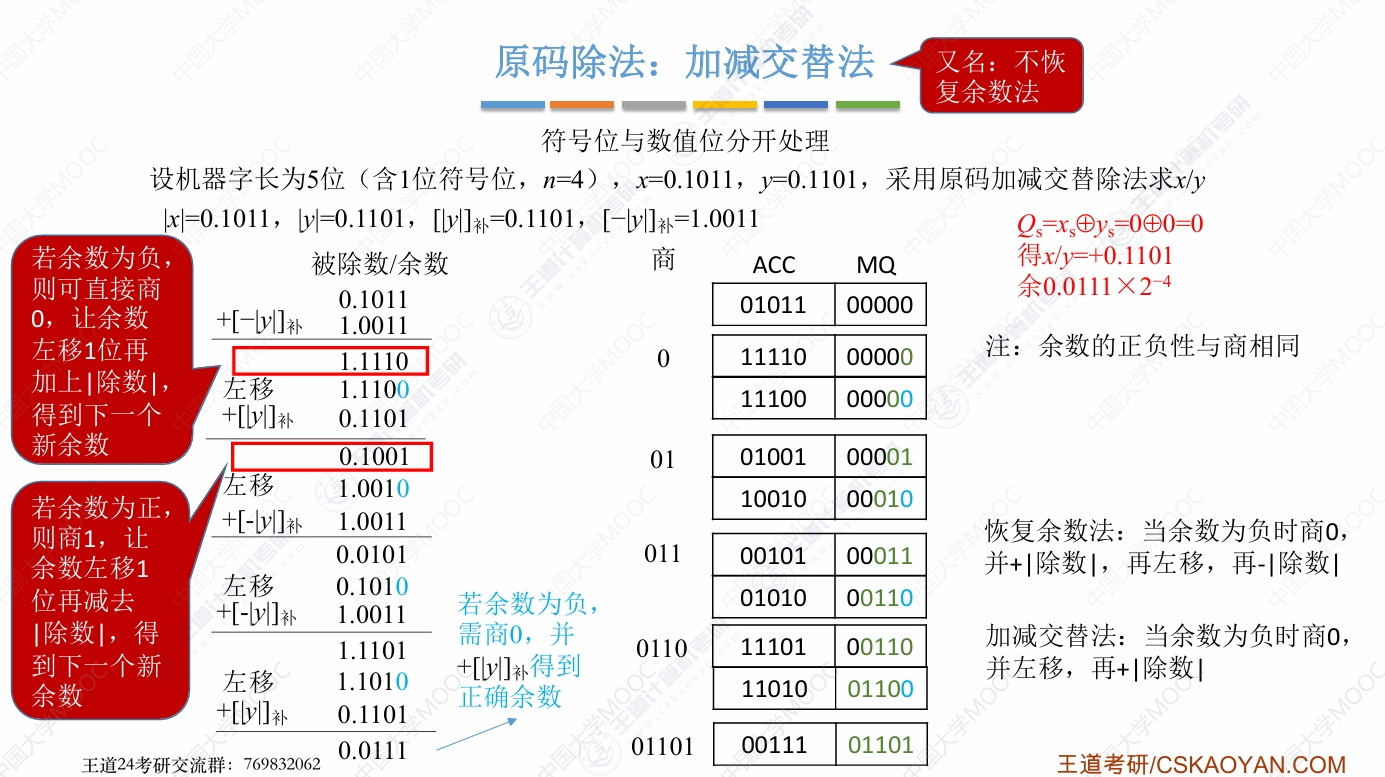

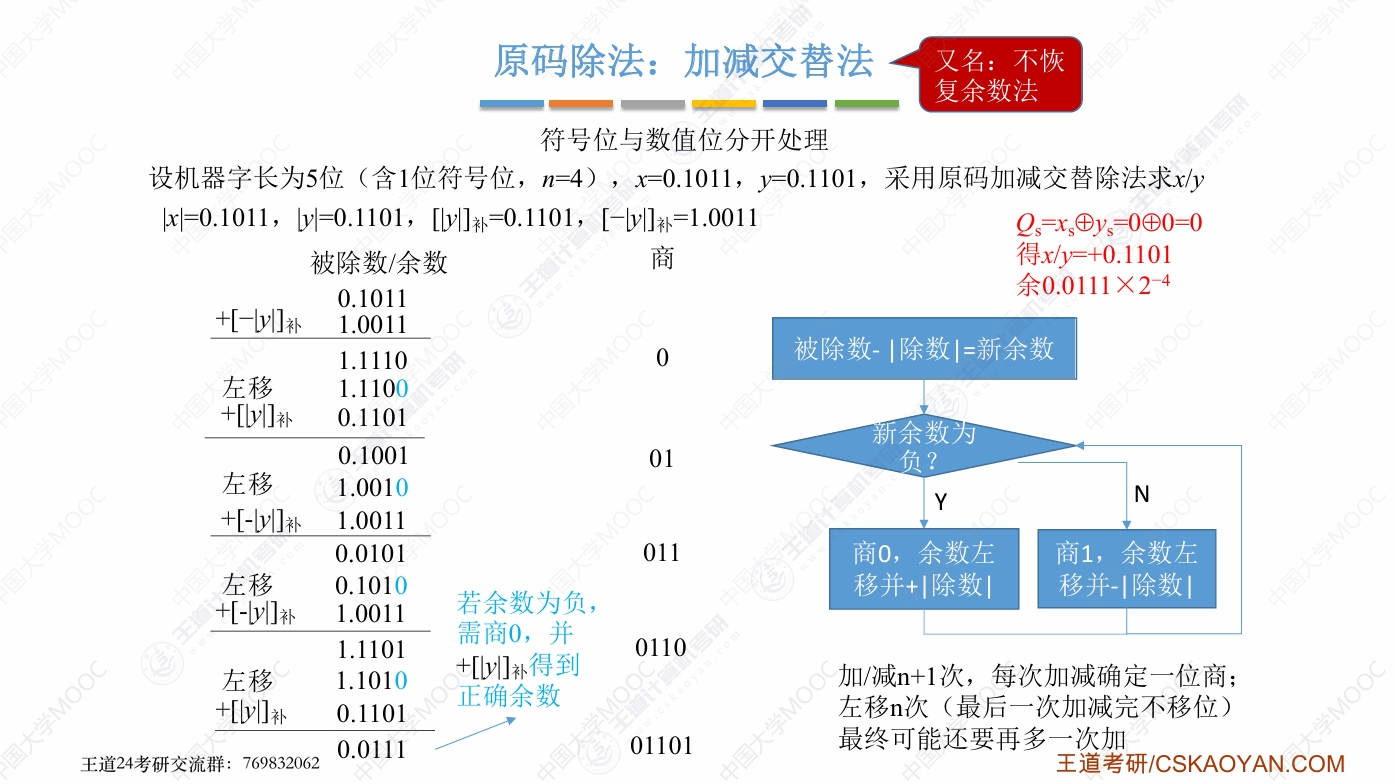

- 在进行除法运算前,需要被除数进行位扩展(32bit->64bit)

- edx:eax 两个寄存器连起来使用

- 不能两个操作数都来自主存

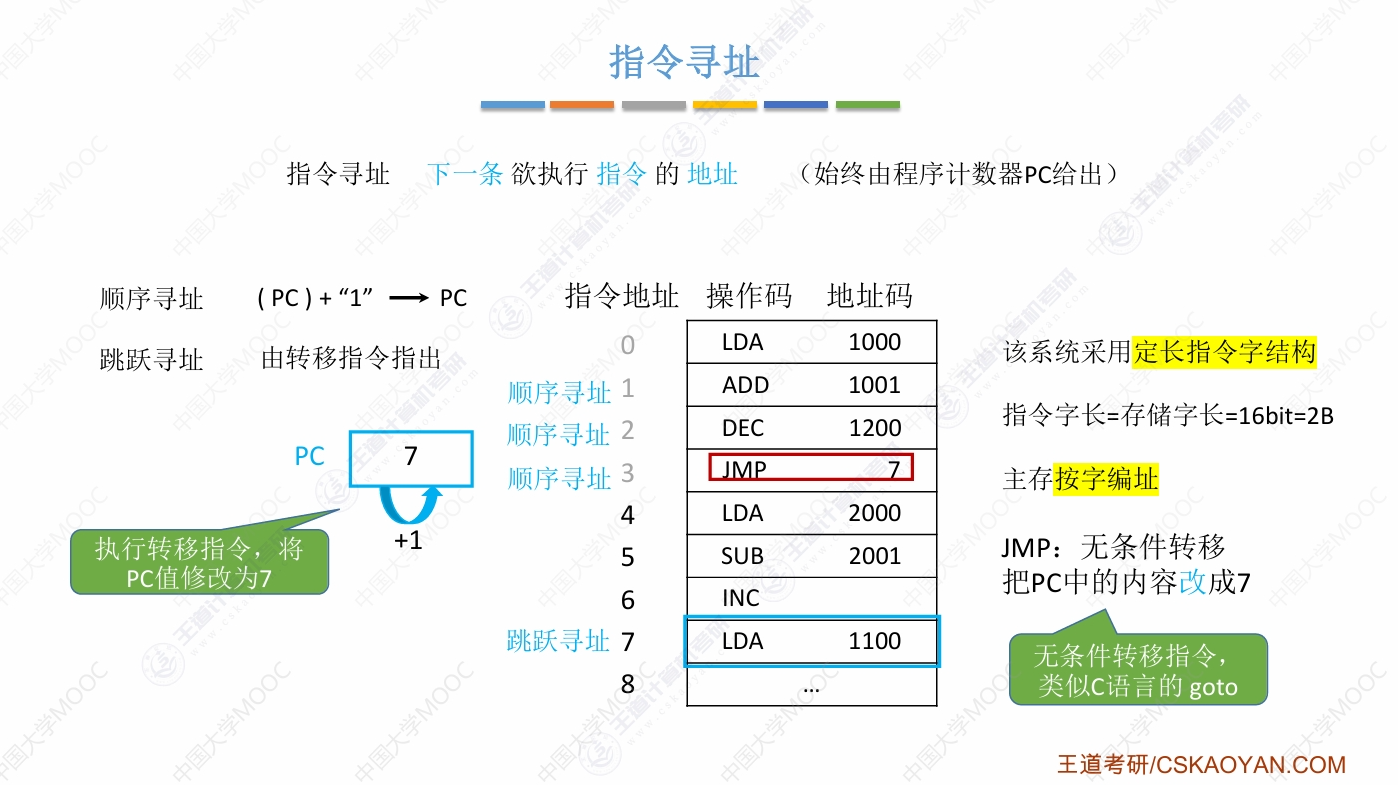

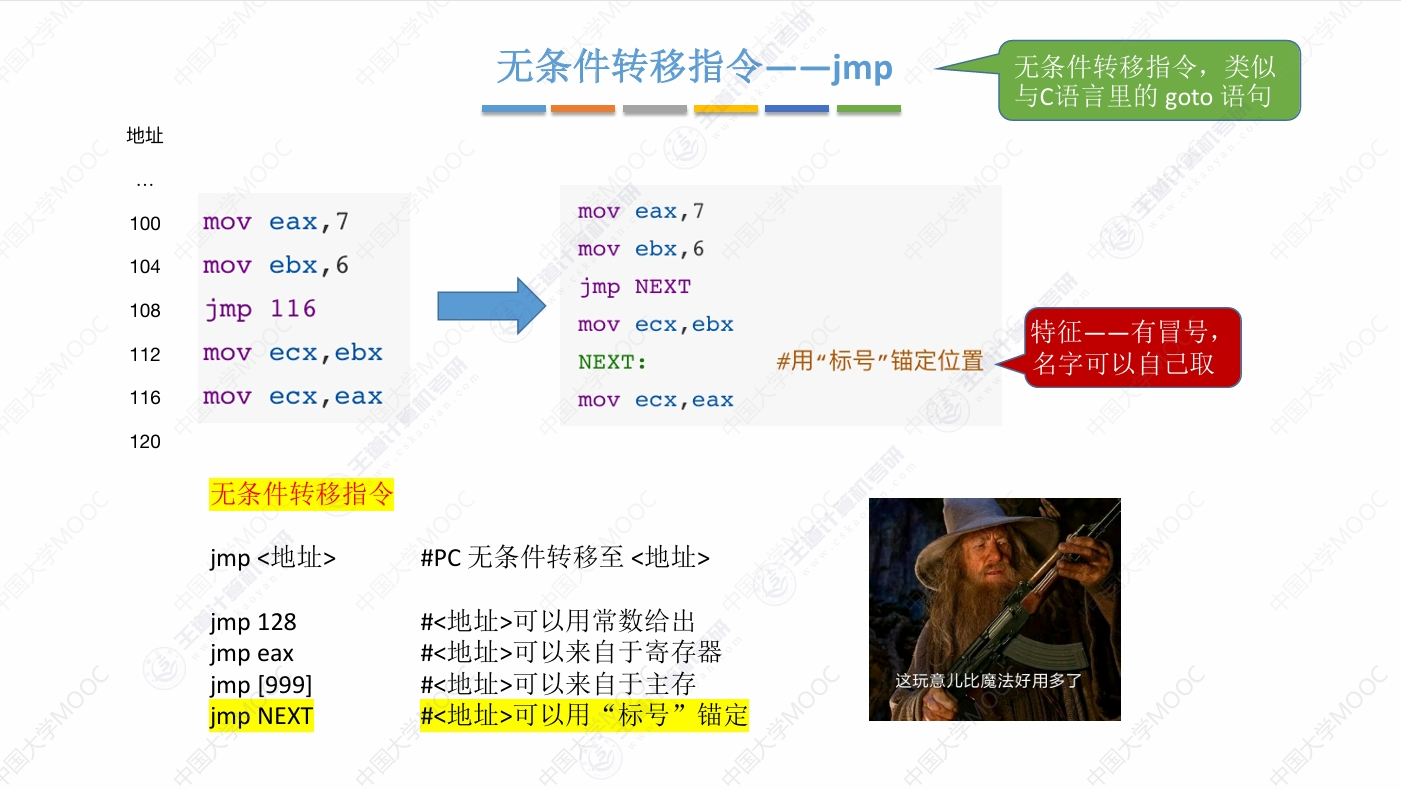

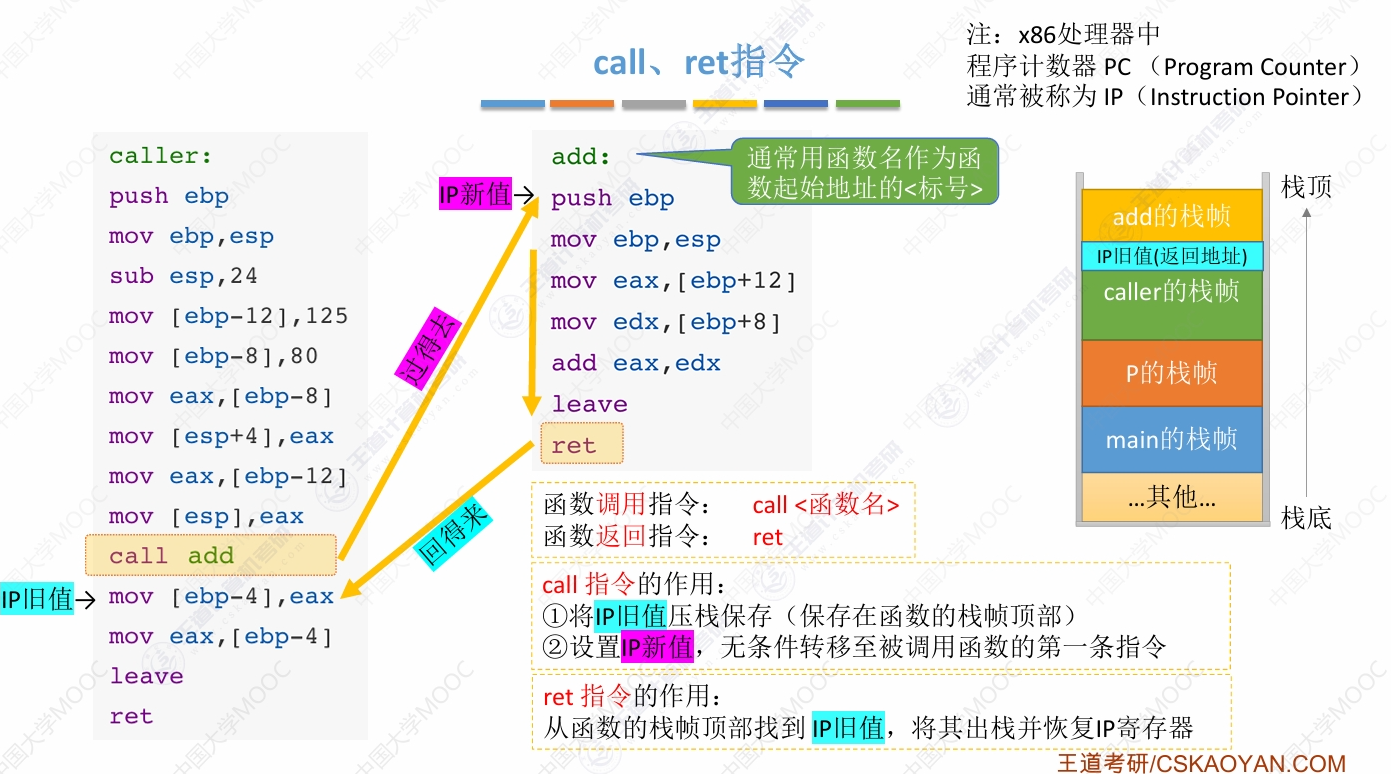

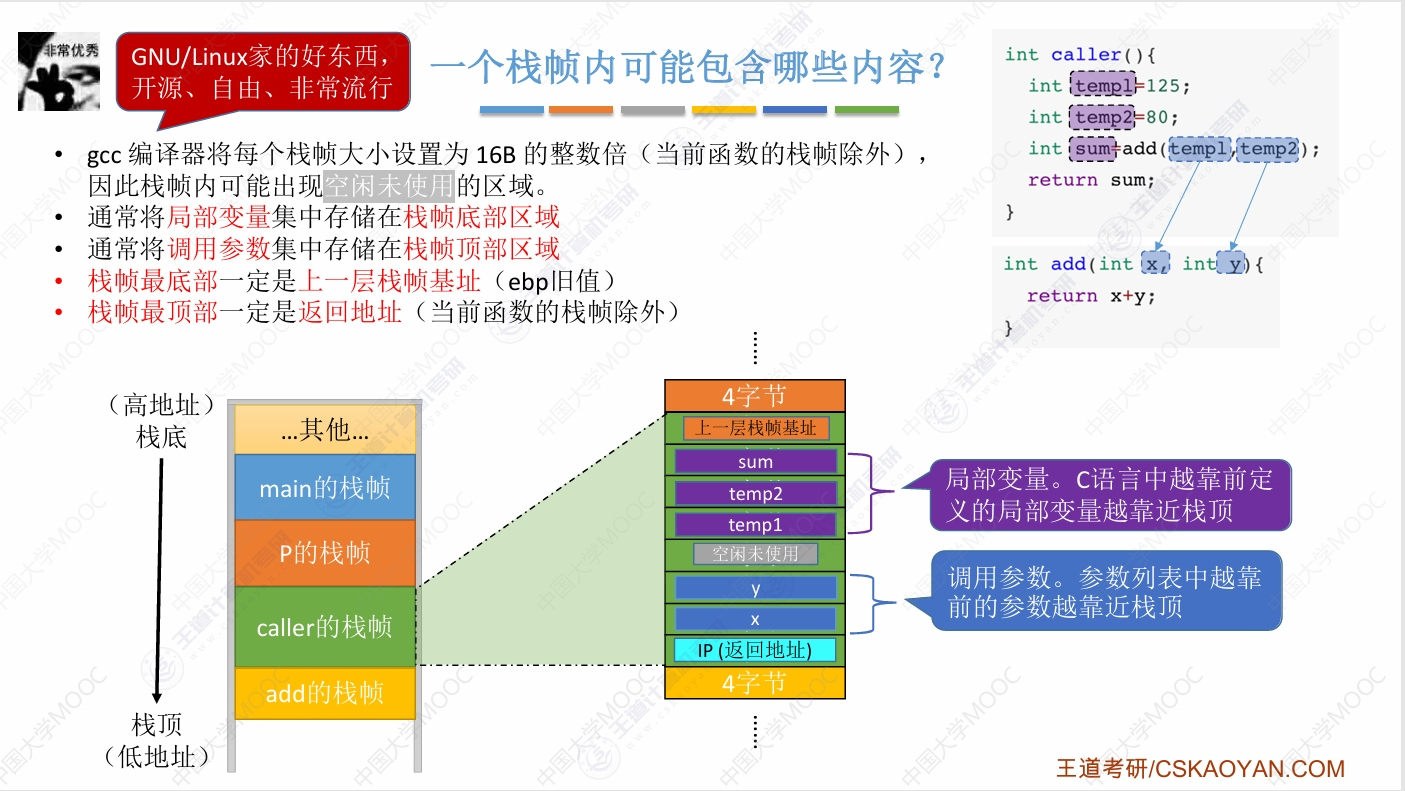

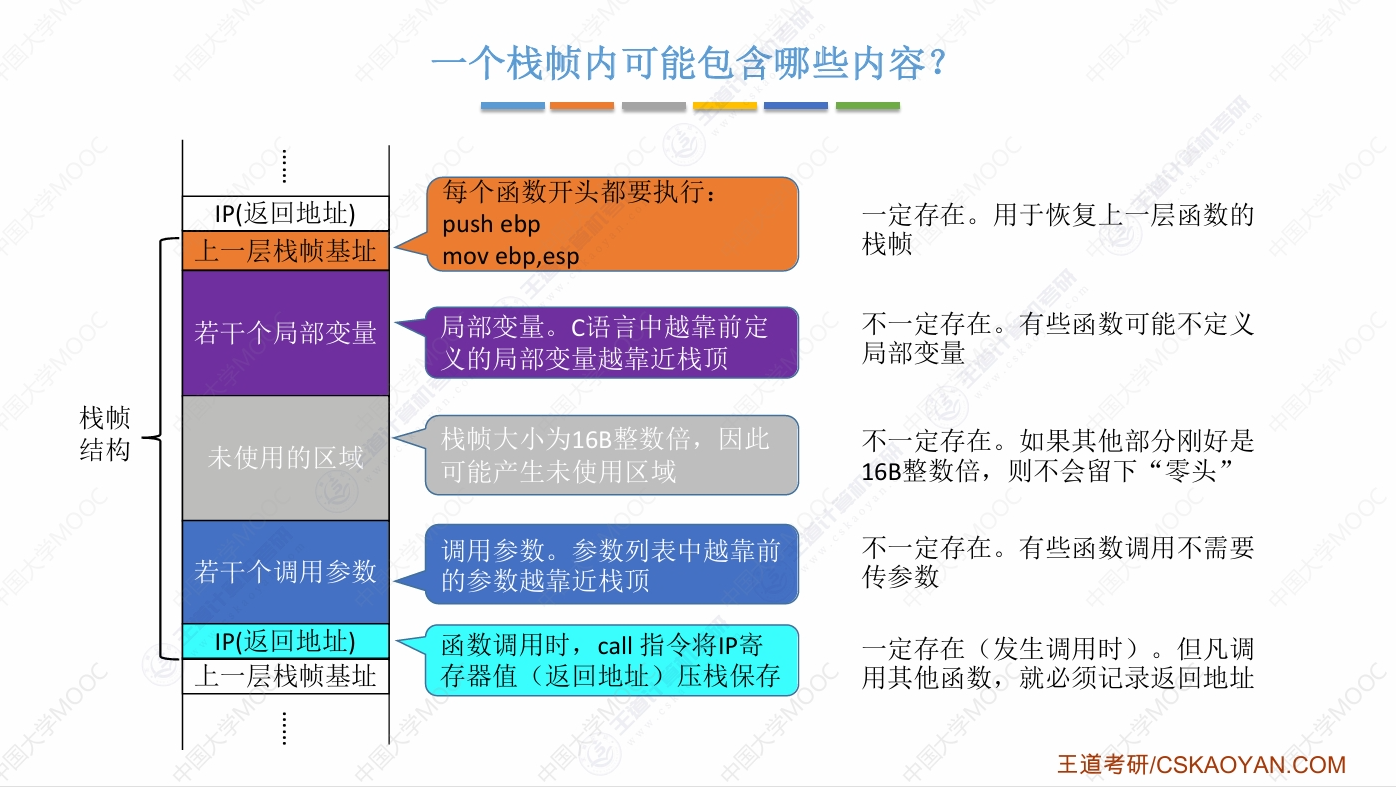

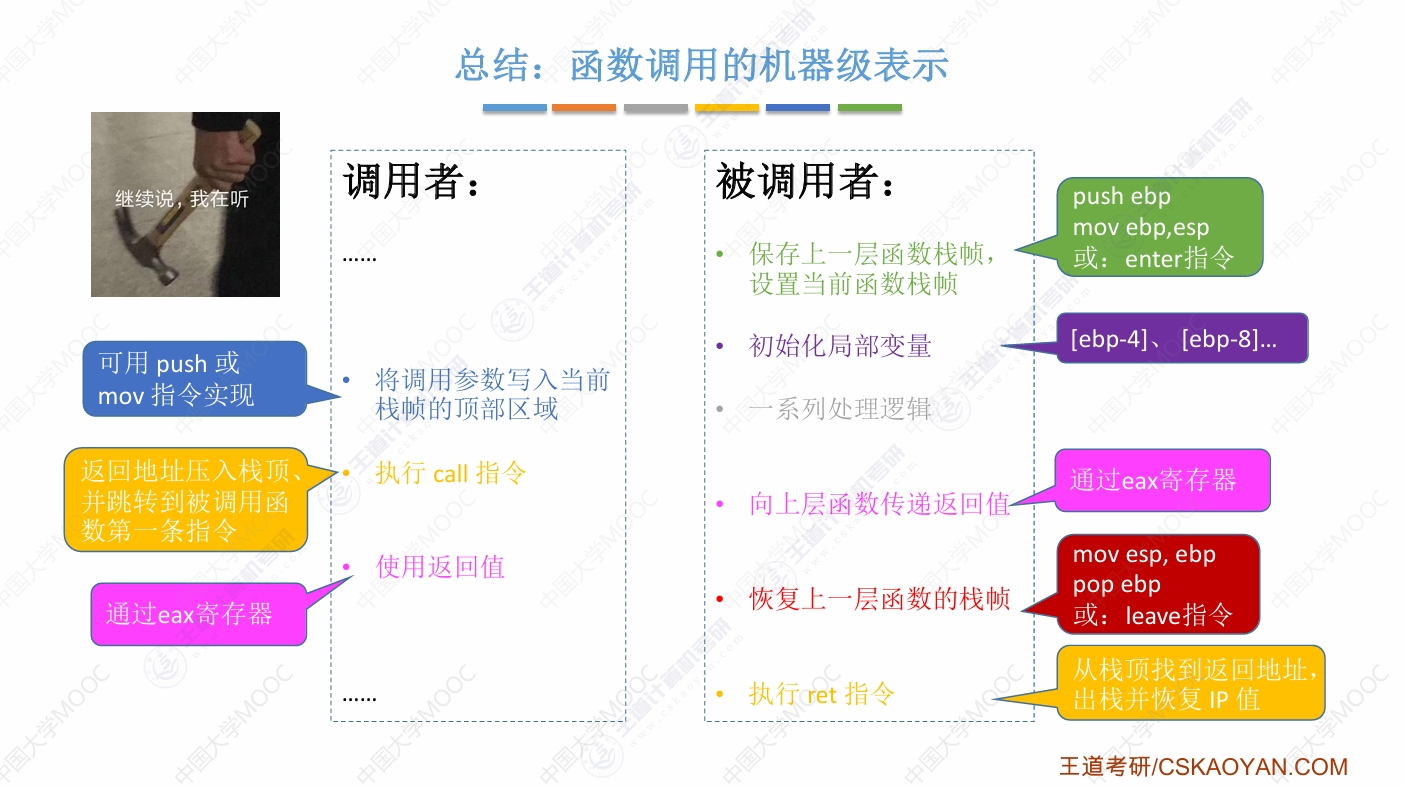

- x86处理器中,PC(程序计数器)通常被称为IP

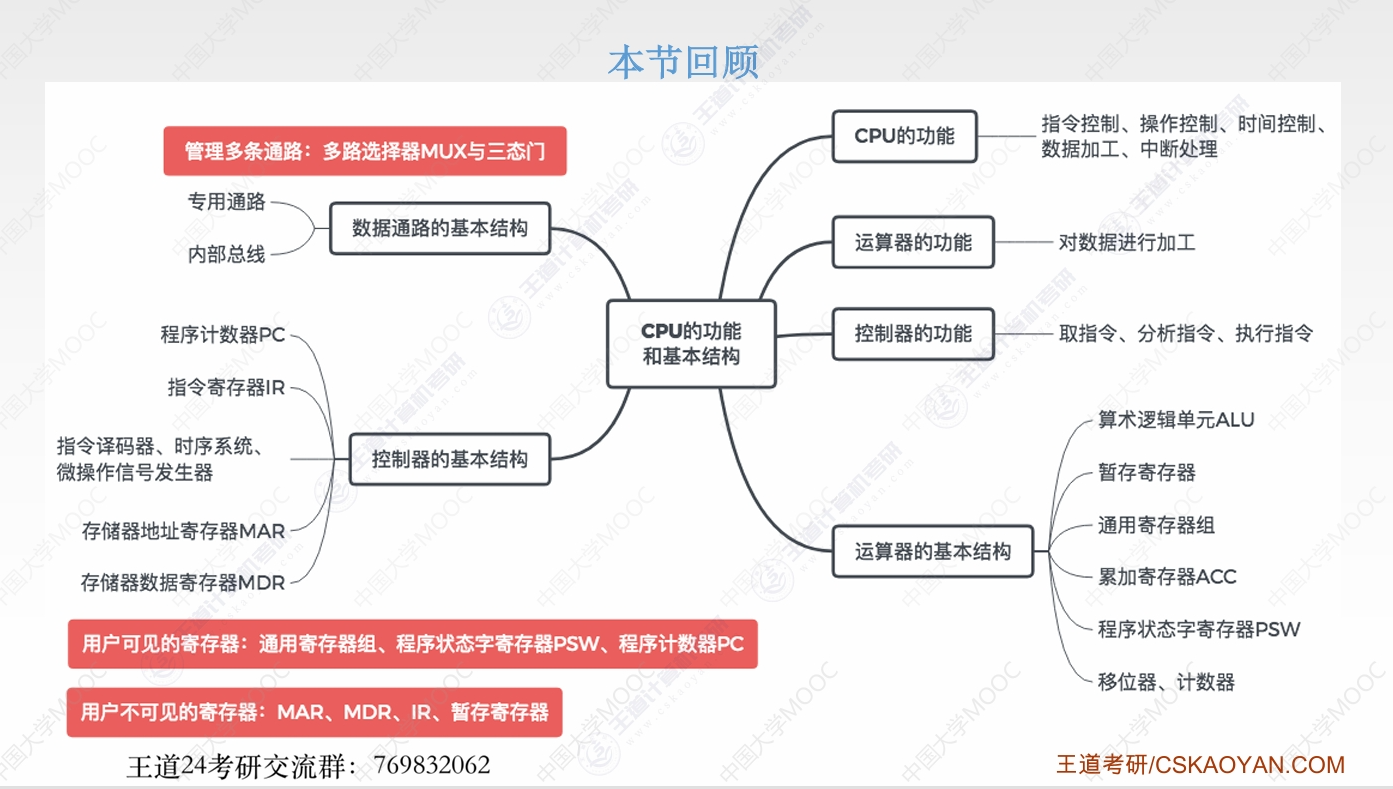

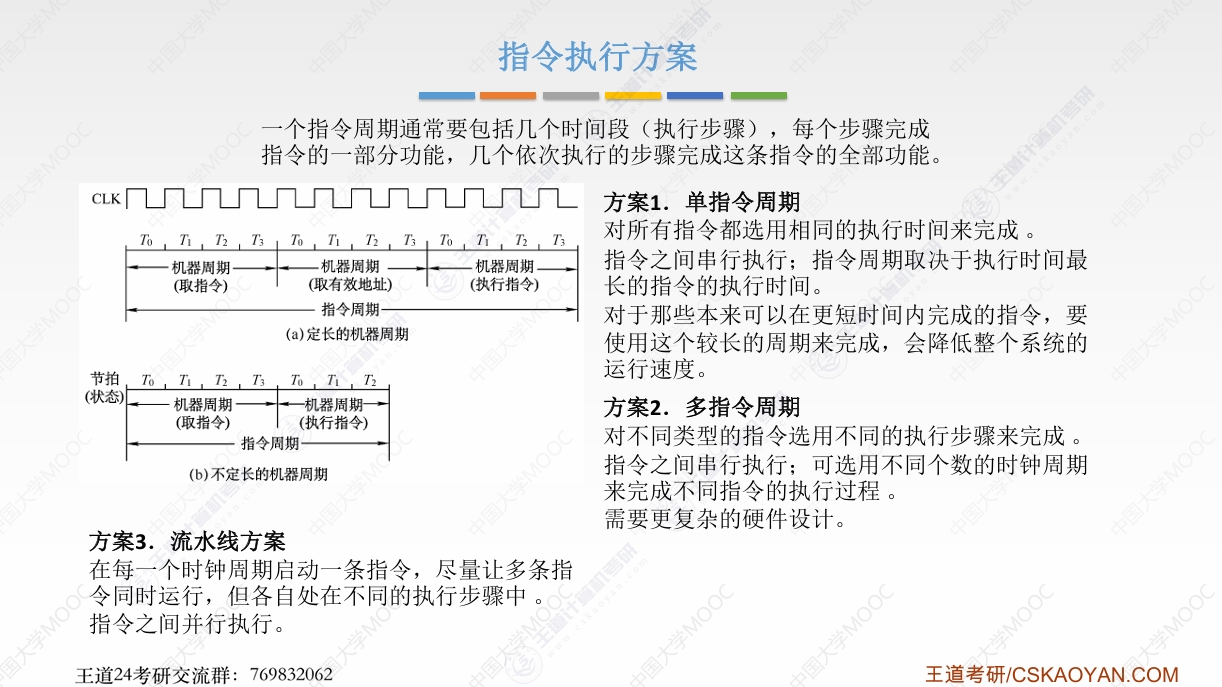

五丶中央处理器

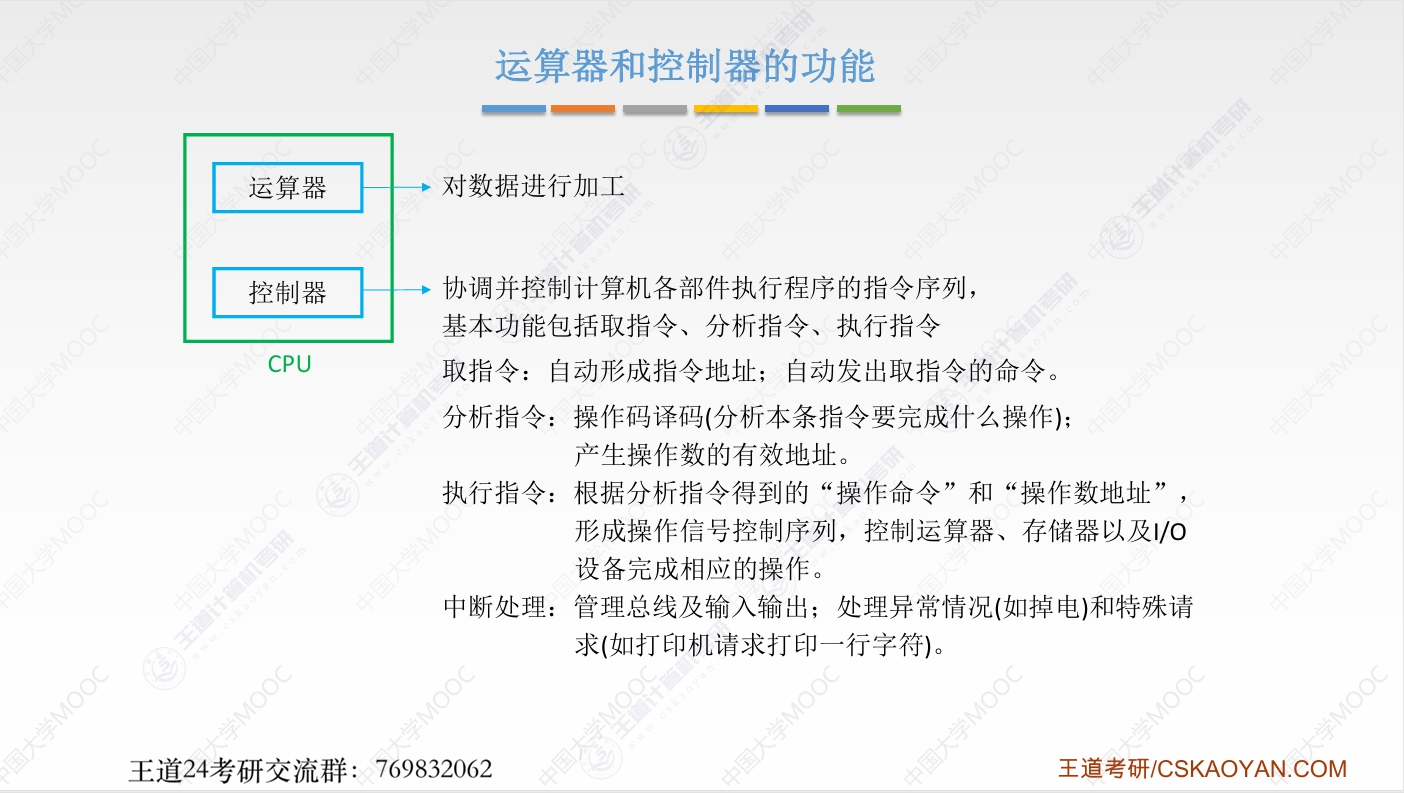

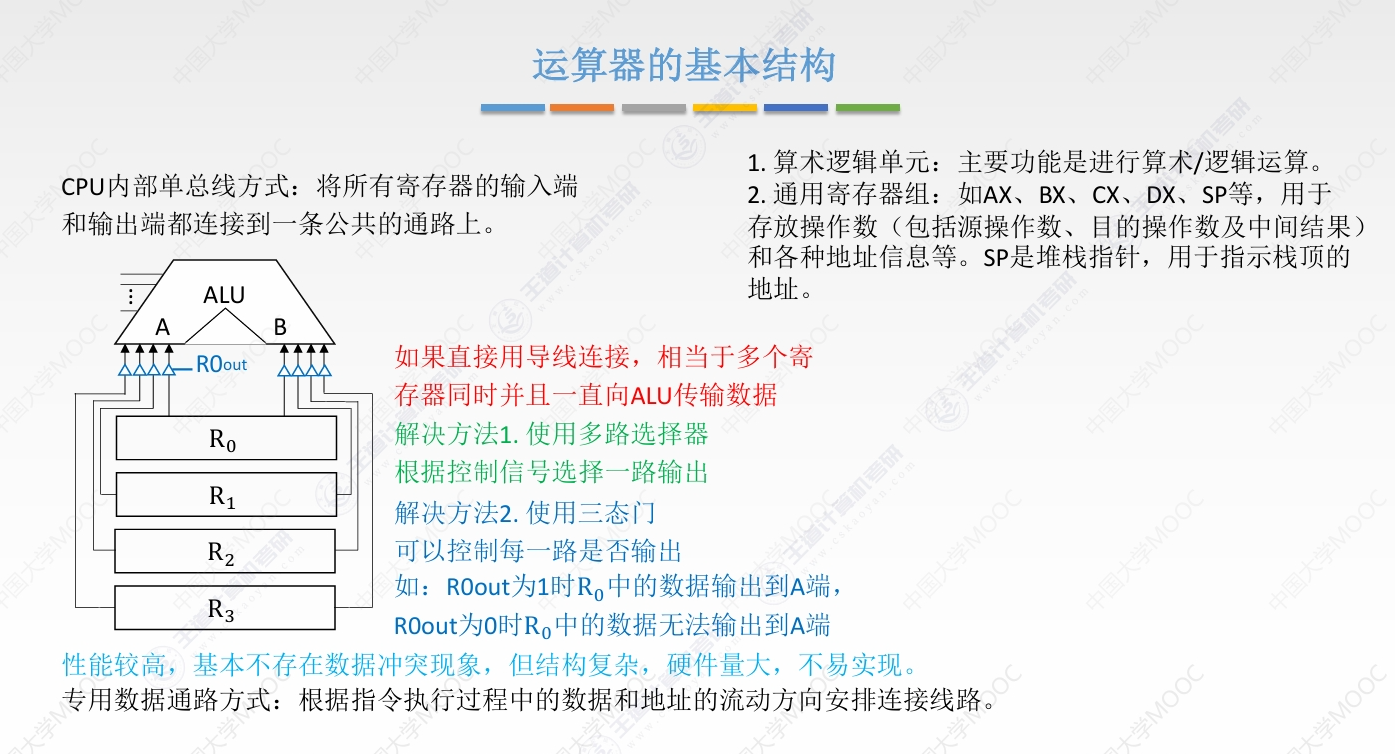

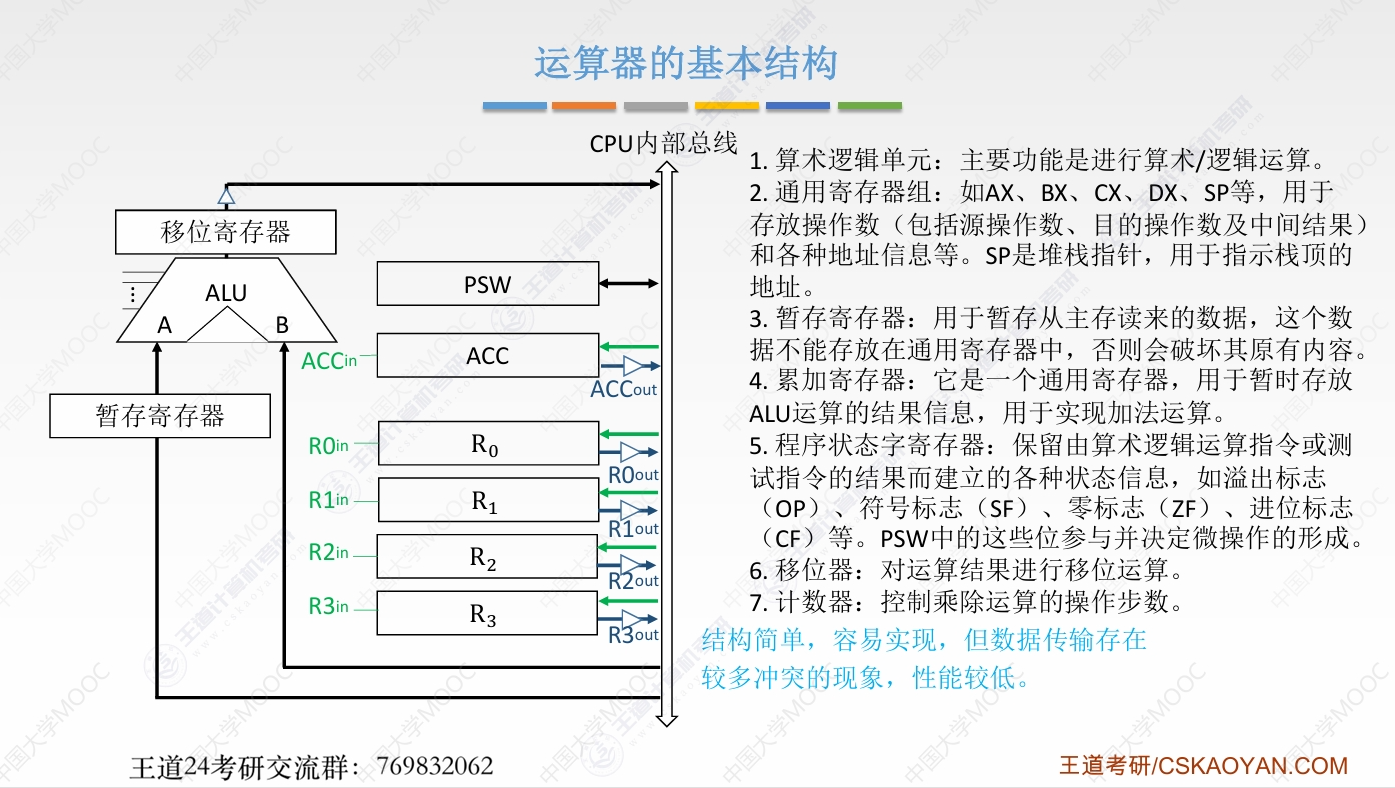

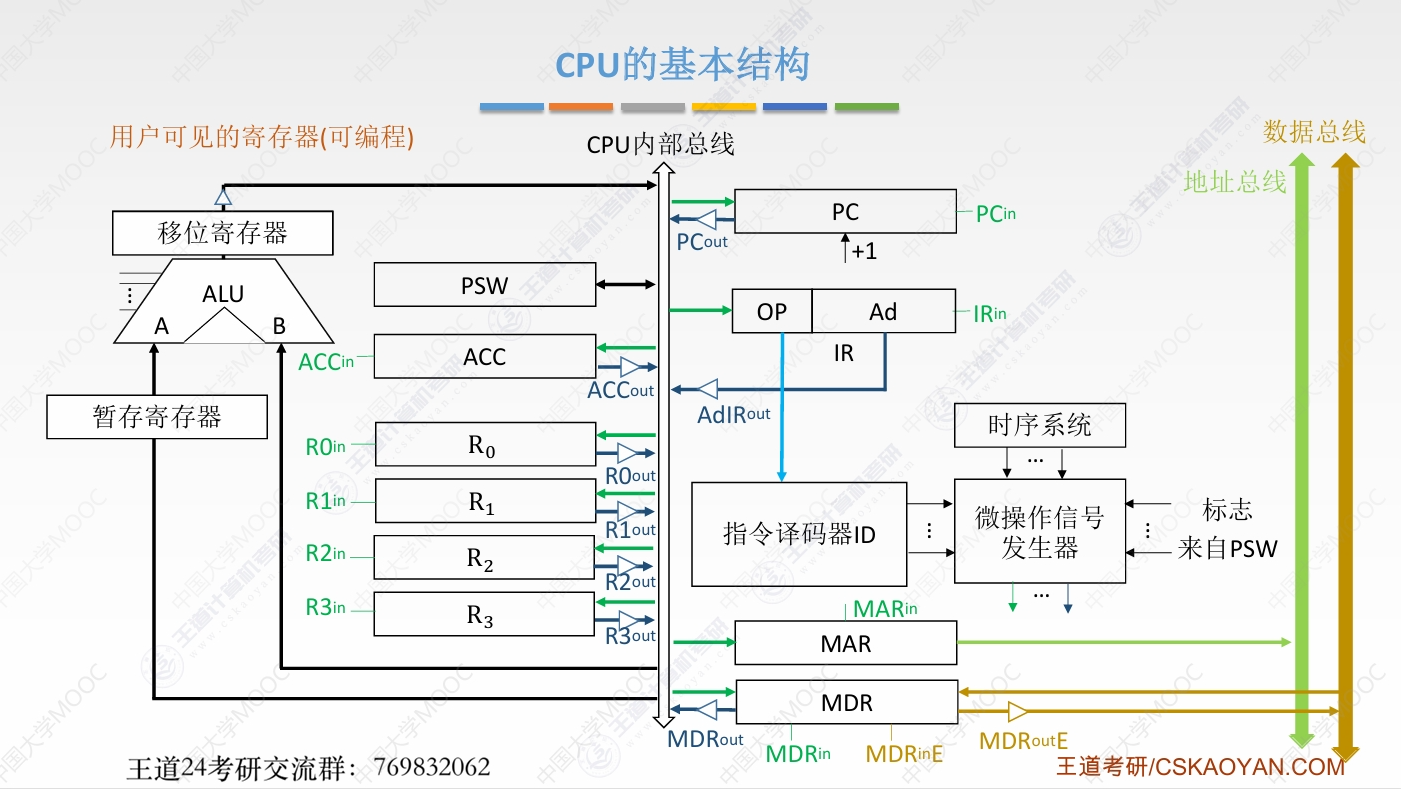

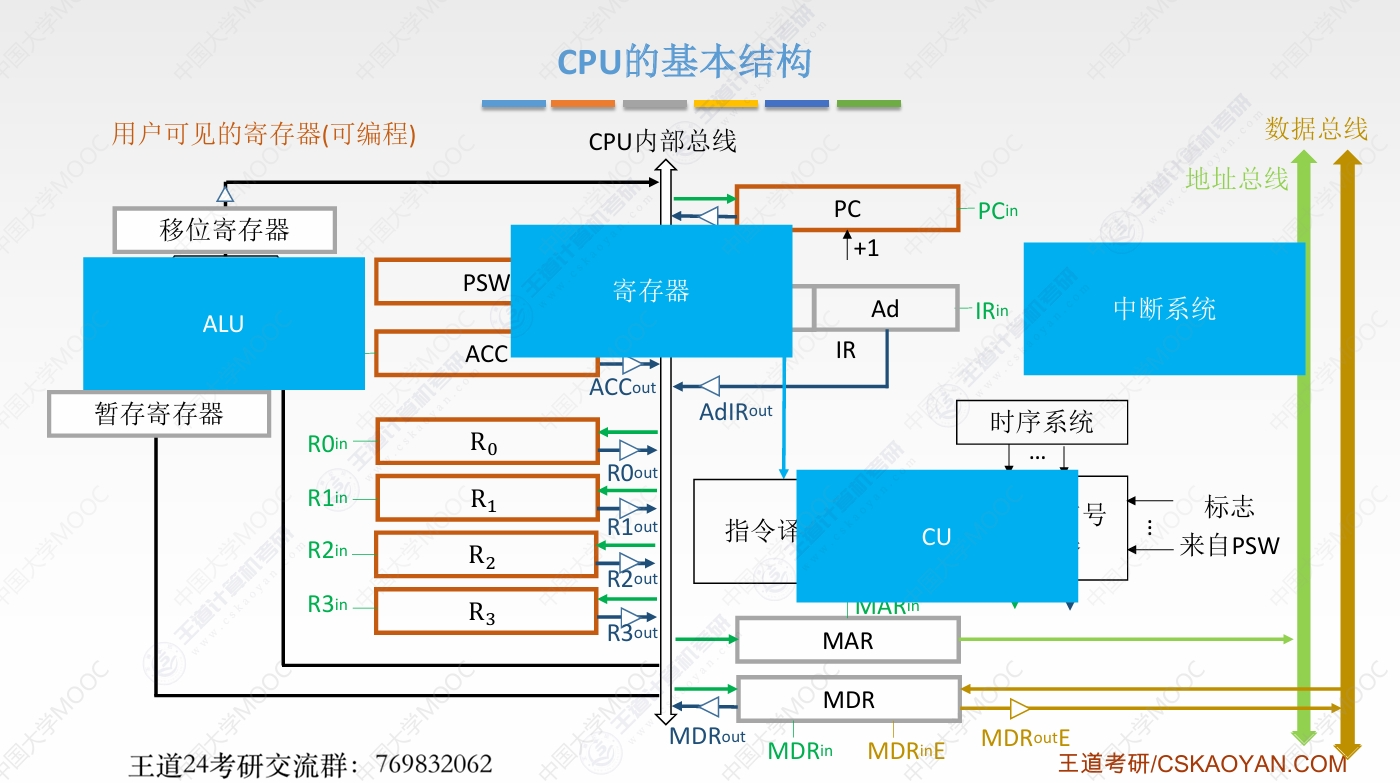

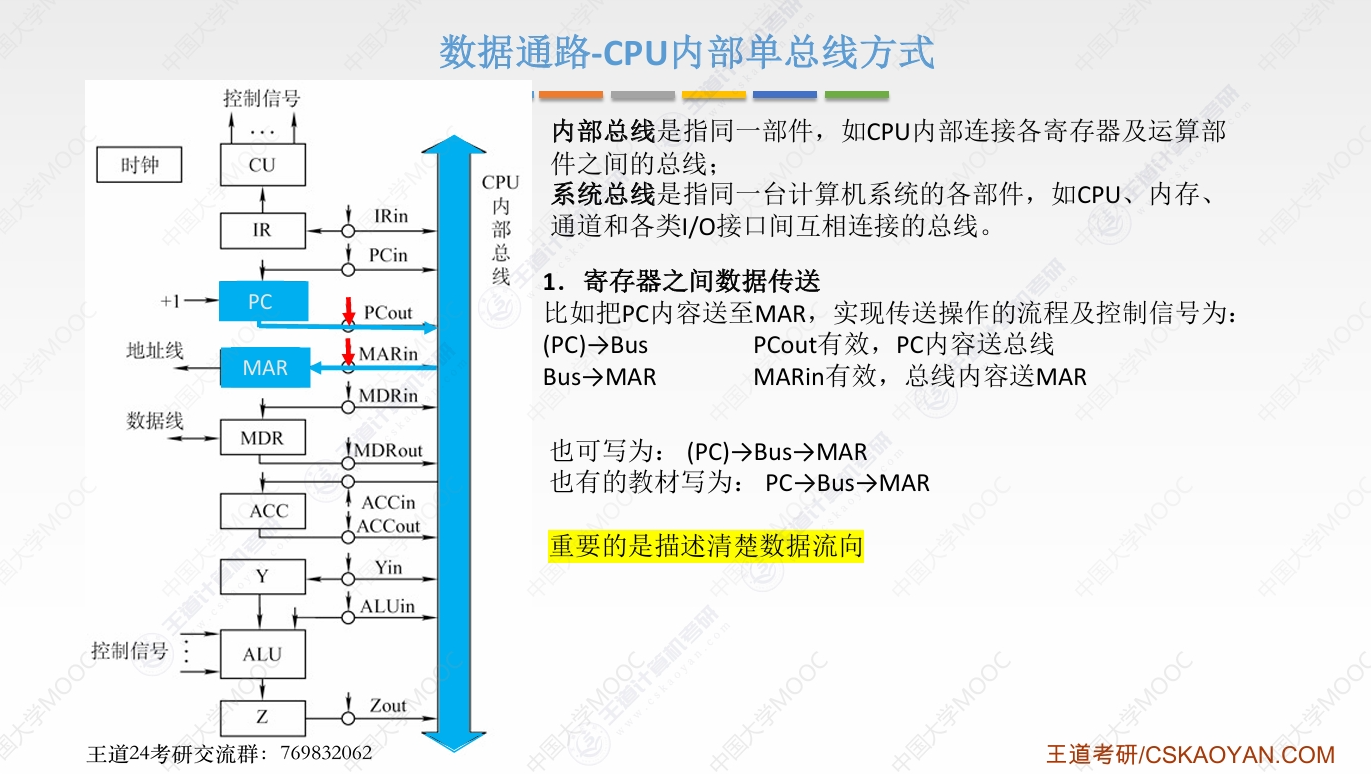

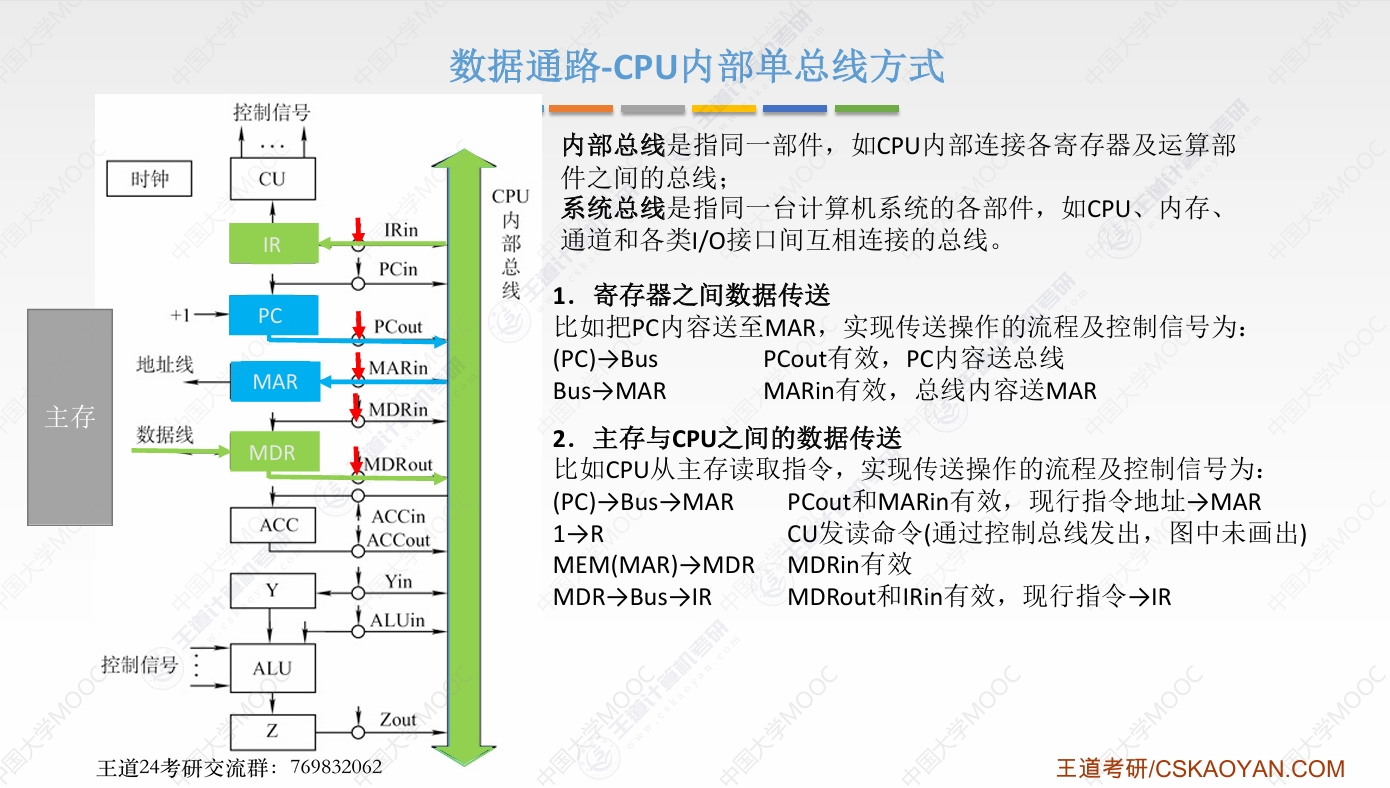

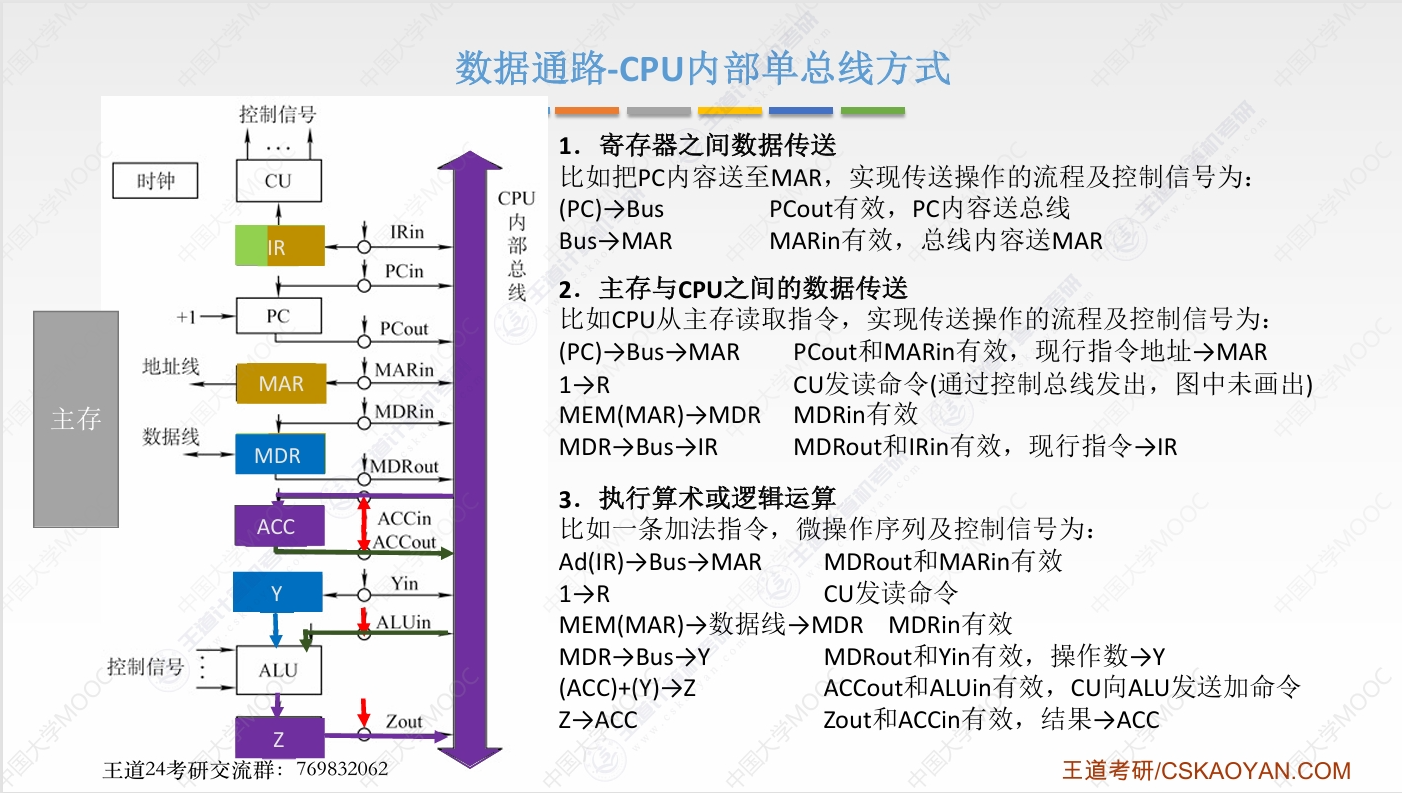

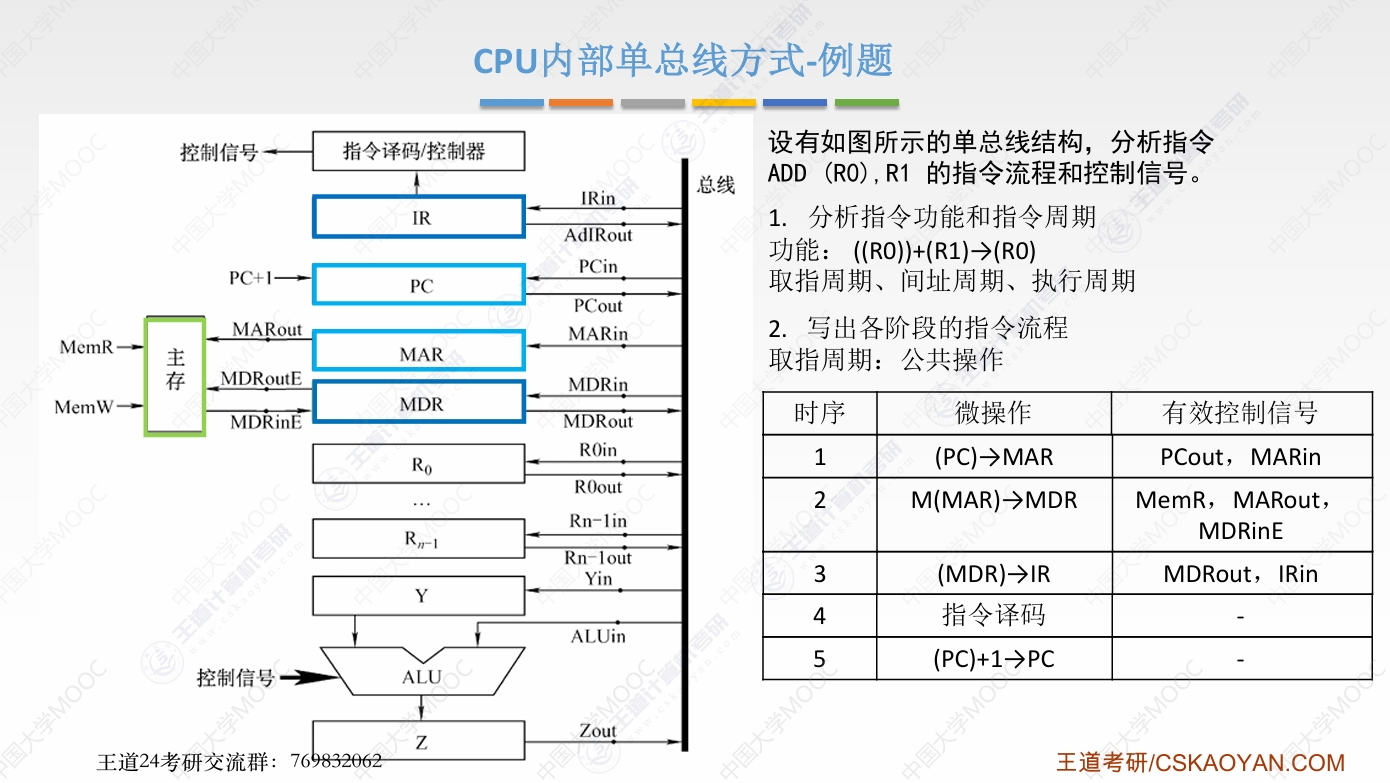

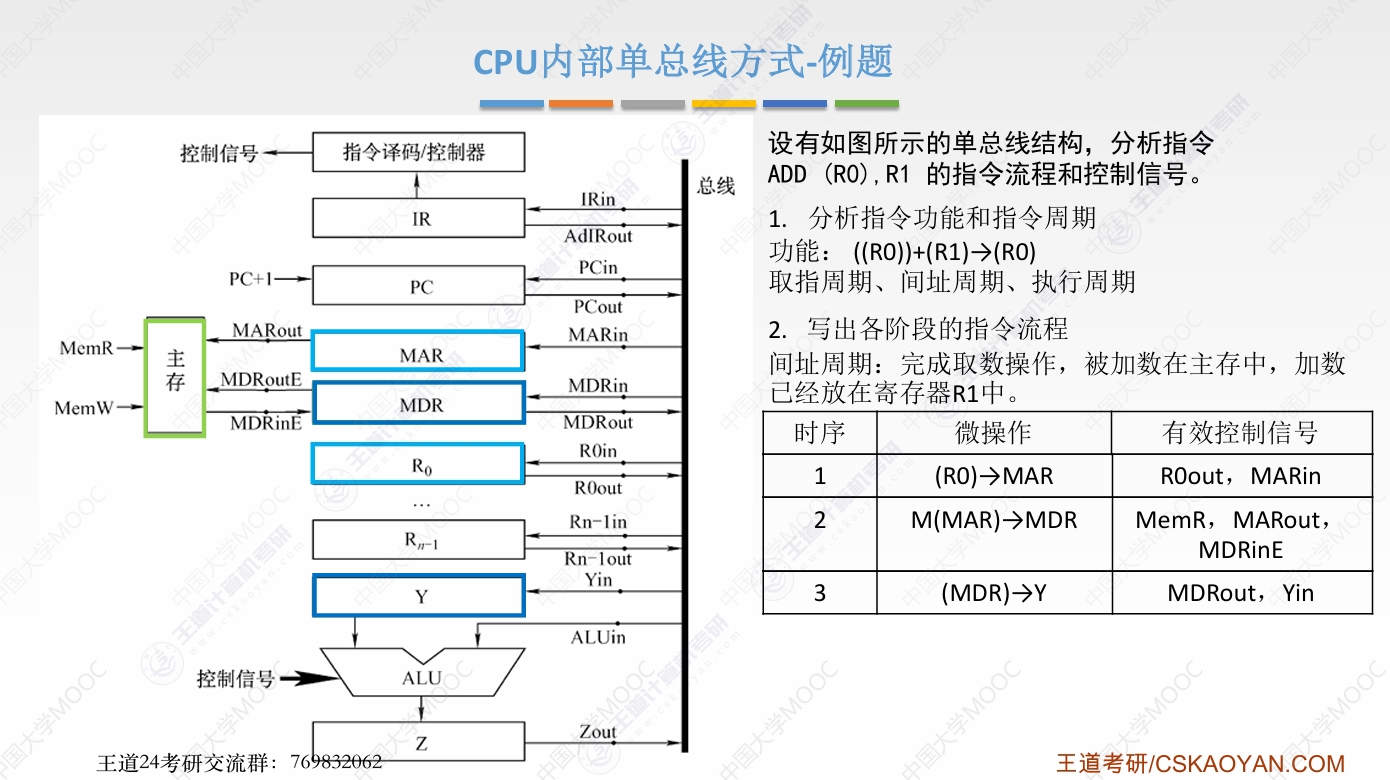

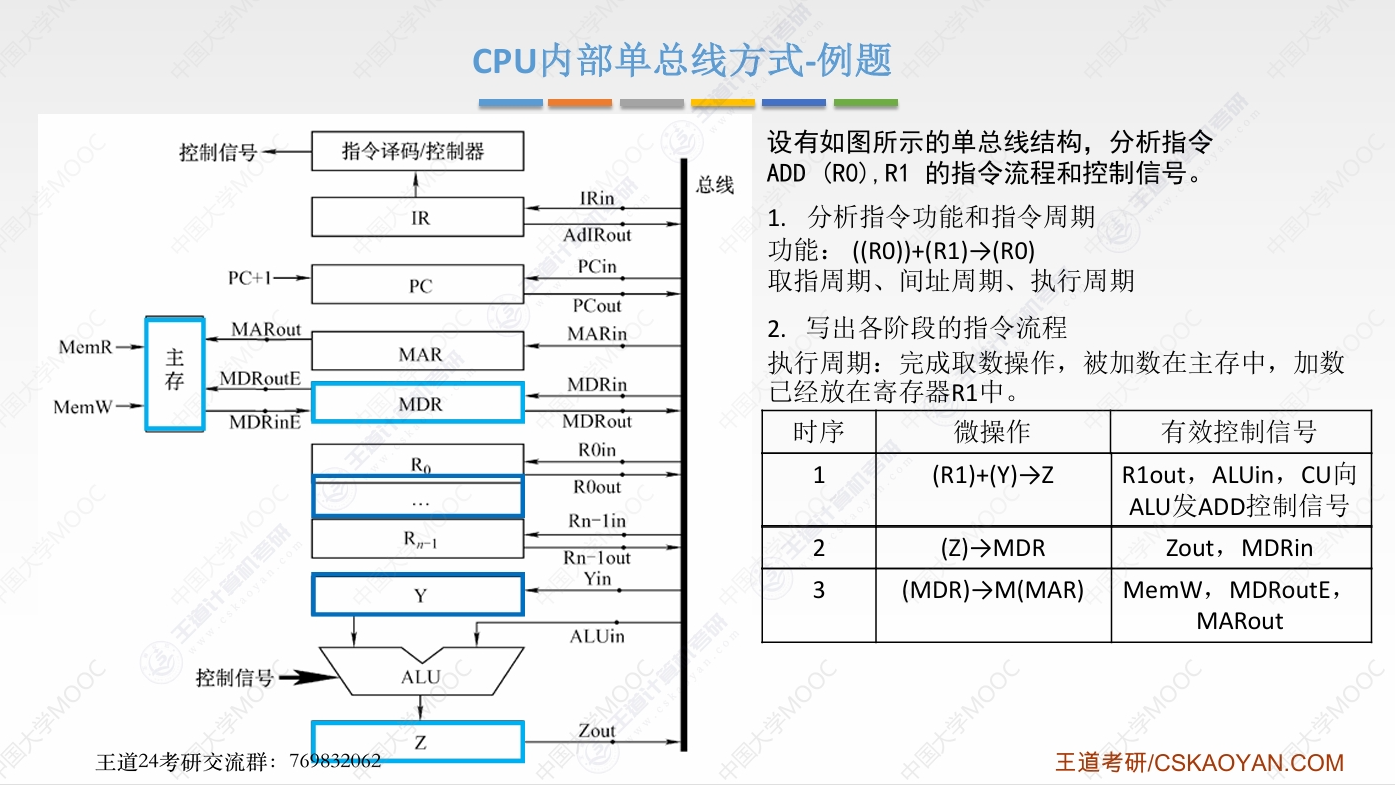

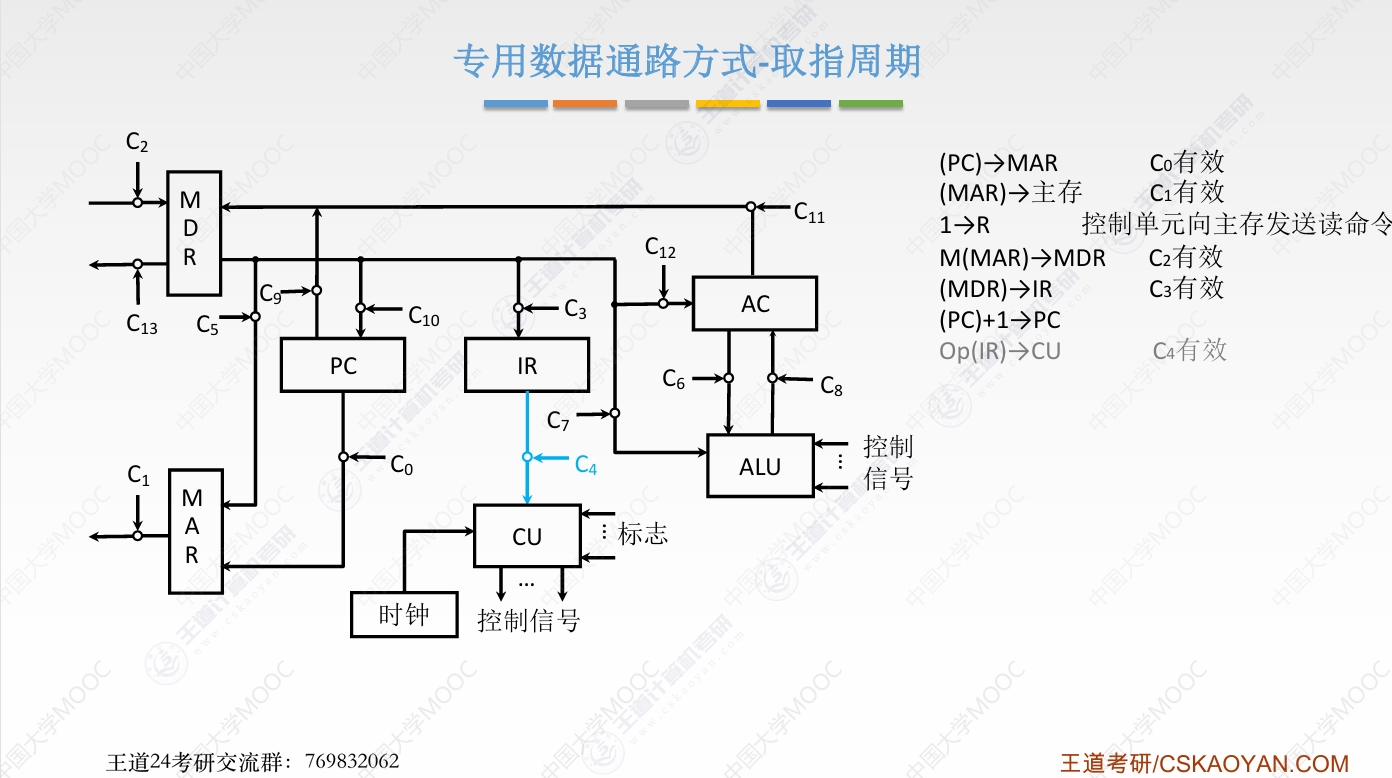

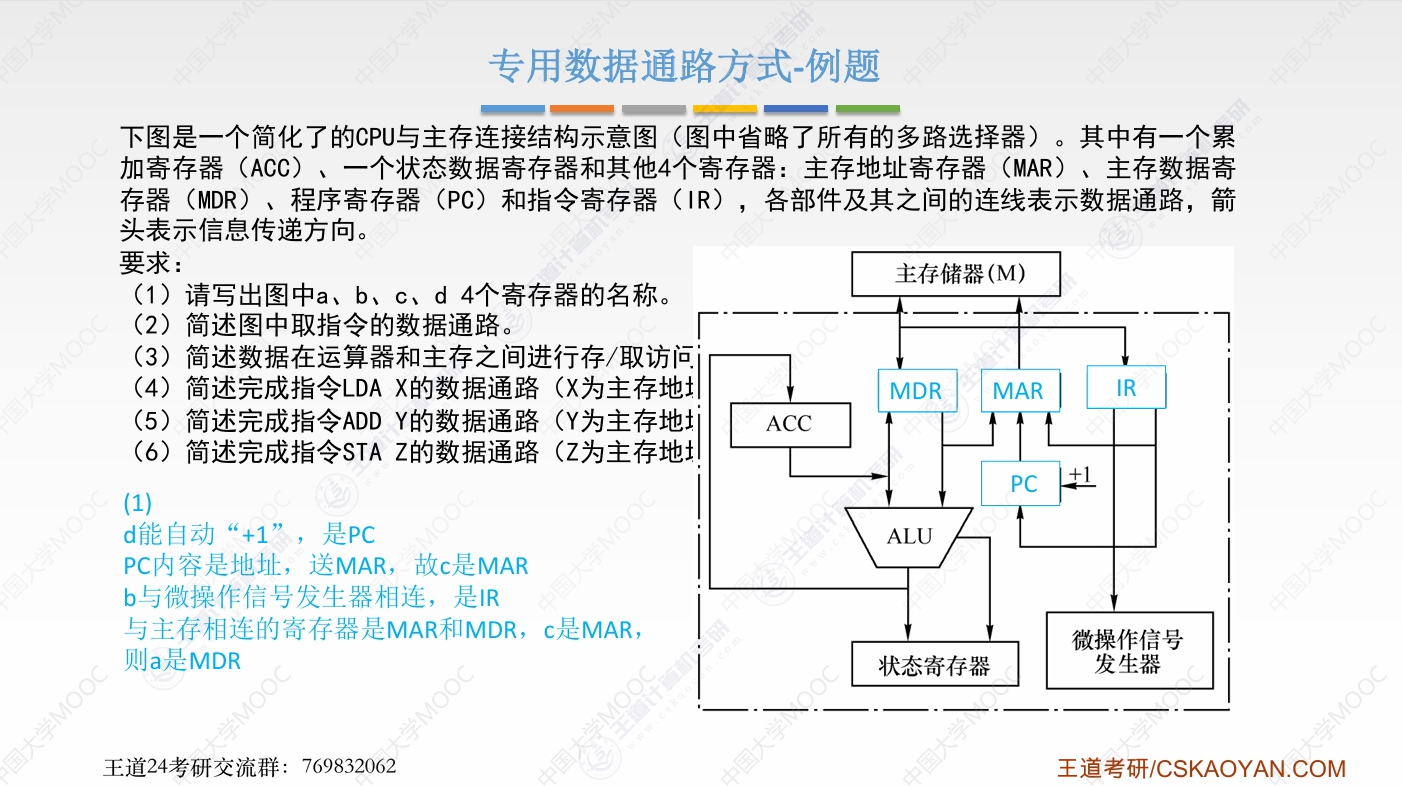

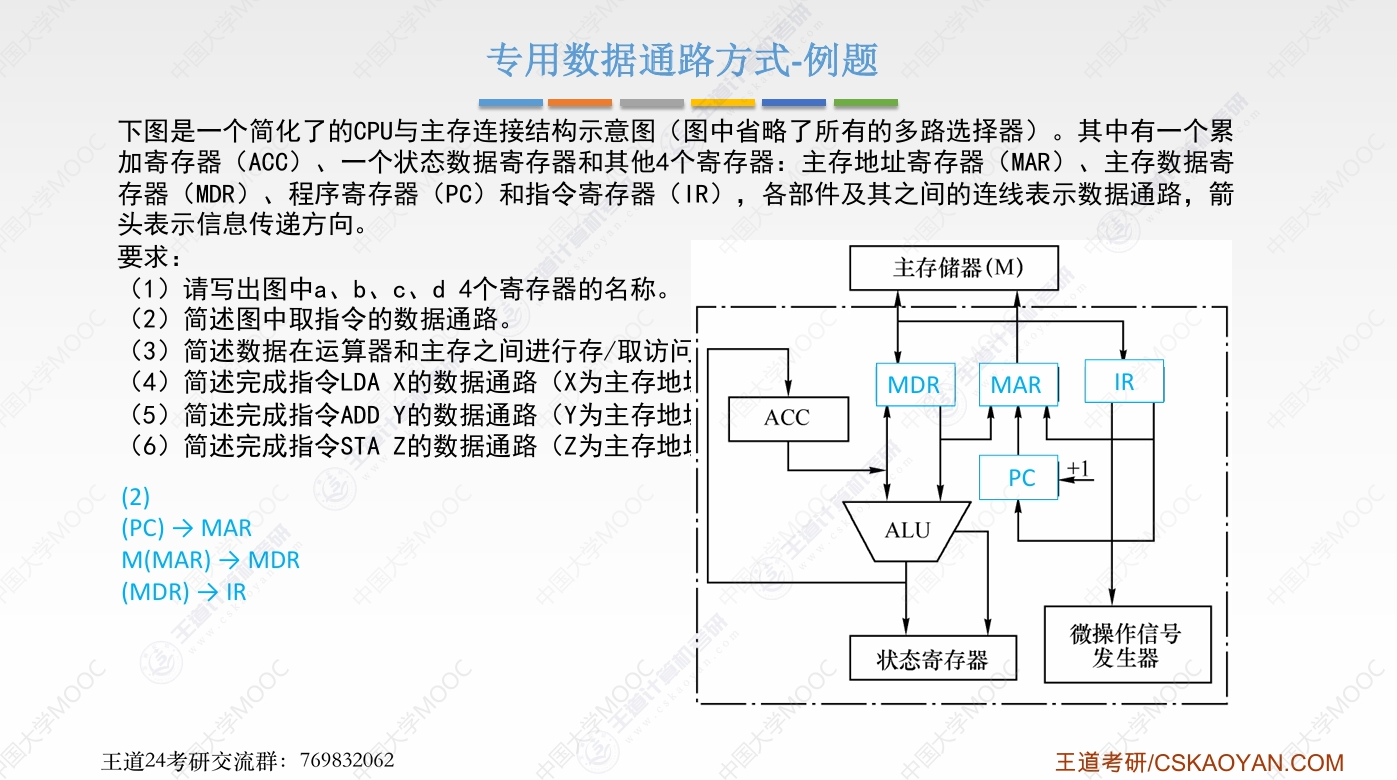

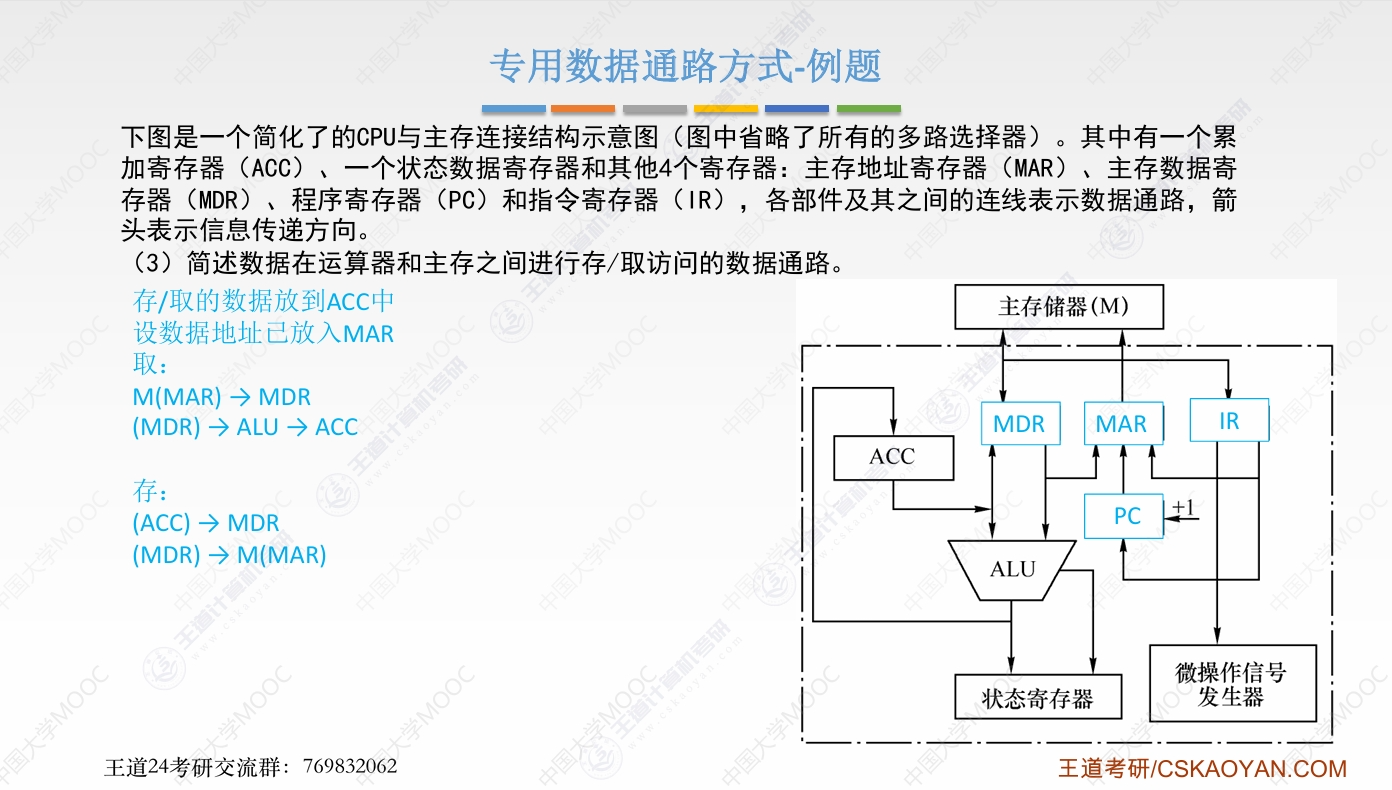

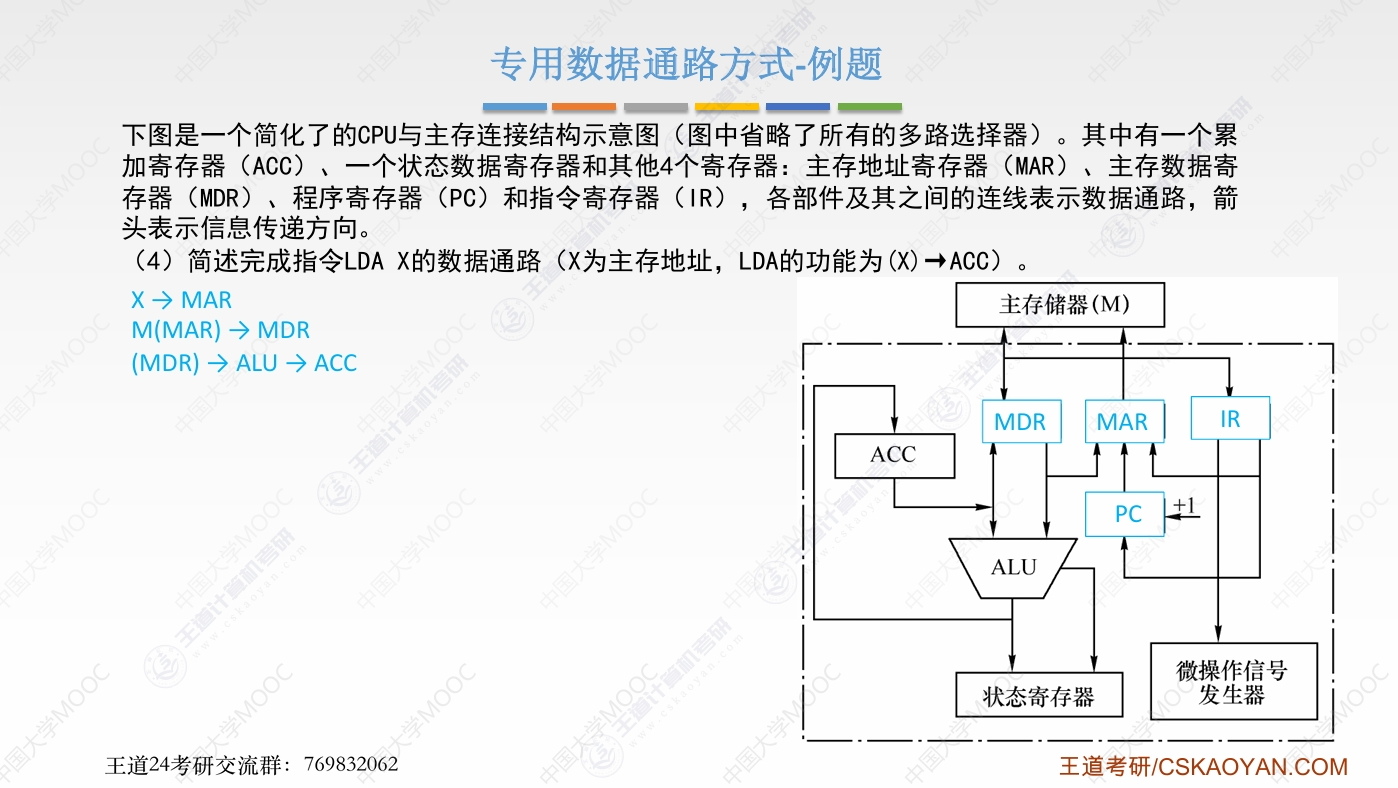

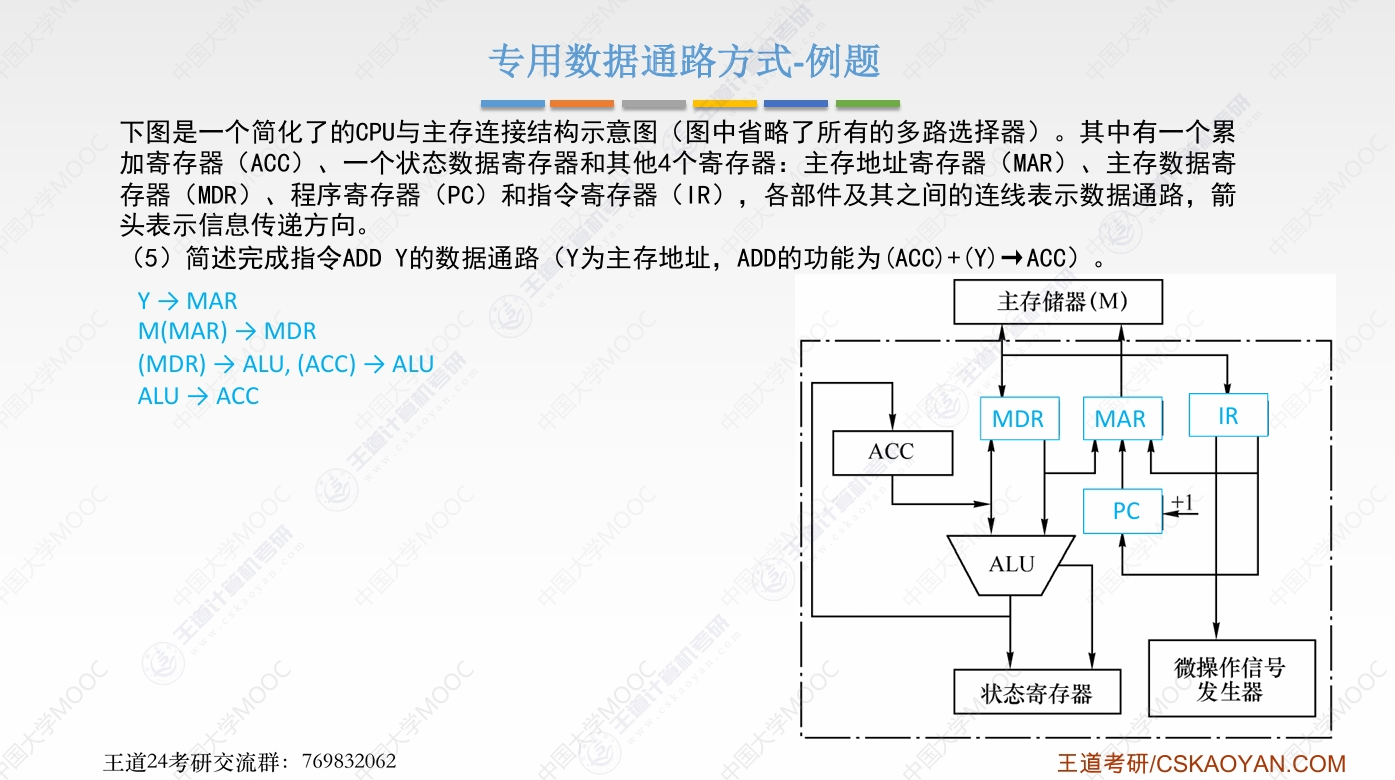

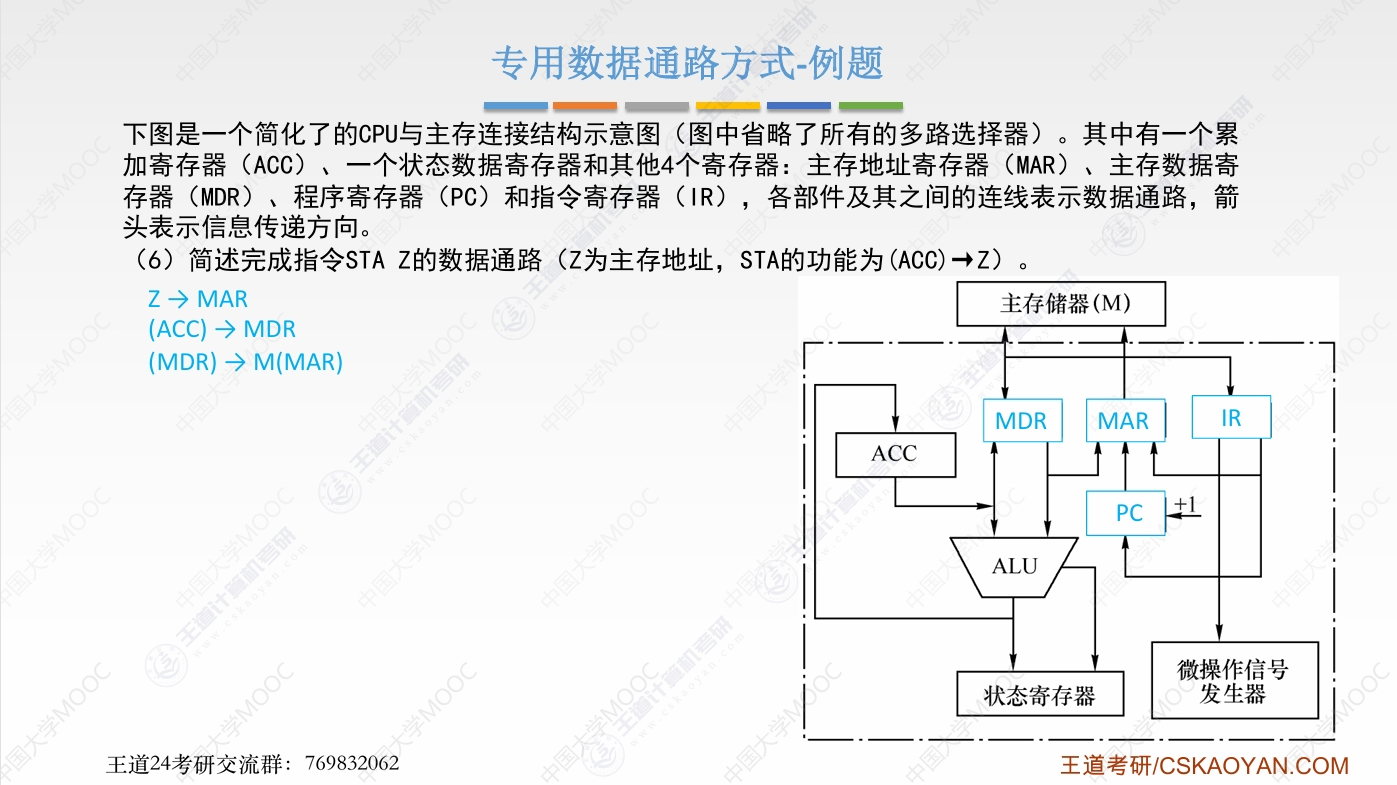

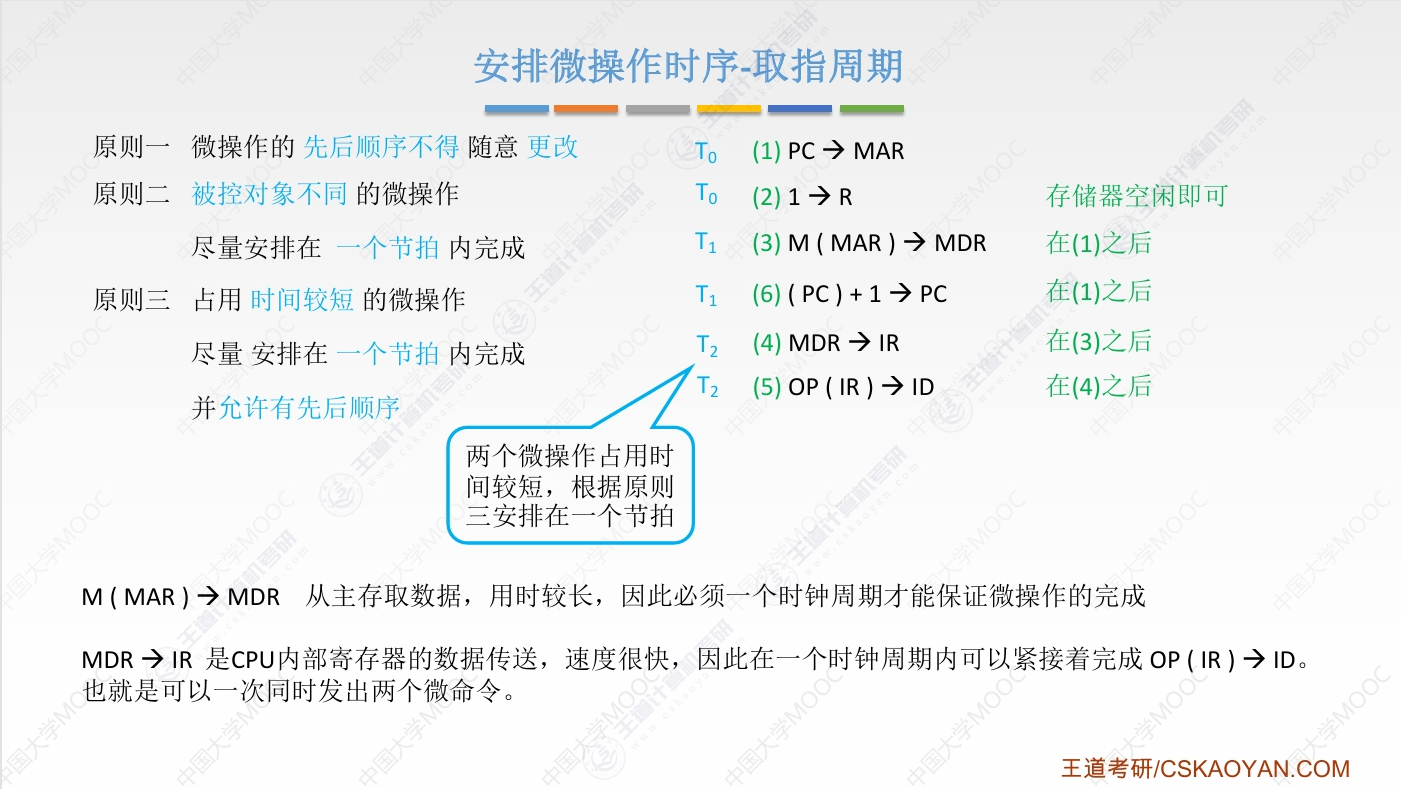

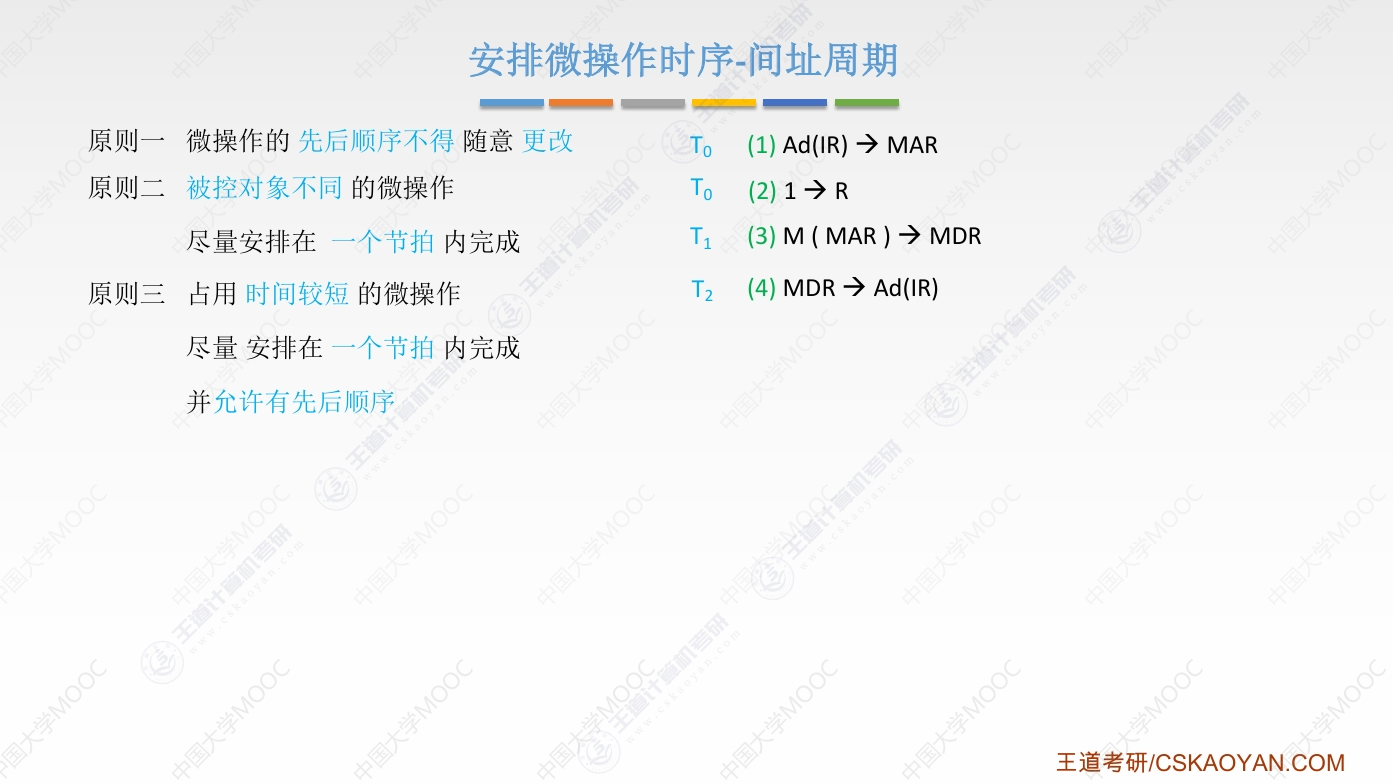

- 数据通路 : 数据在功能部件之间传送的路径

- 这里MEM指的是内存

- 这里Y和Z指的是暂存寄存器

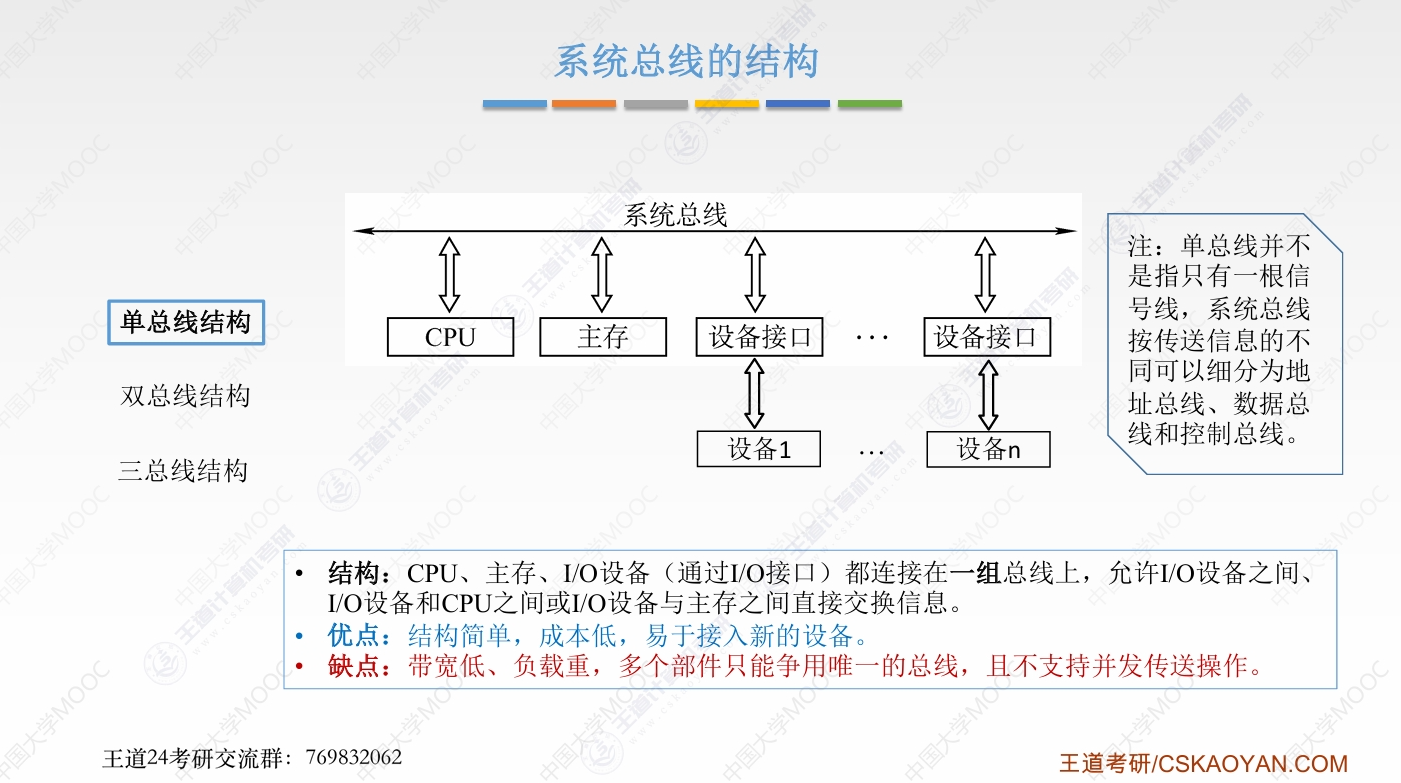

- 单总线结构,ALU需要配合暂存寄存器一起使用

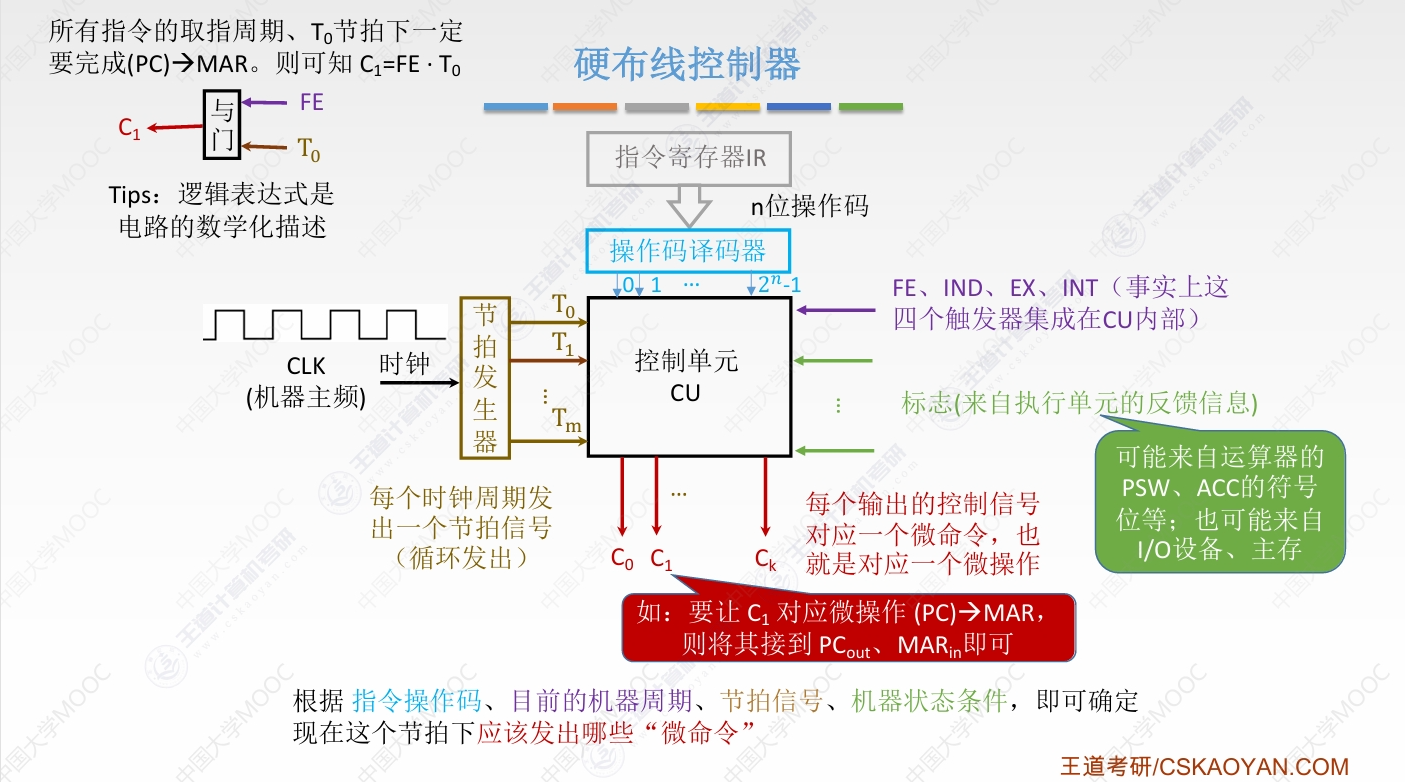

- 操作码译码器 : 根据操作码输出对应的有效信号(如0100对应有效信号4)

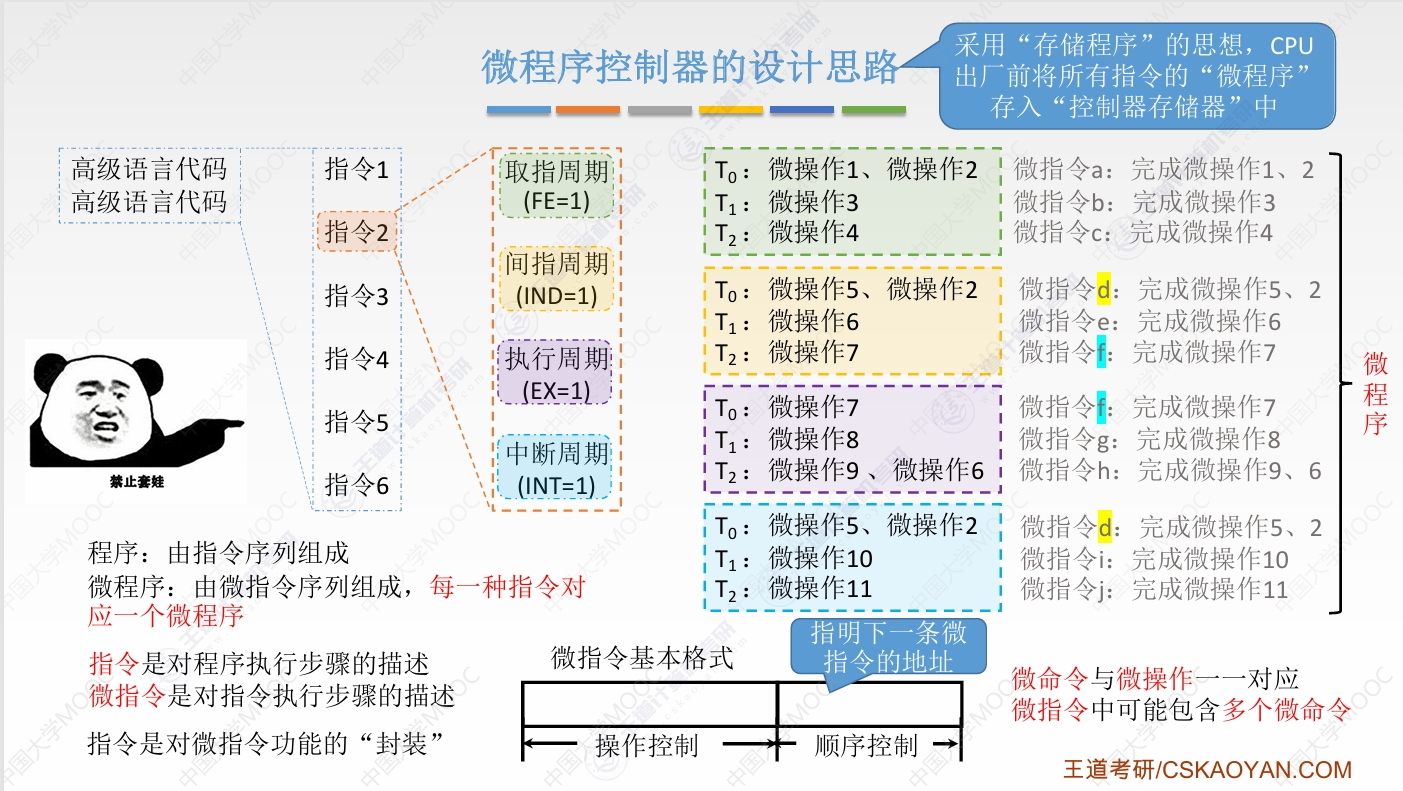

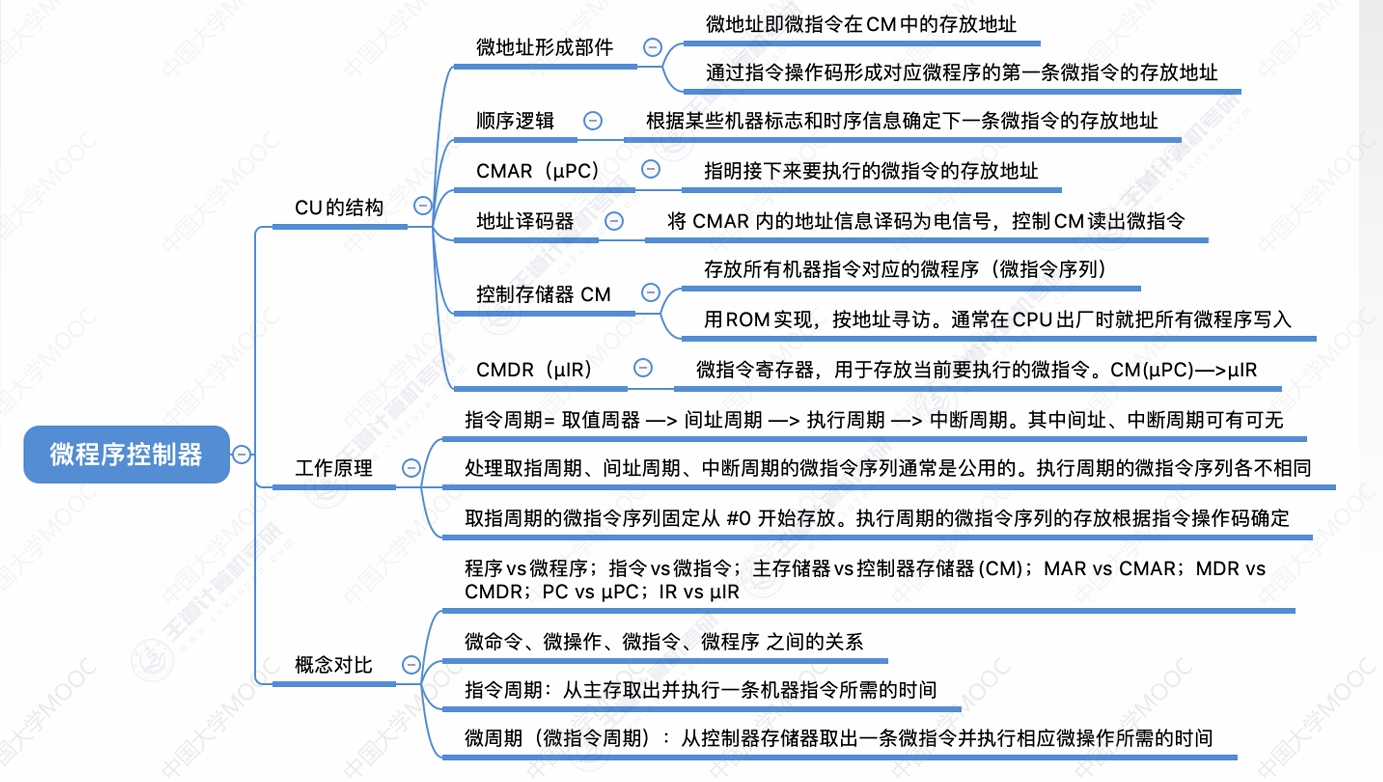

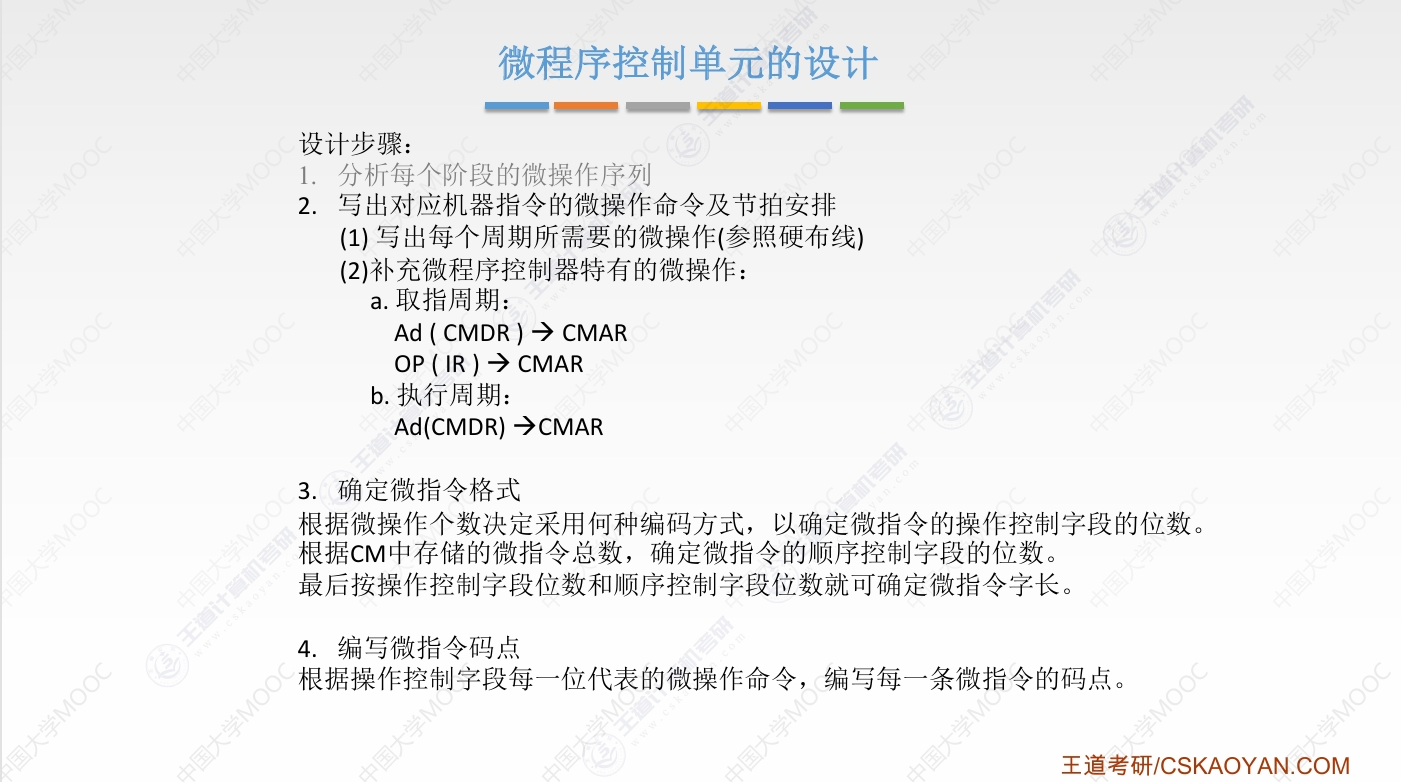

- 这里绿字中的微程序更偏向于微程序段这种概念

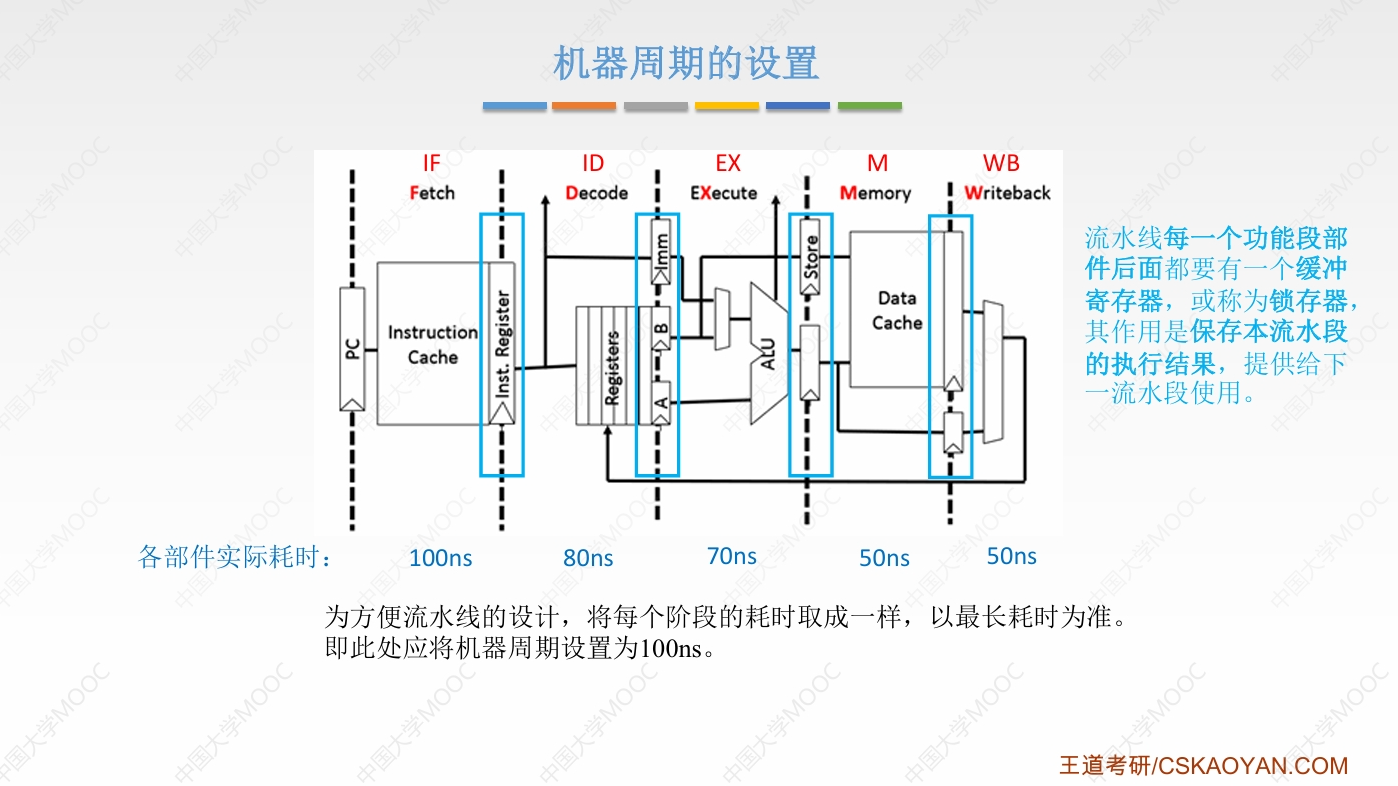

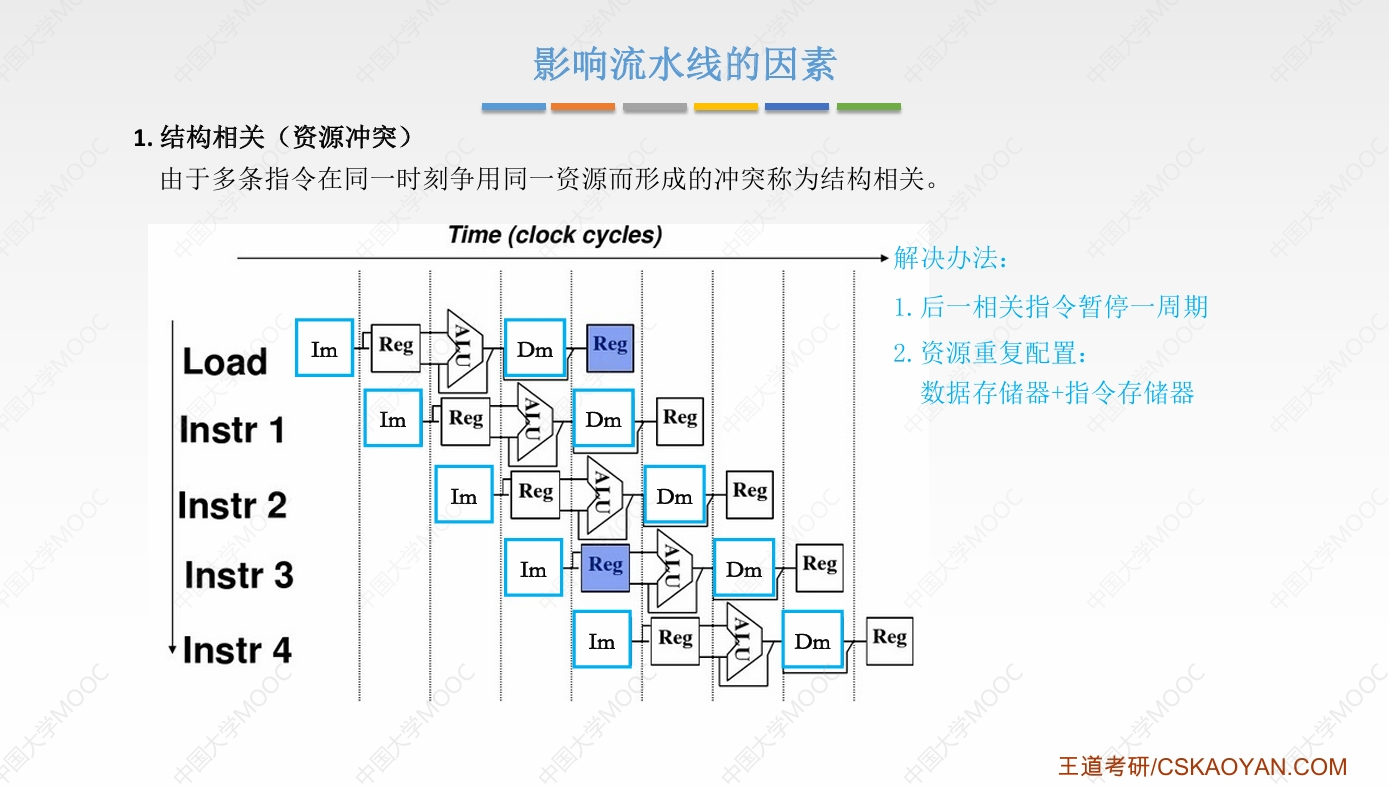

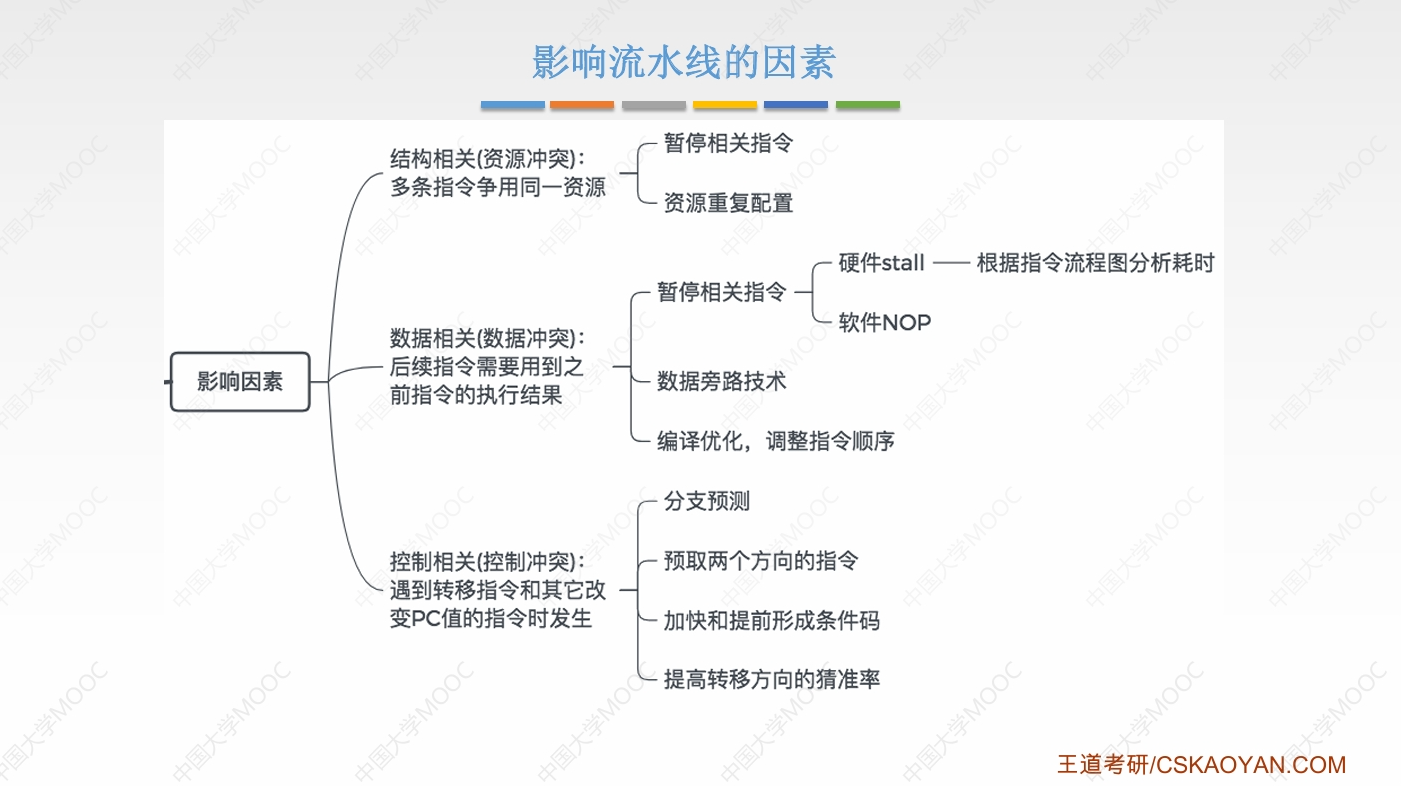

- 资源重复偏置 : 将一个完整的存储器分成专门存储指令的存储体和专门存储数据的存储体

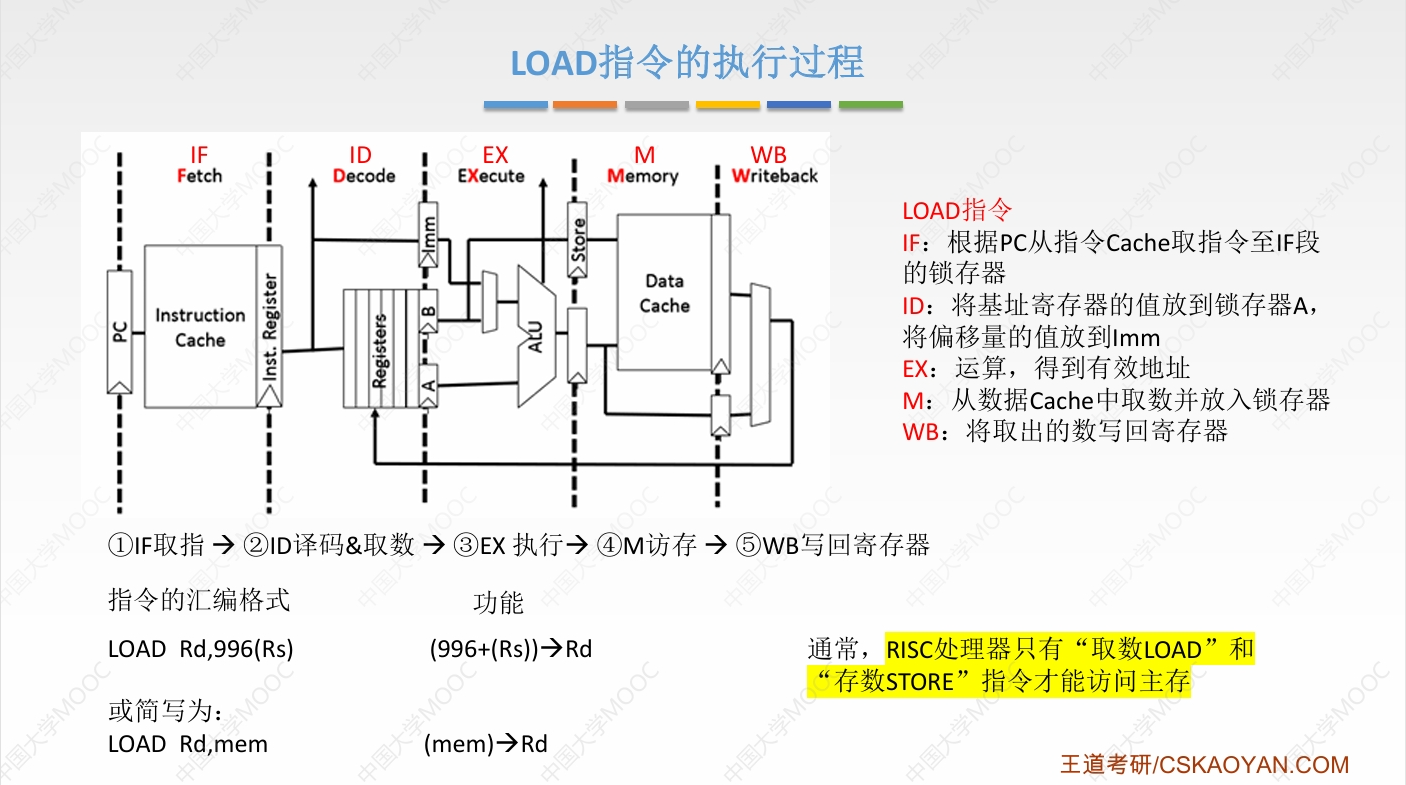

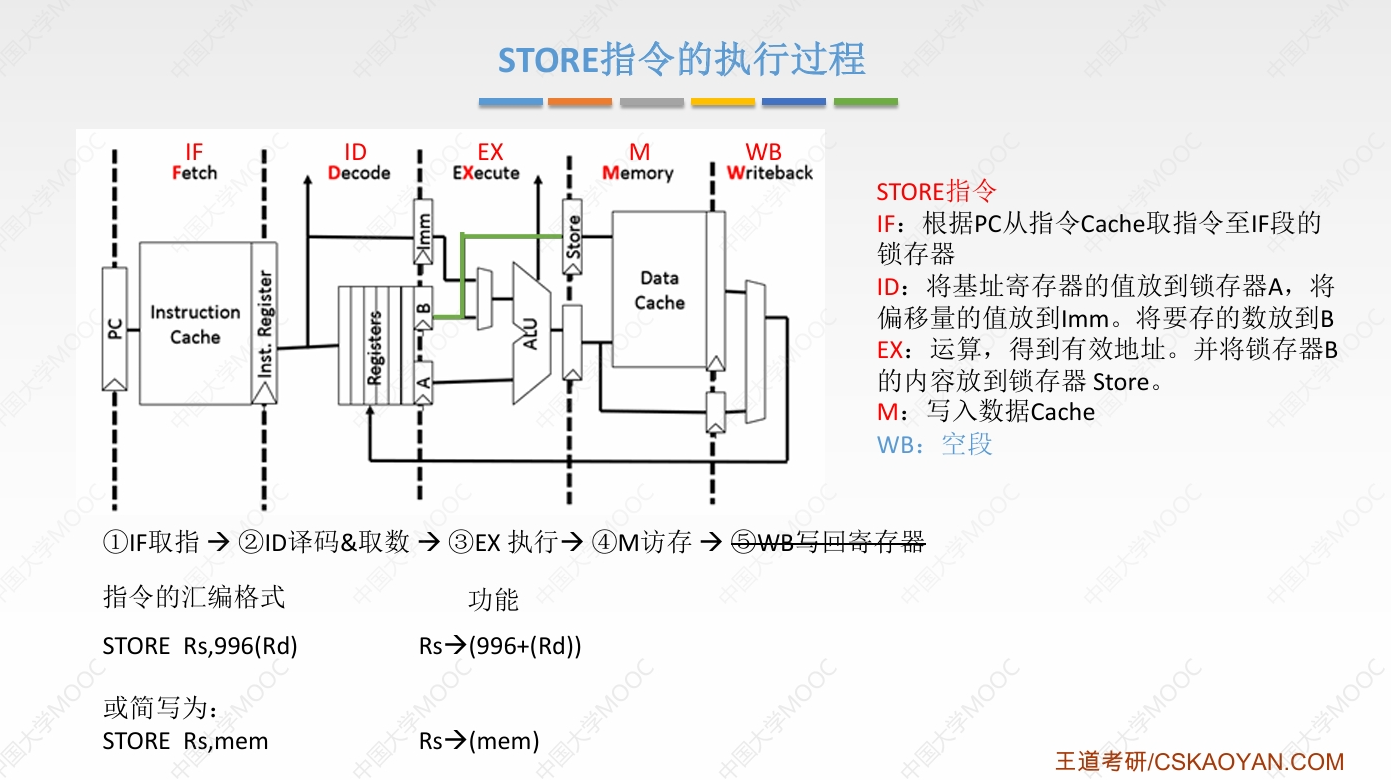

- imm寄存器用来存放立即数

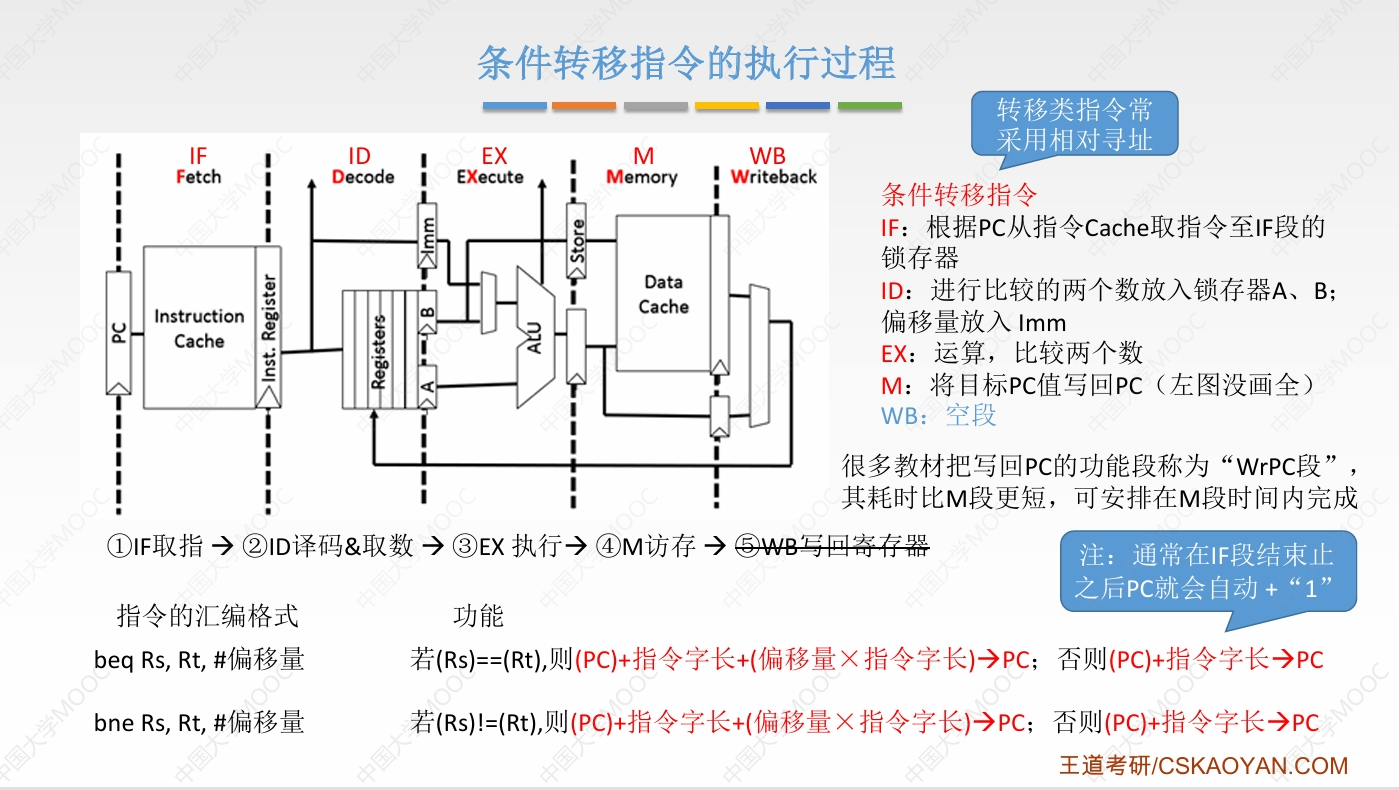

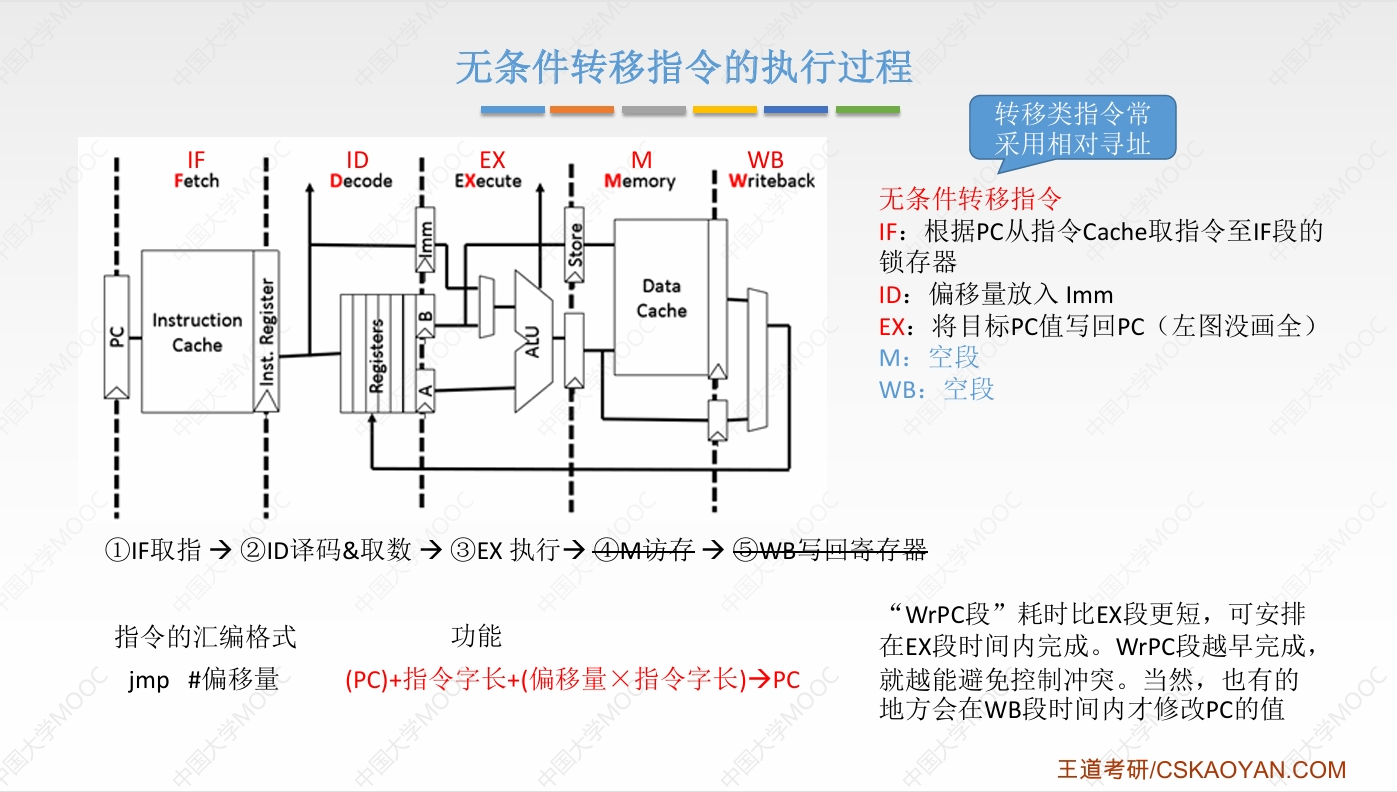

- (PC)+指令字长=PC+1

- (PC)+指令字长+(偏移量×指令字长)=从PC+1那个位置再往下偏移量个指令

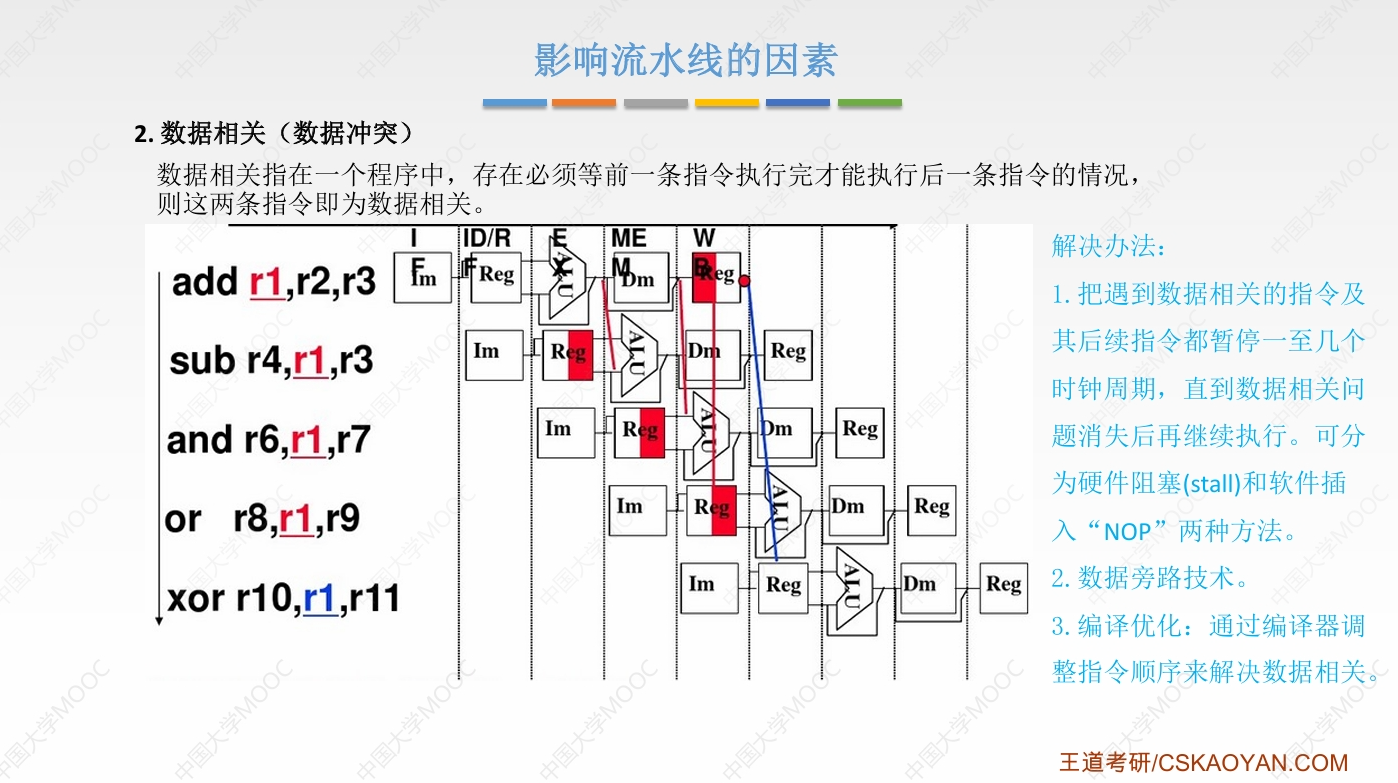

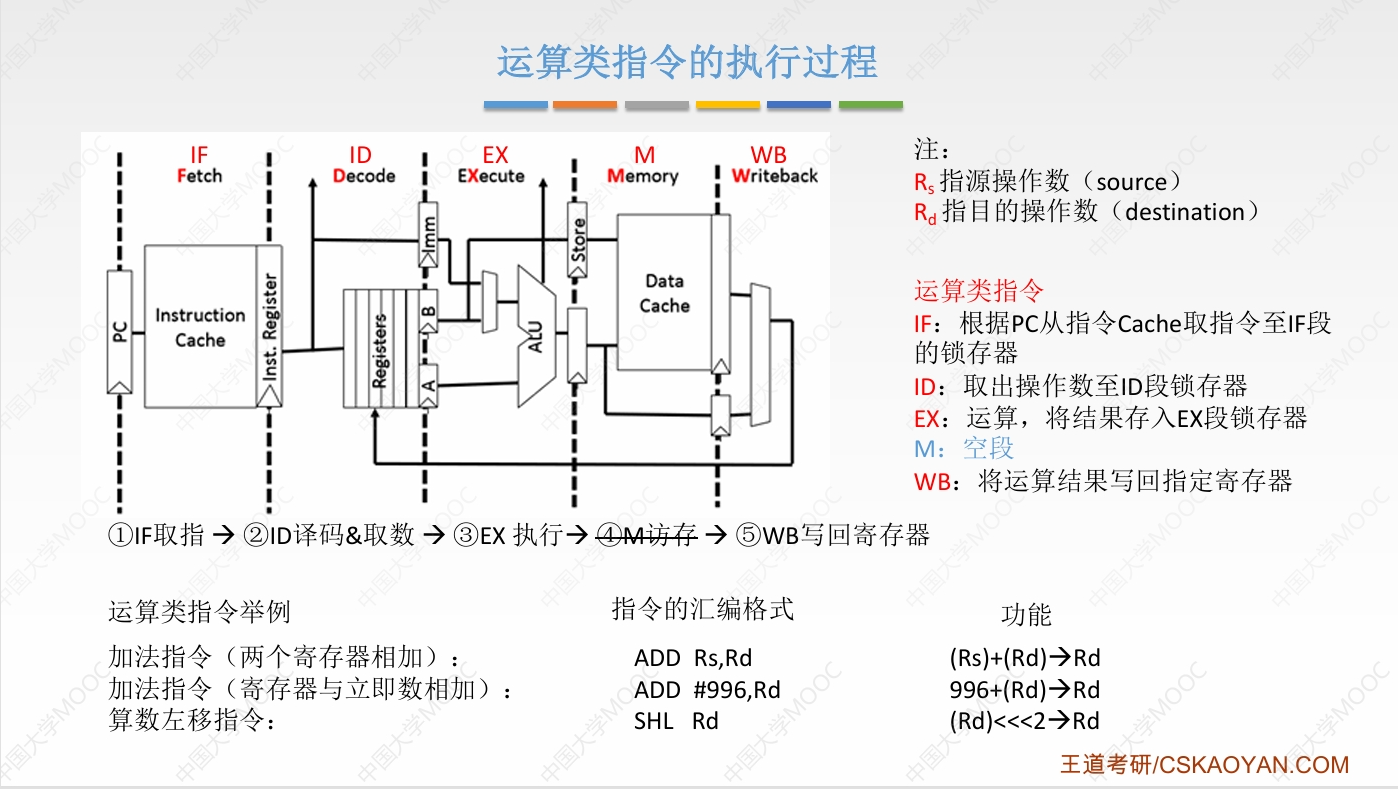

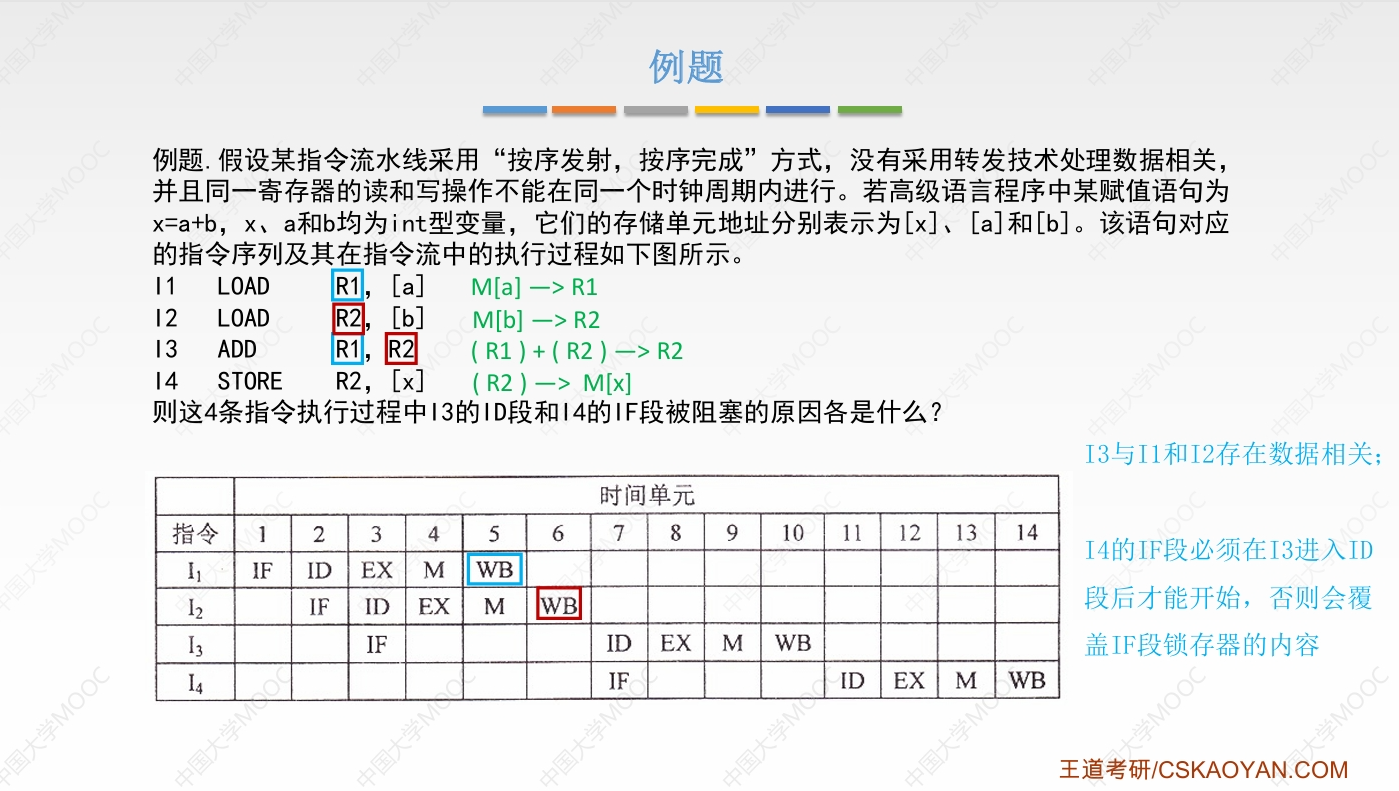

- LOAD指令在WB阶段才会将取出的数写回寄存器,所以I3的ID段被堵塞了

- 只有上一条指令进入ID段后,下一条指令才能开始IF段,否则会覆盖IF段锁存器的内容

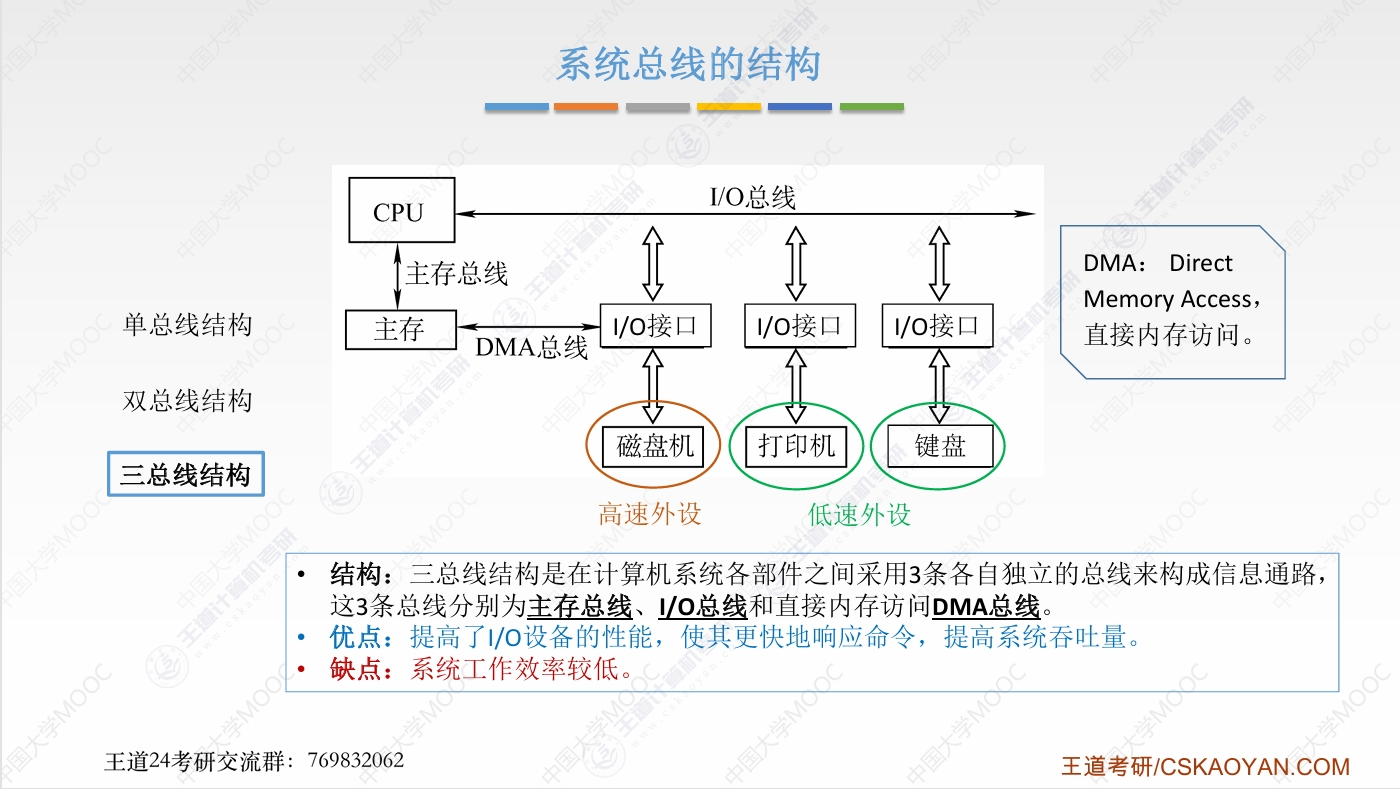

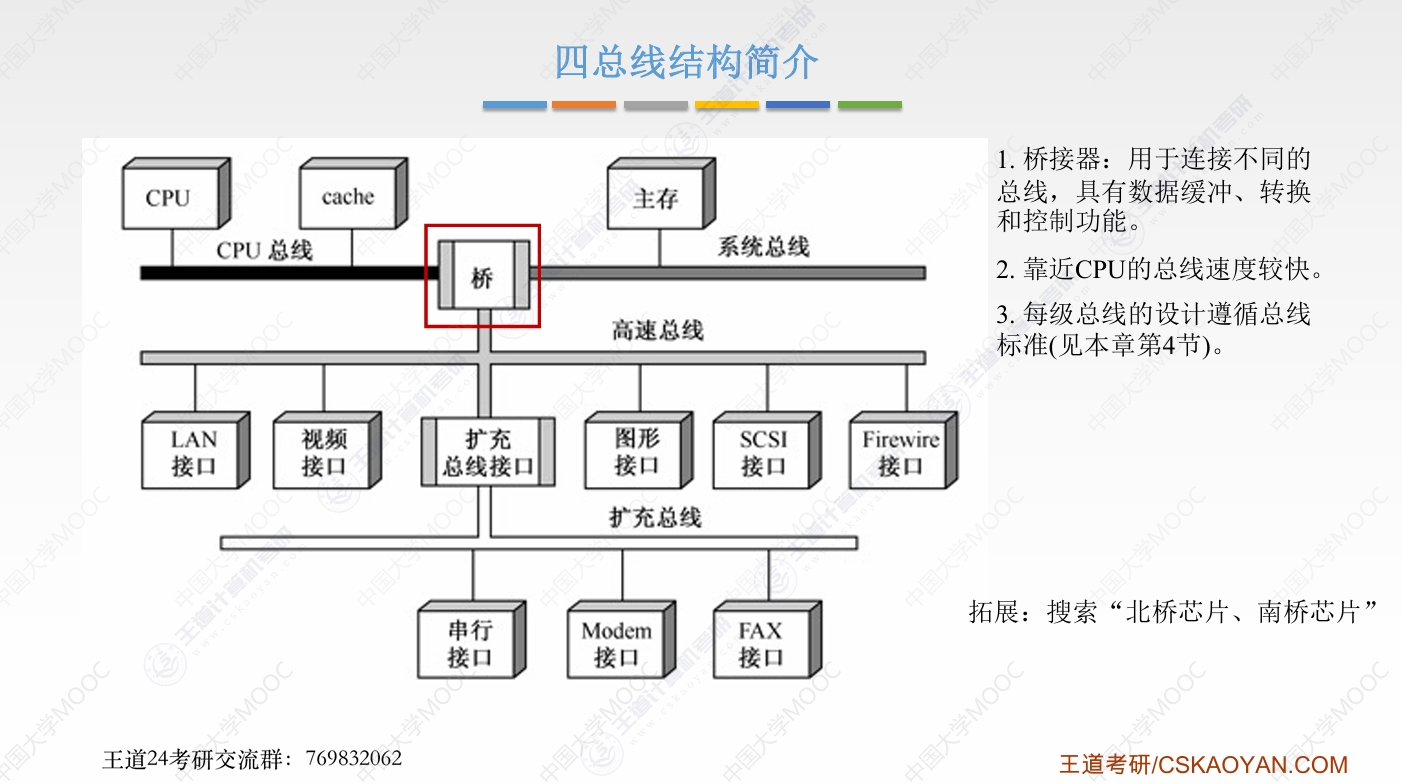

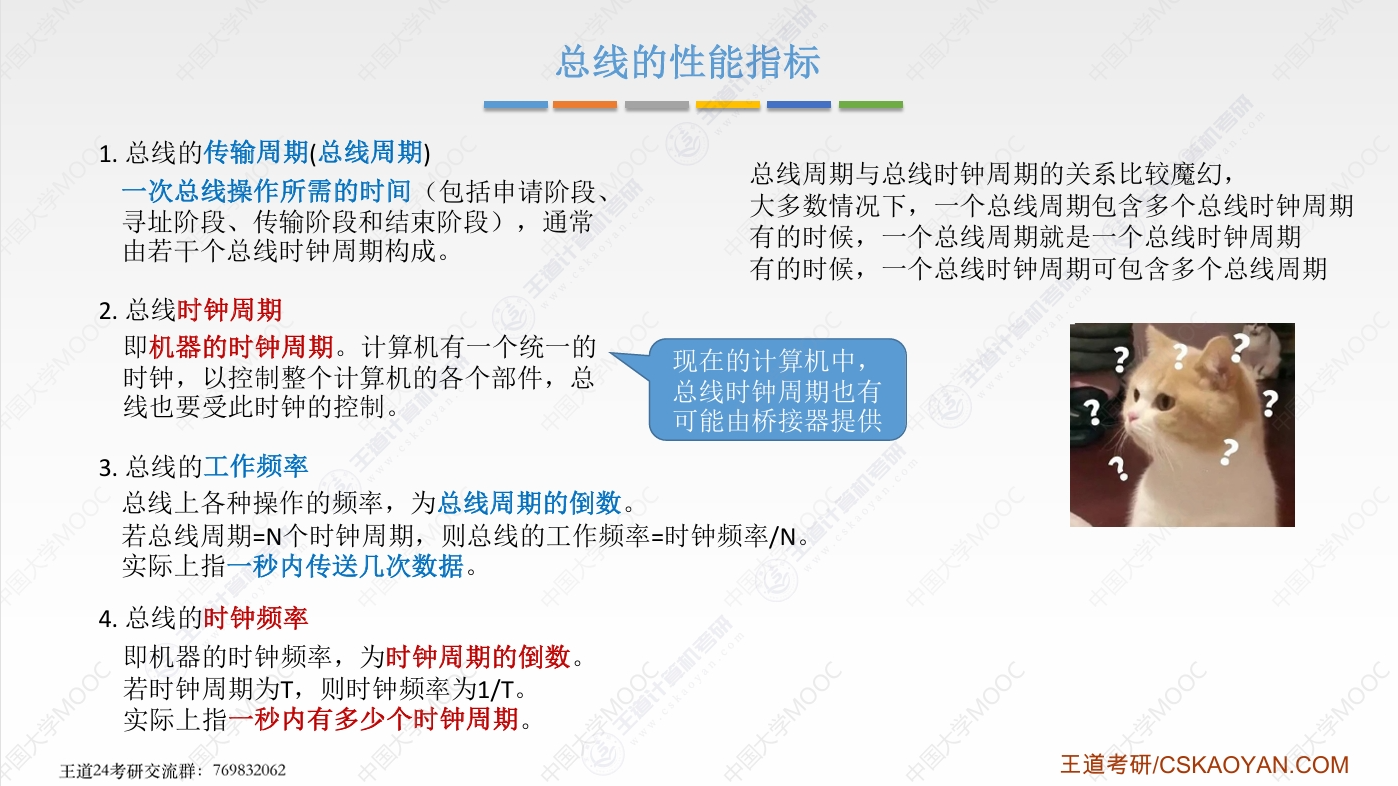

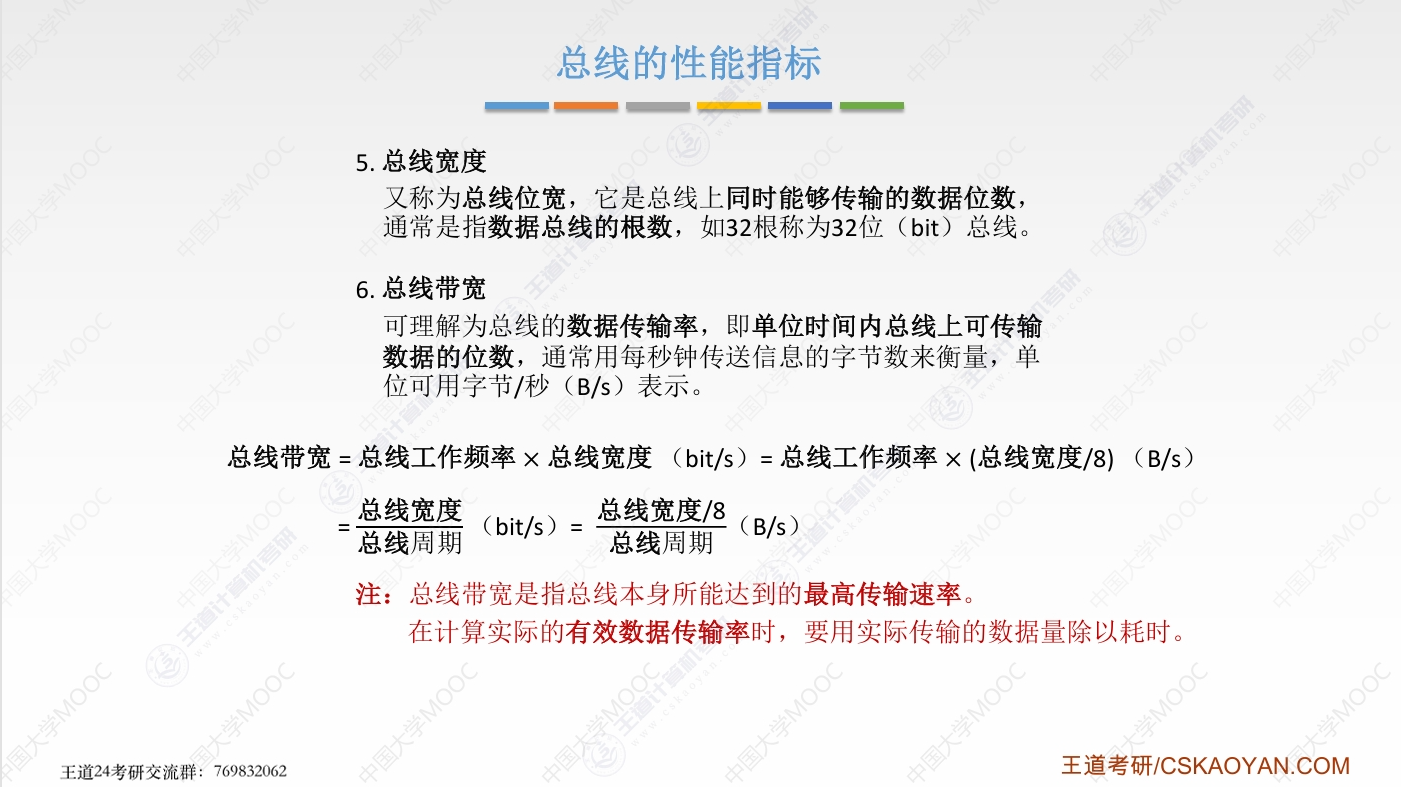

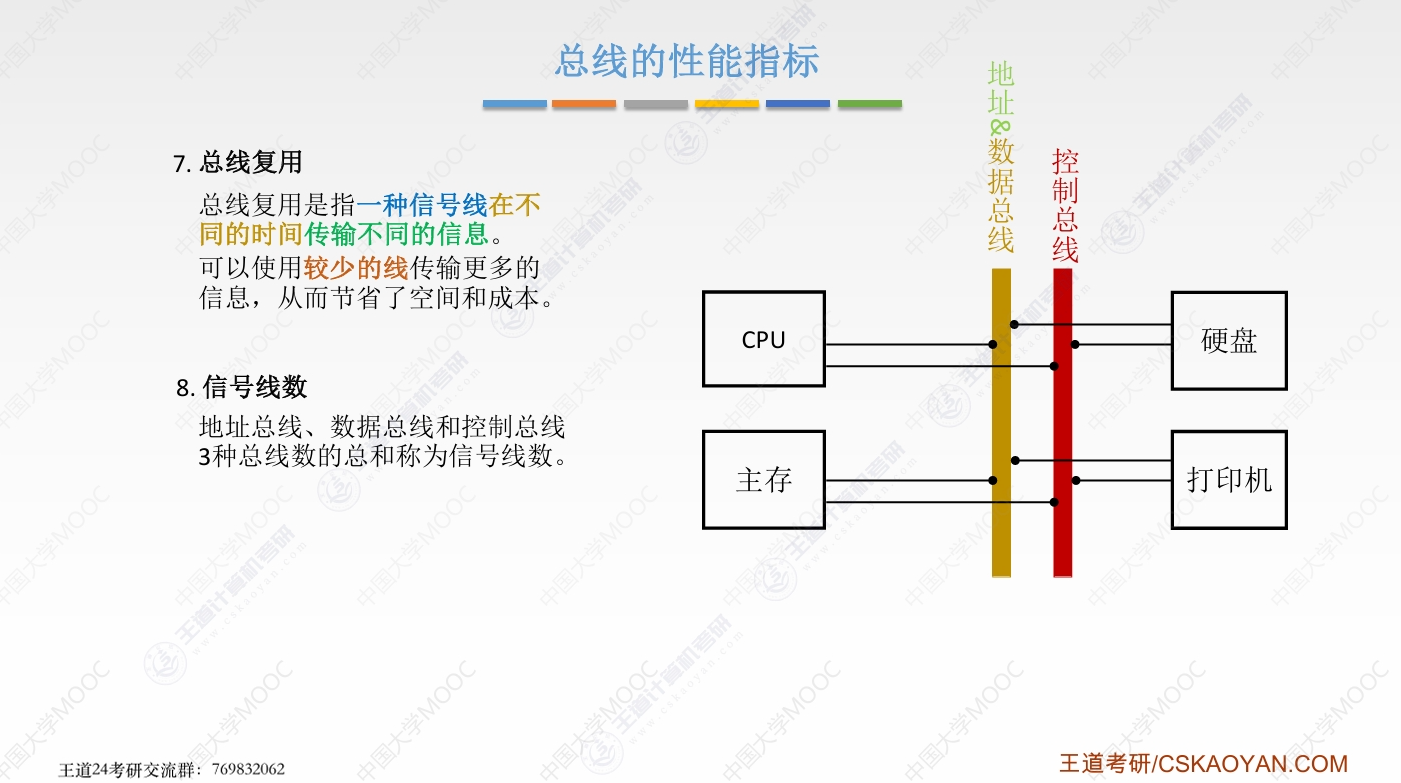

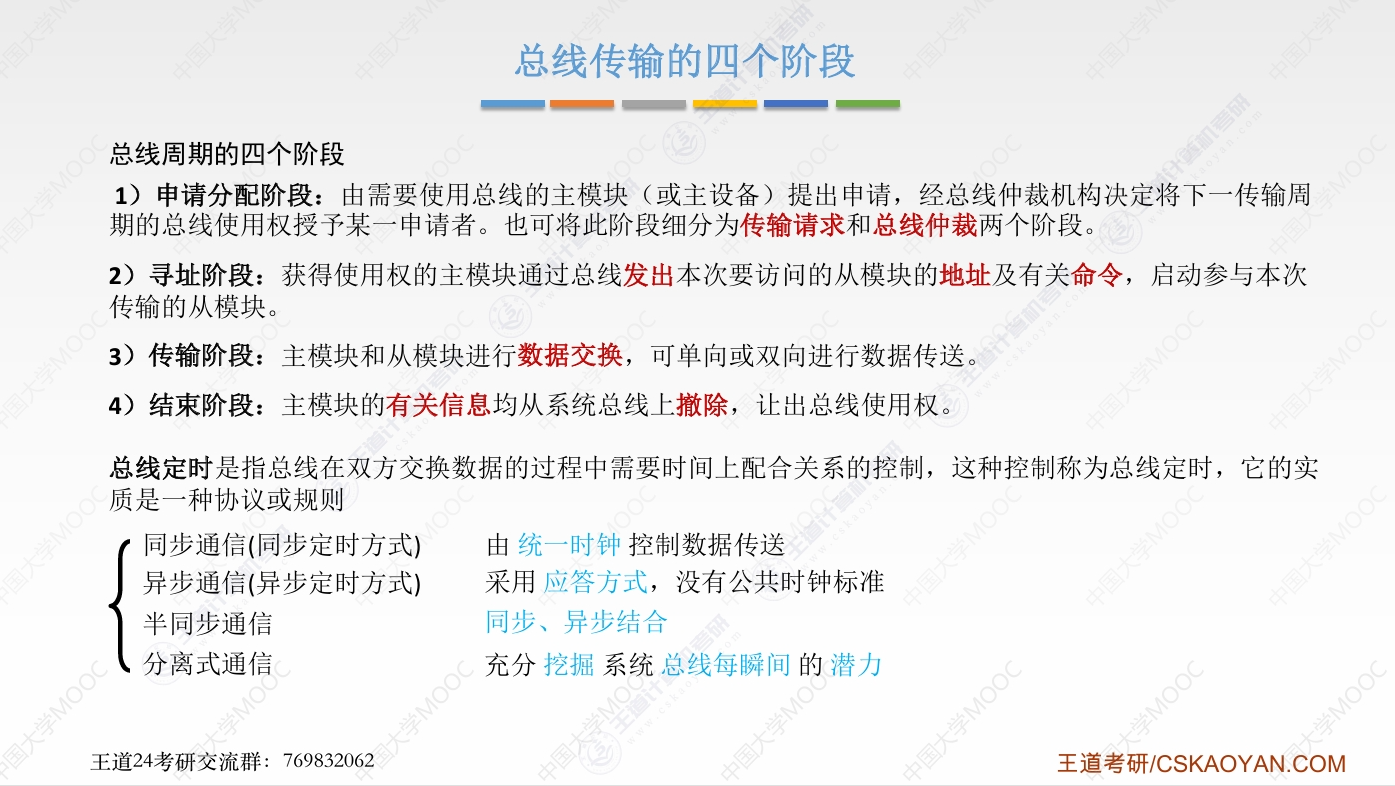

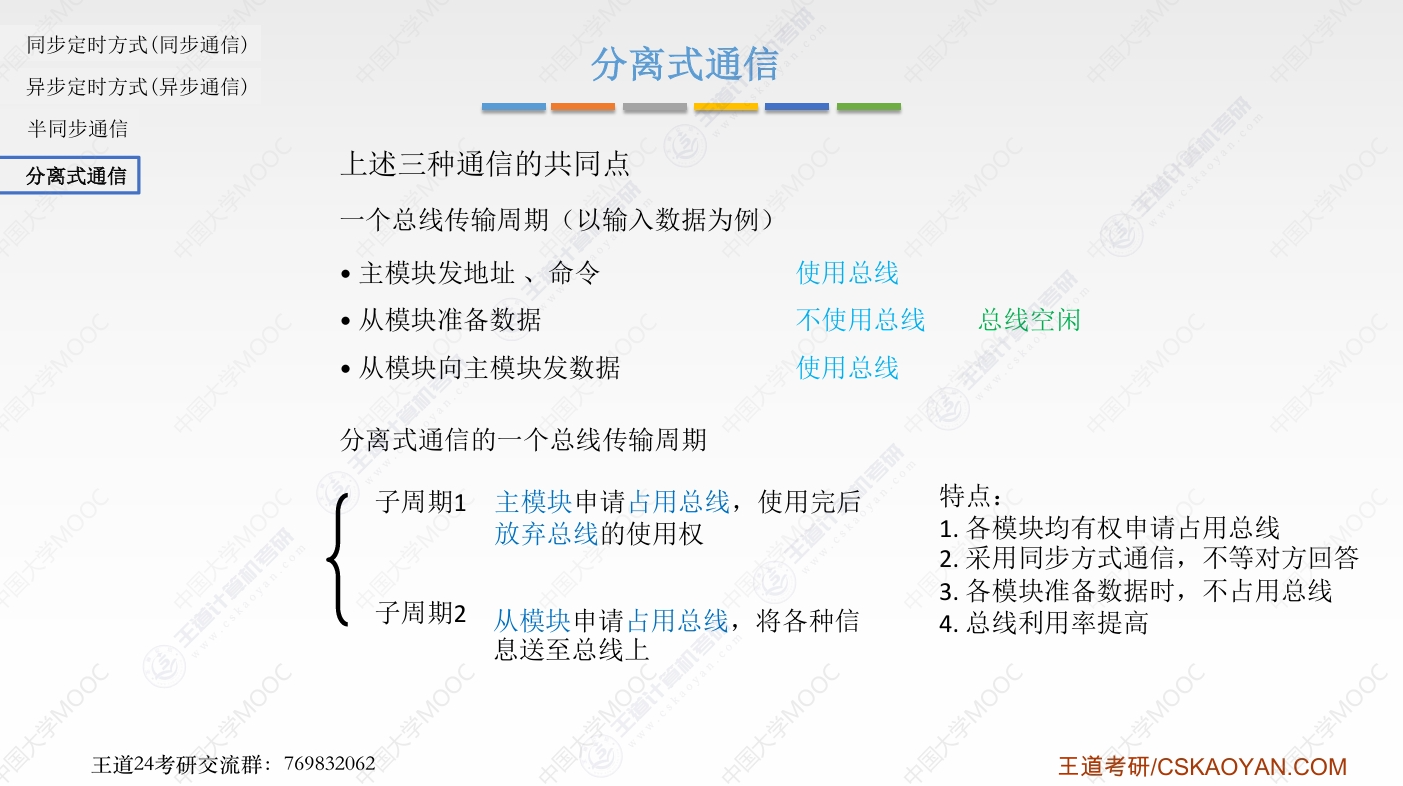

六丶总线

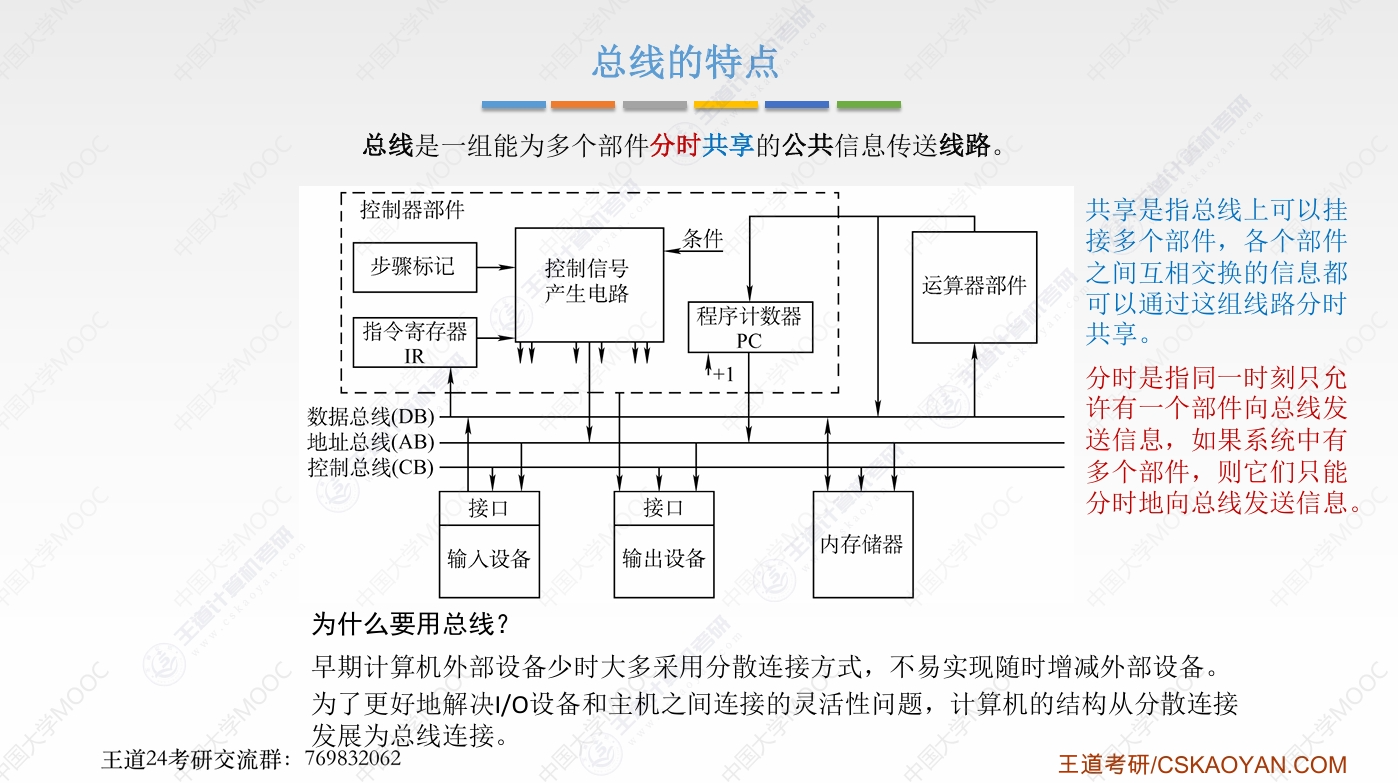

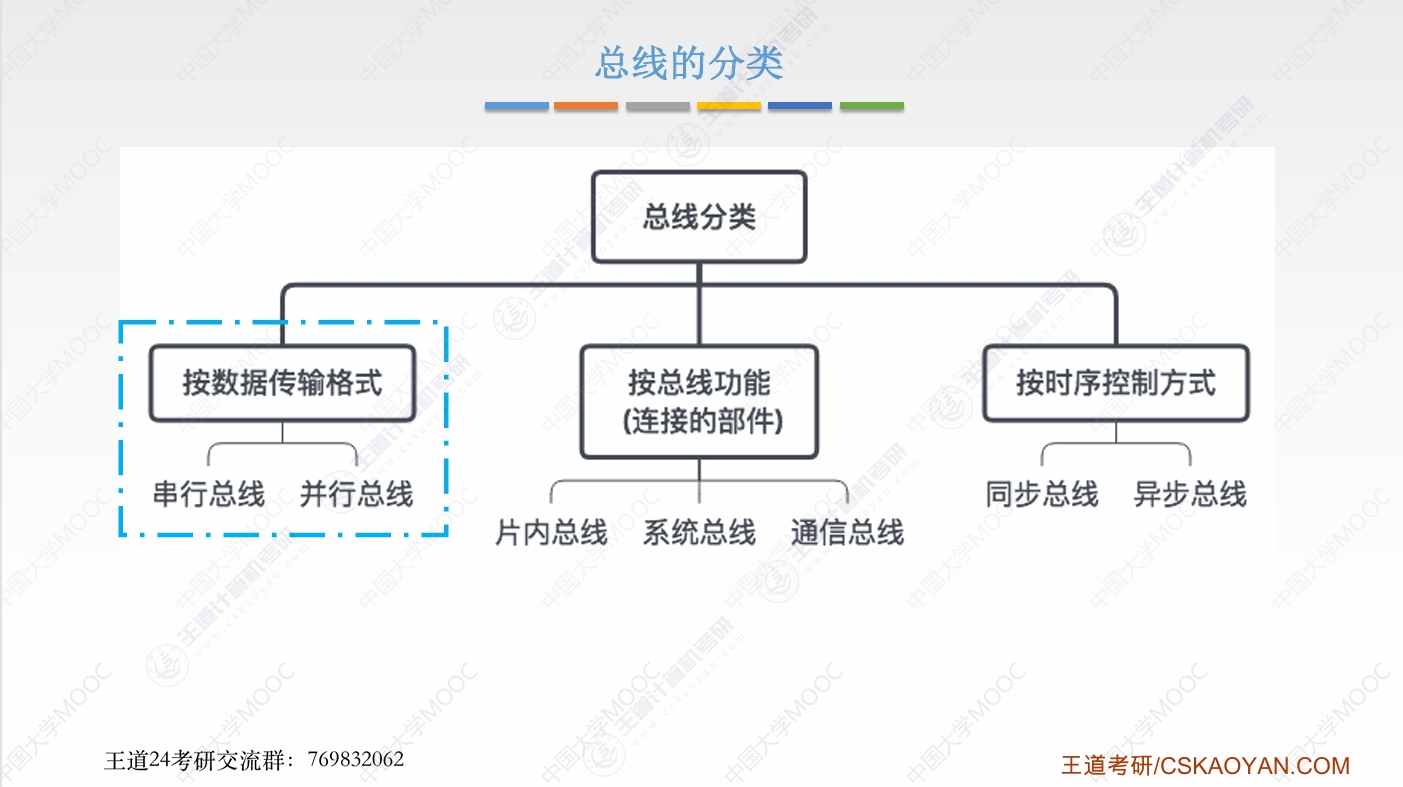

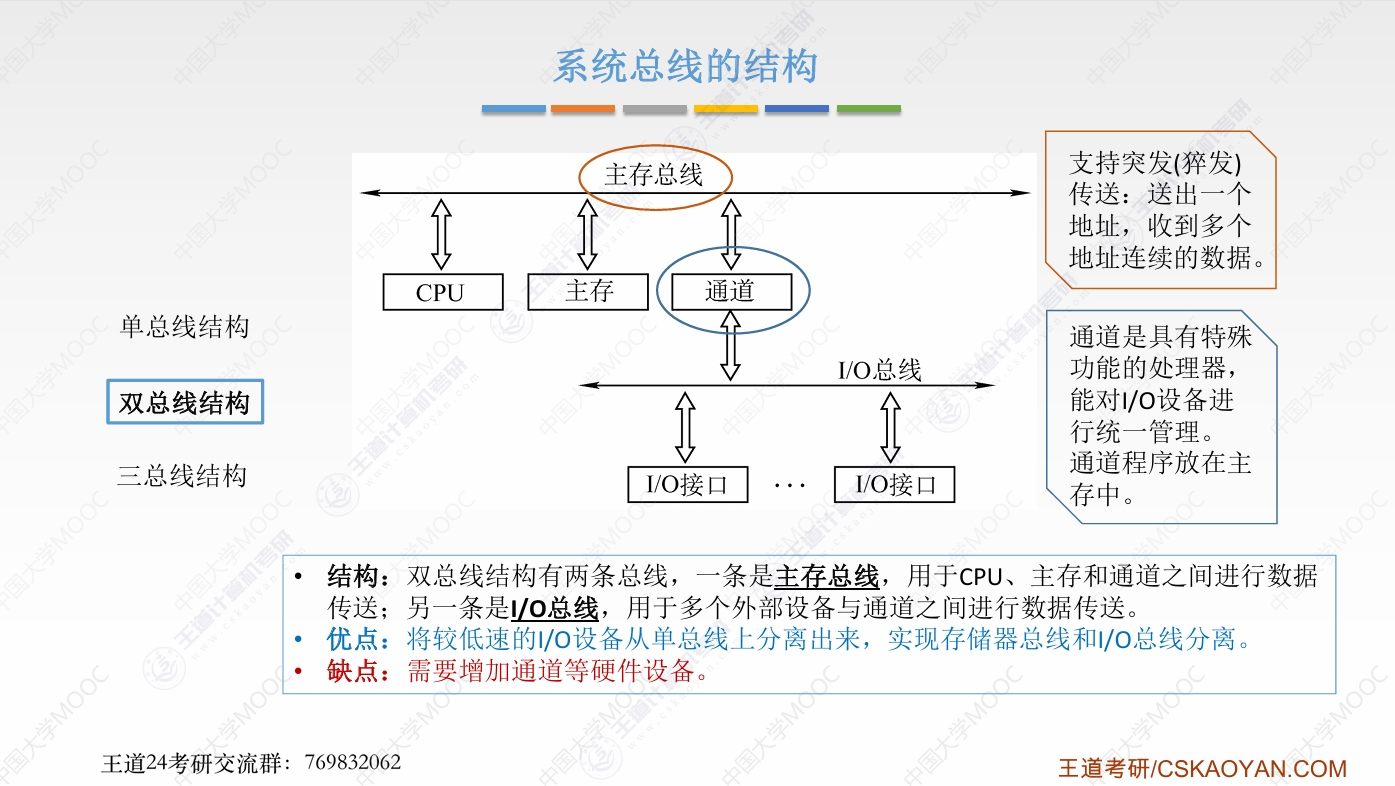

- 总线同一时刻只能有一个部件发送数据,但是可以有多个部件接收数据

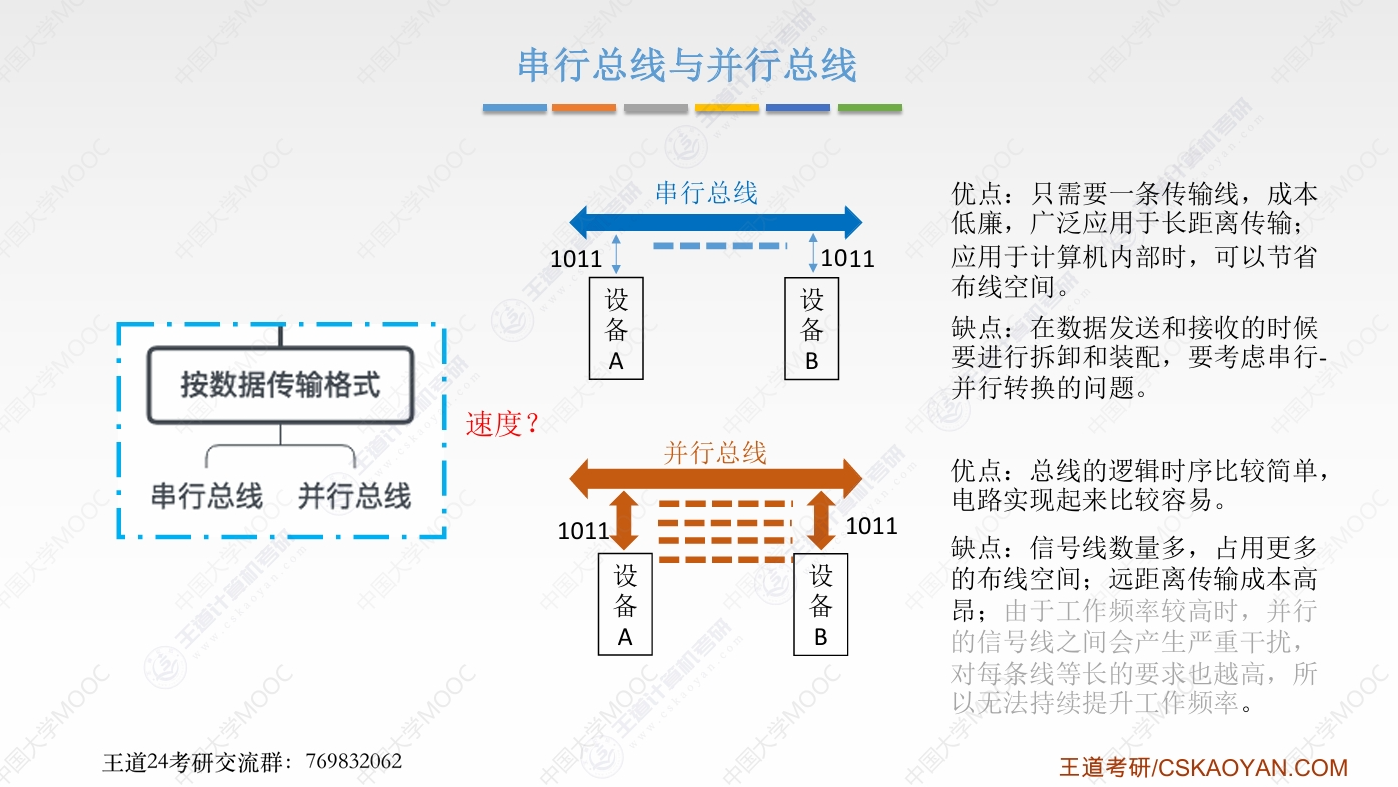

- 传输方向 : 一个部件向另一个部件传(单向/双向)

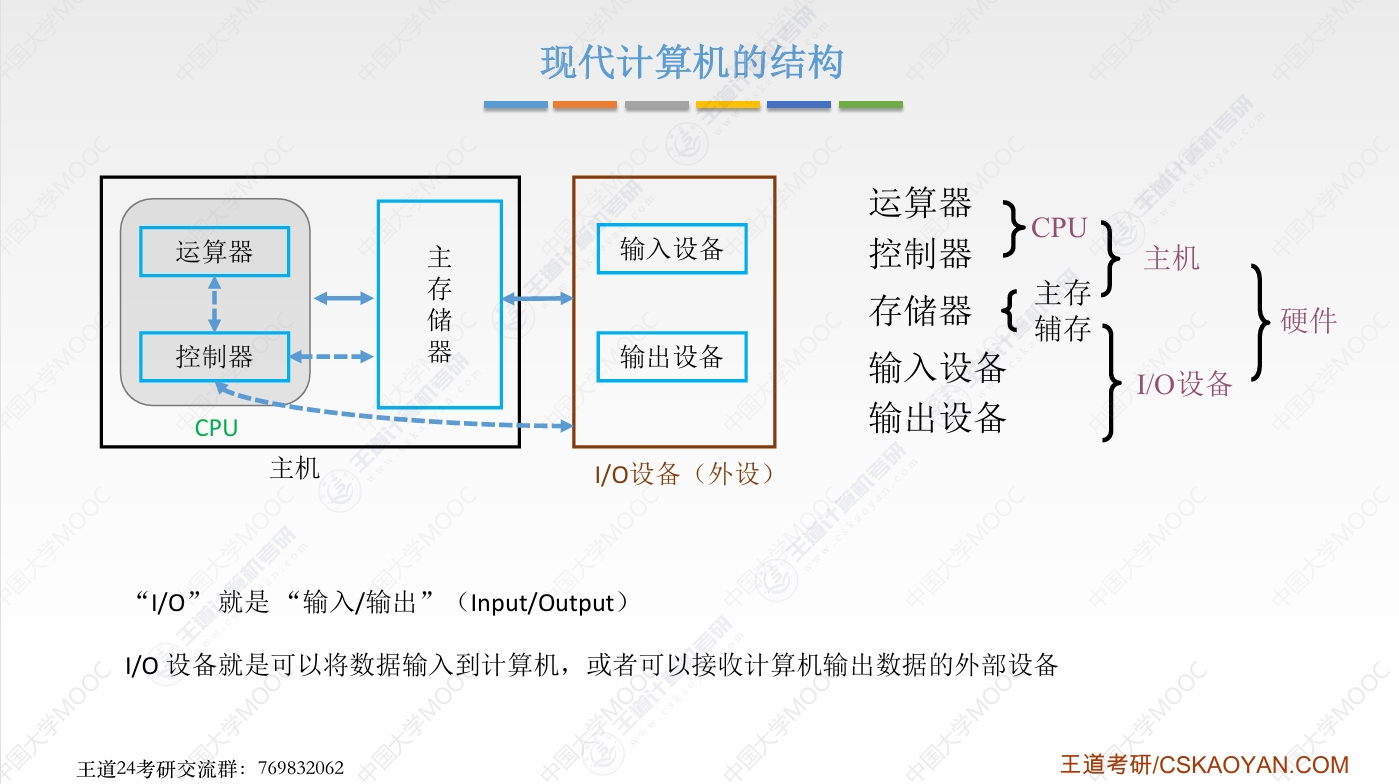

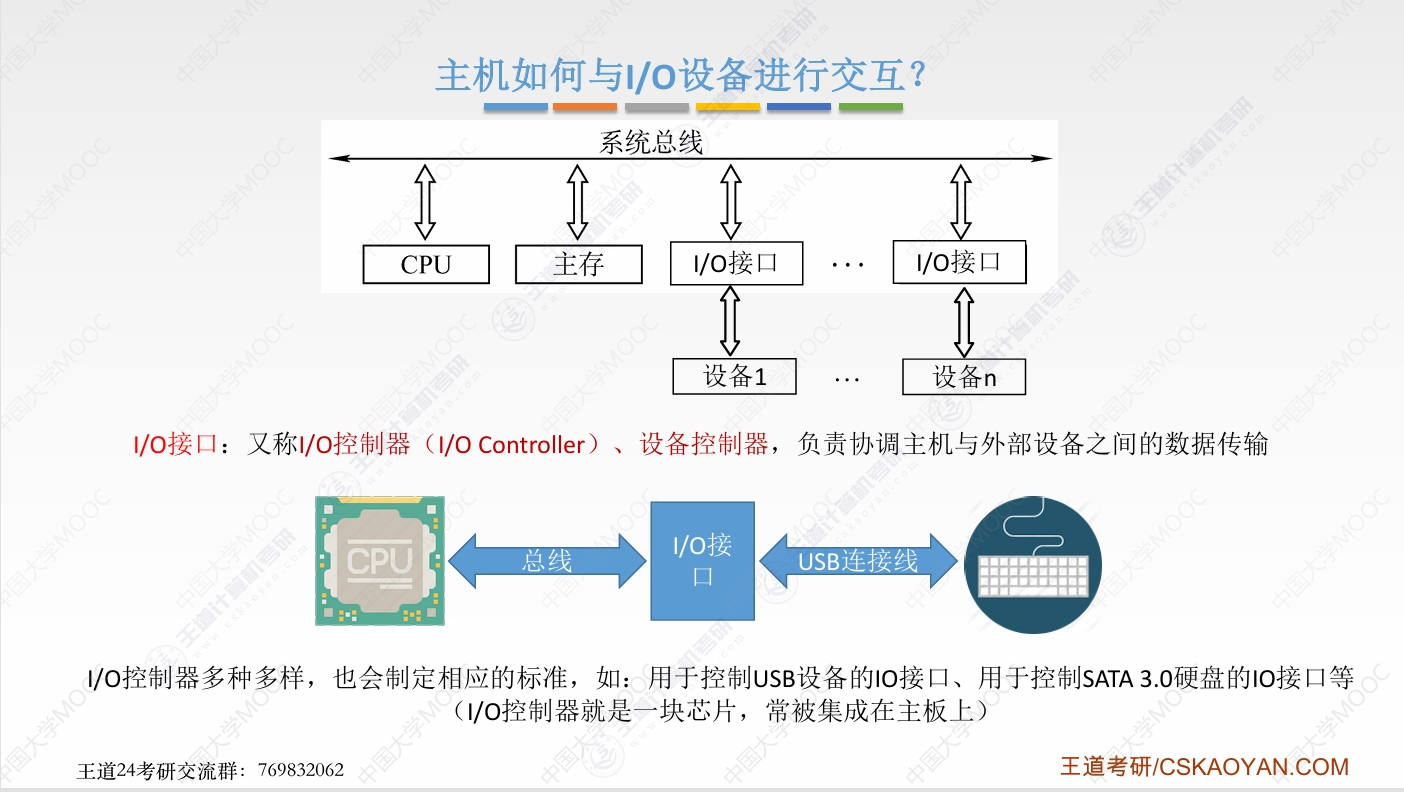

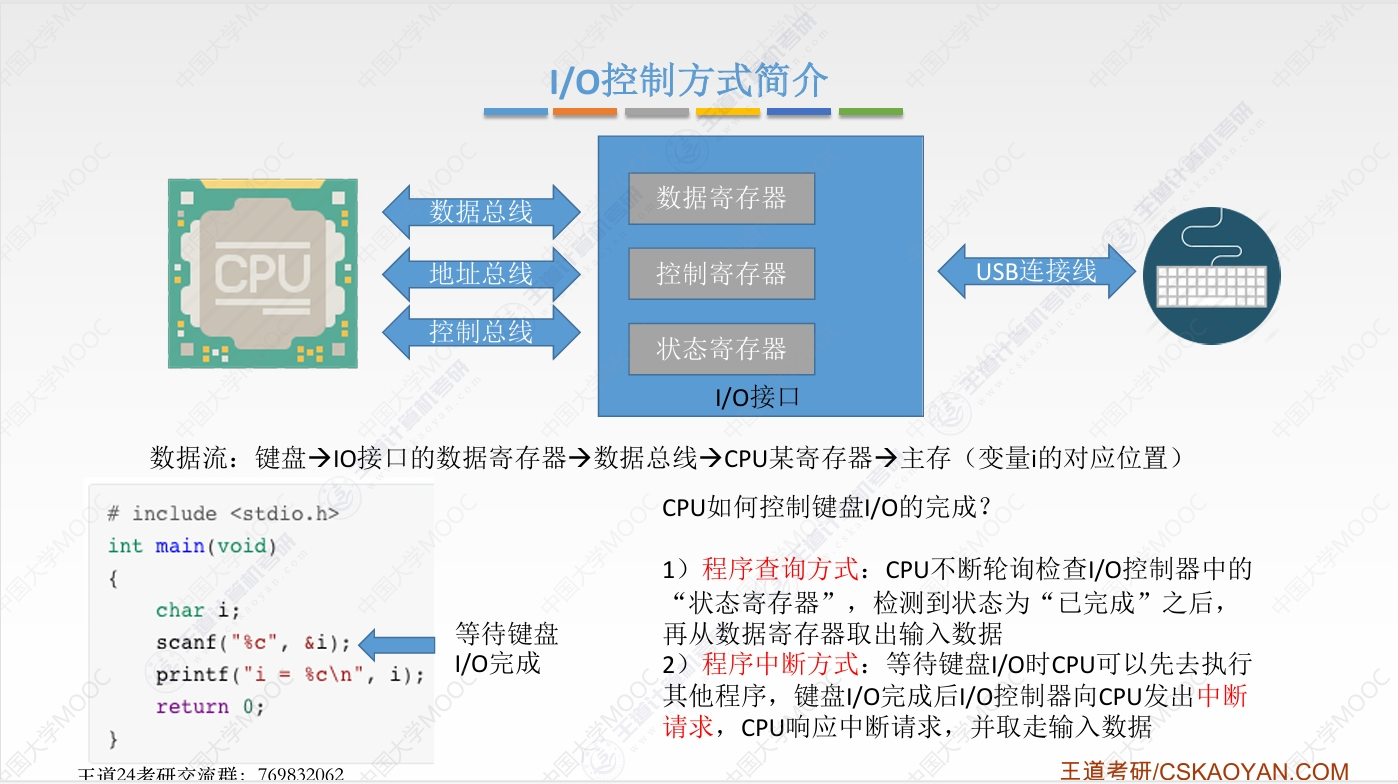

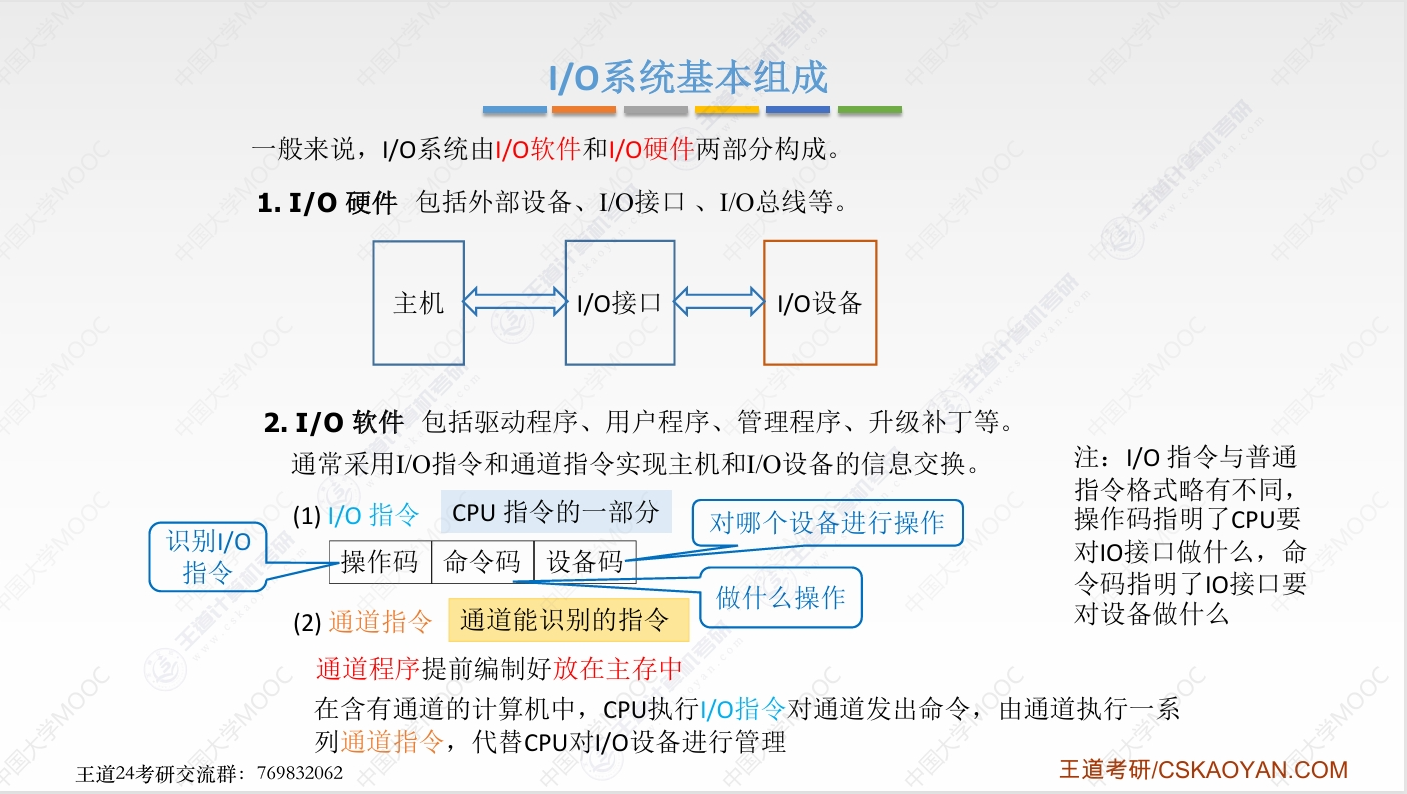

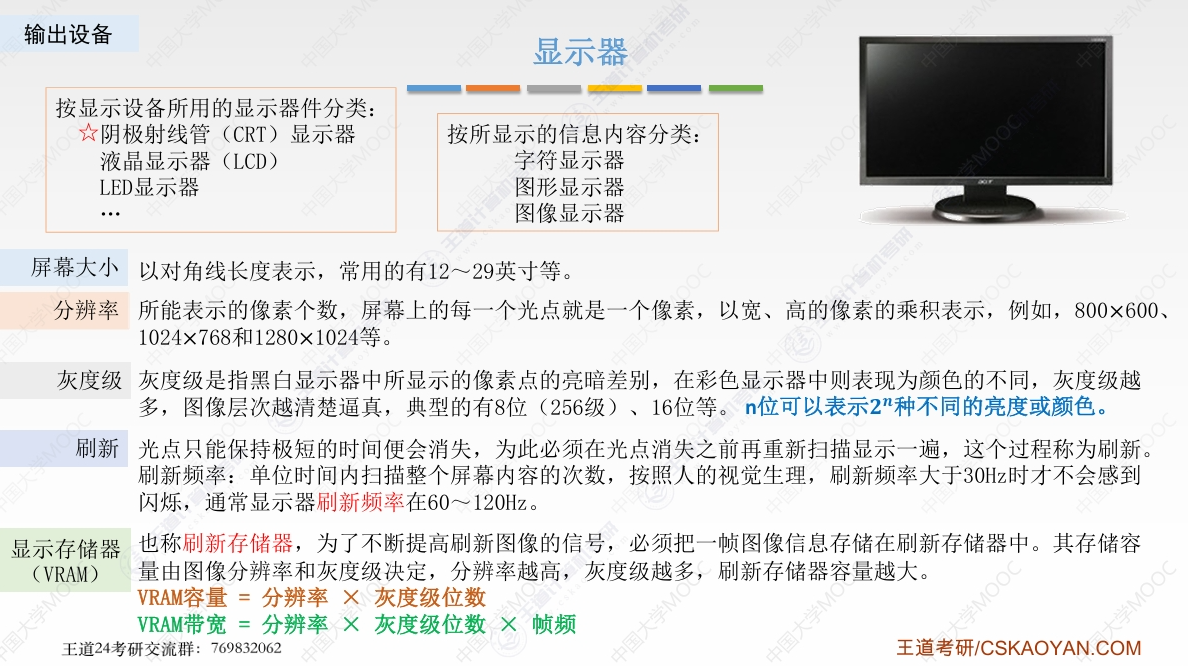

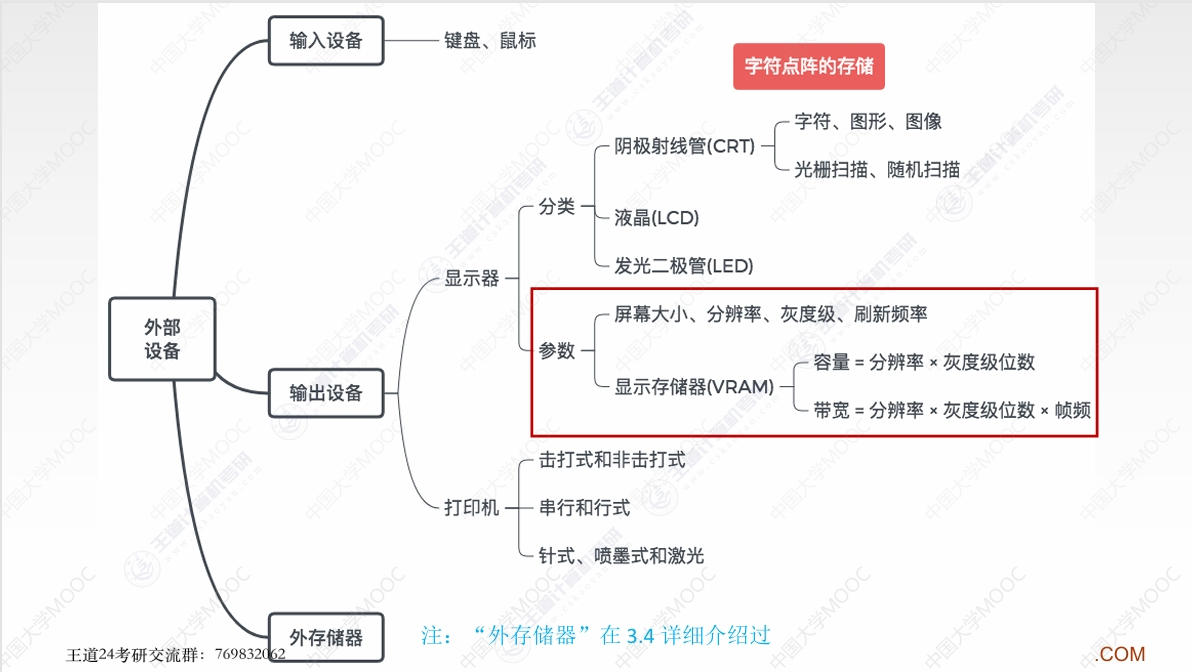

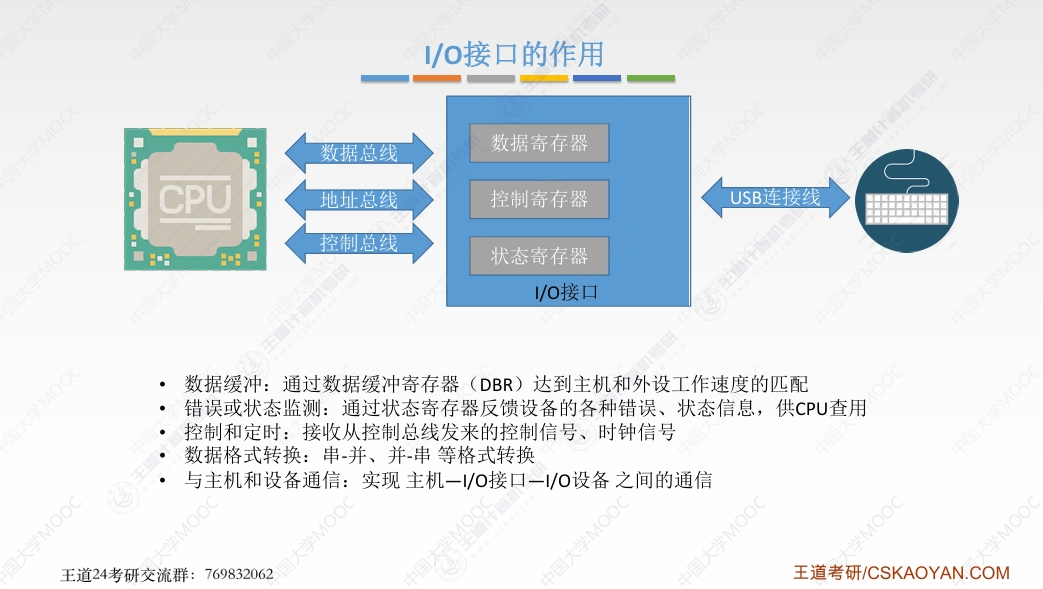

七丶输入输出系统

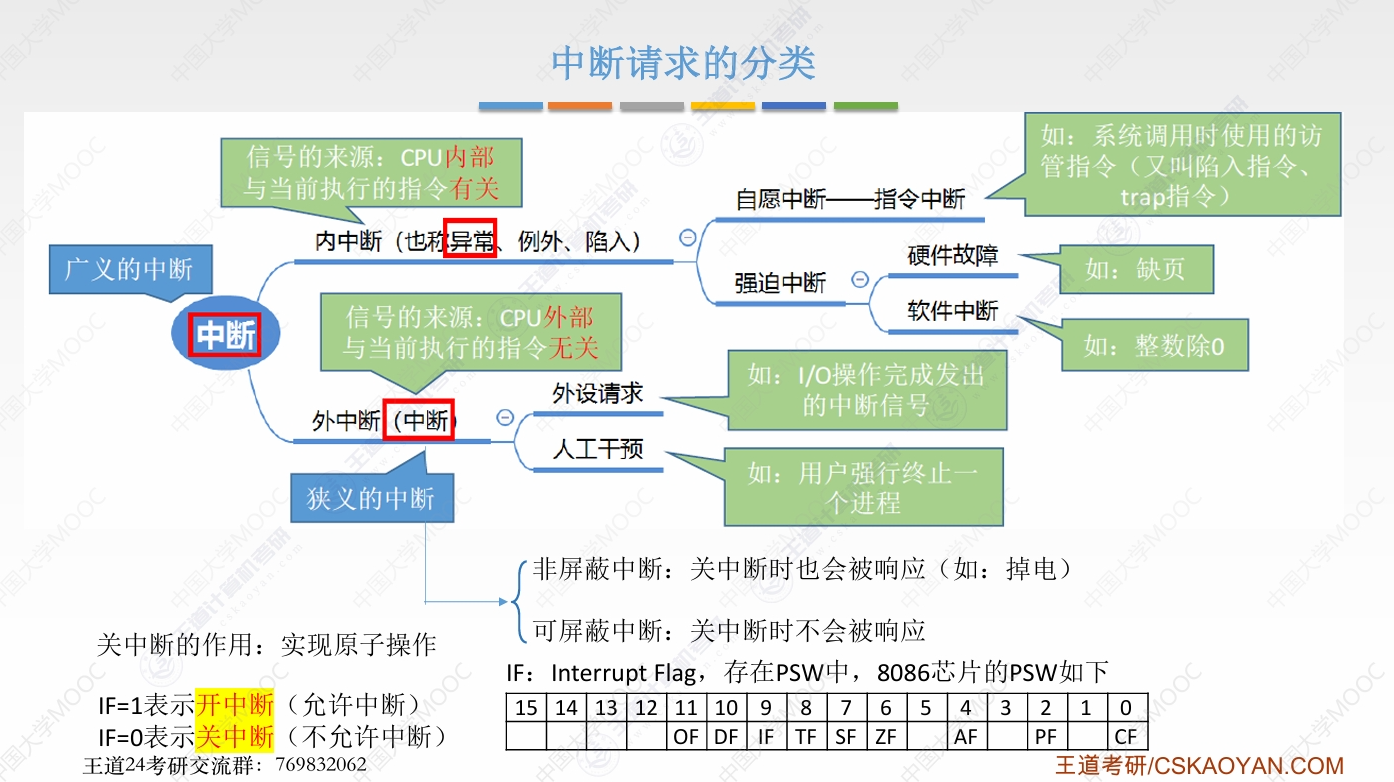

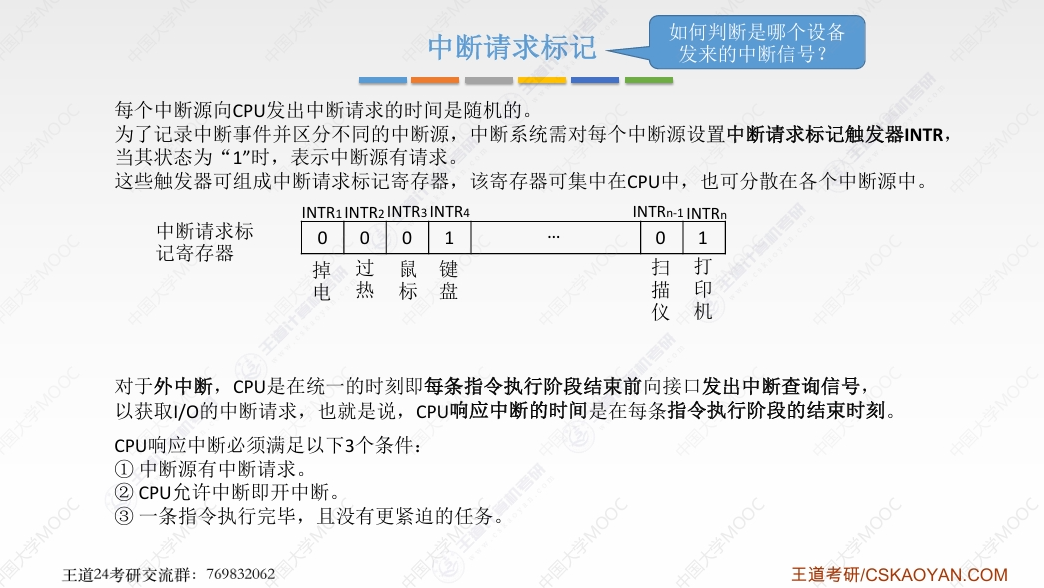

- 原子操作就是不可中断的一个或者一系列操作

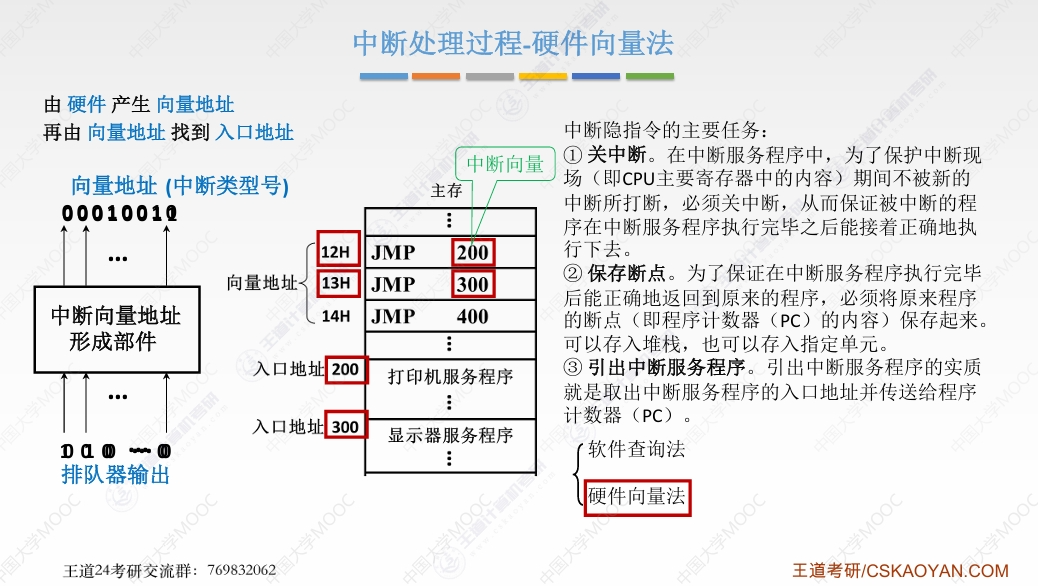

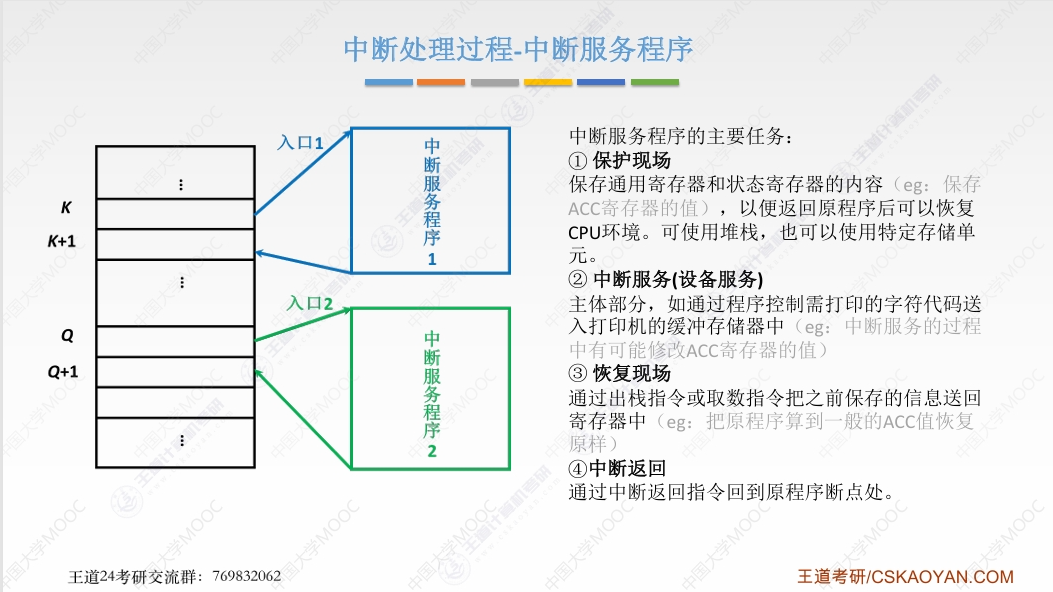

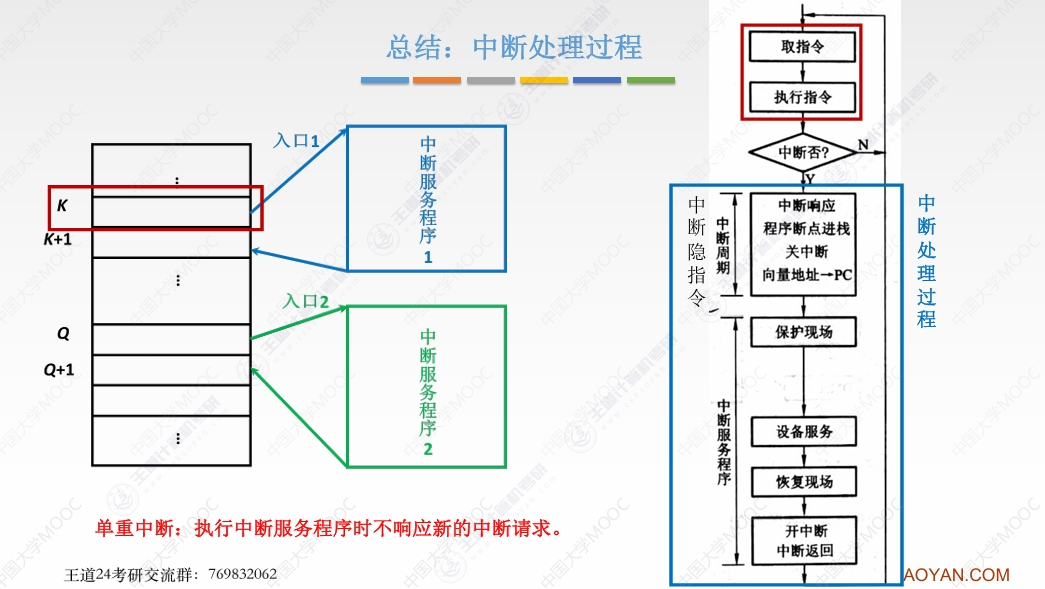

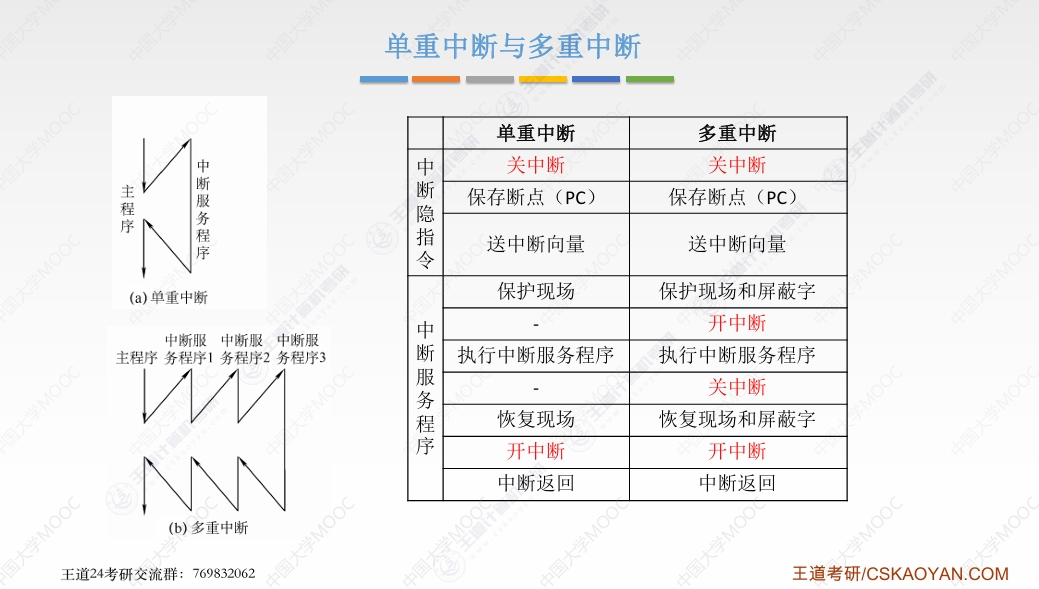

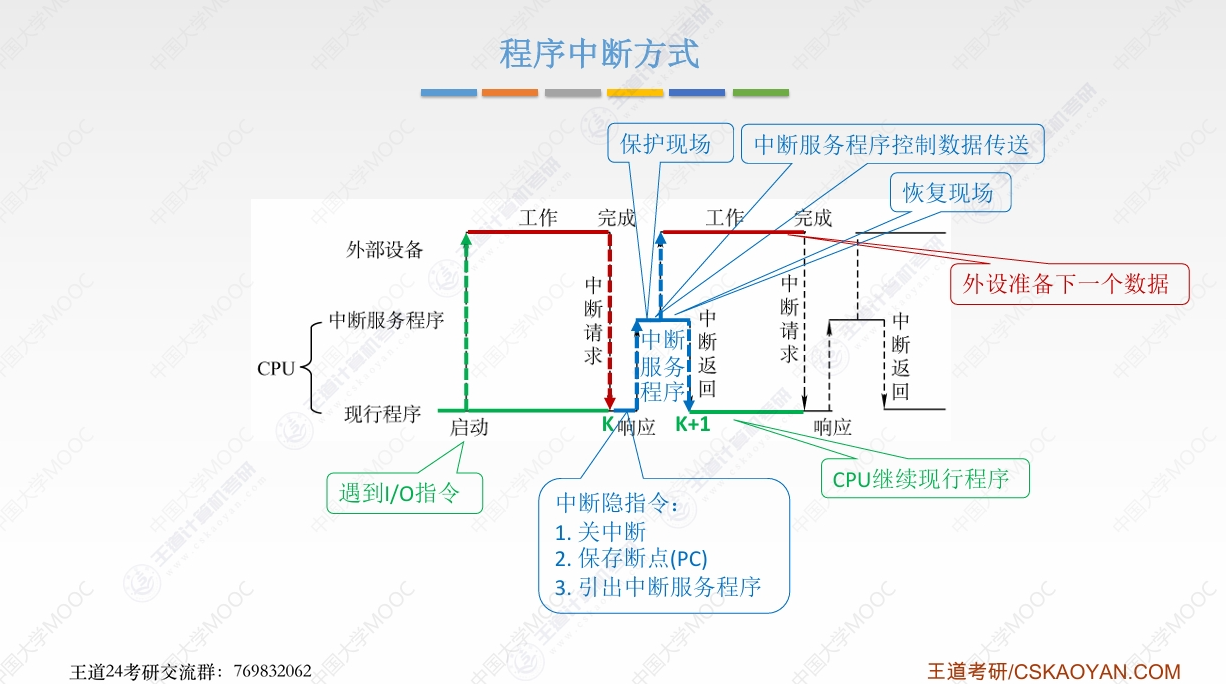

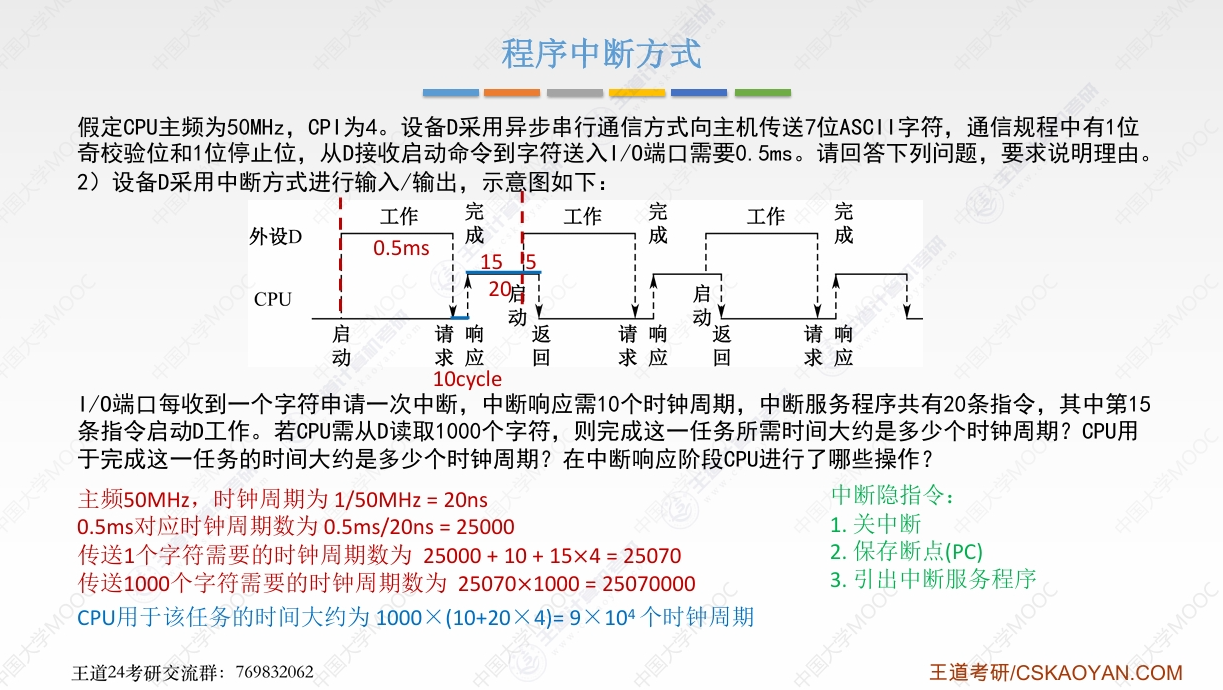

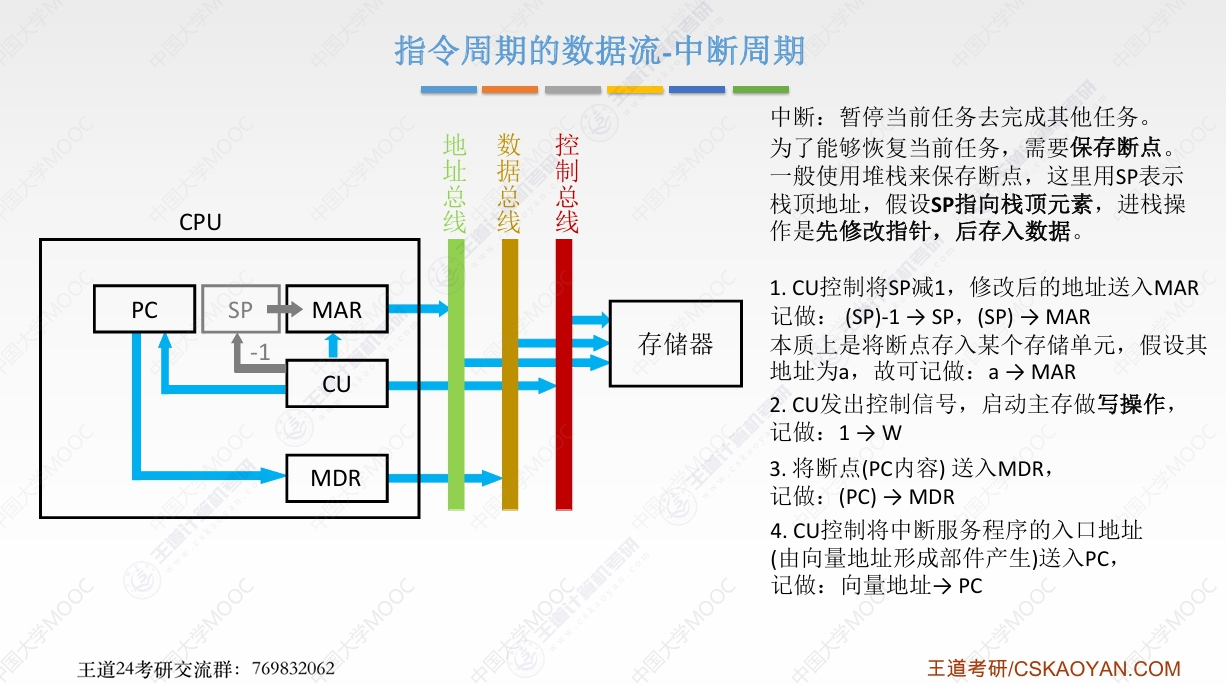

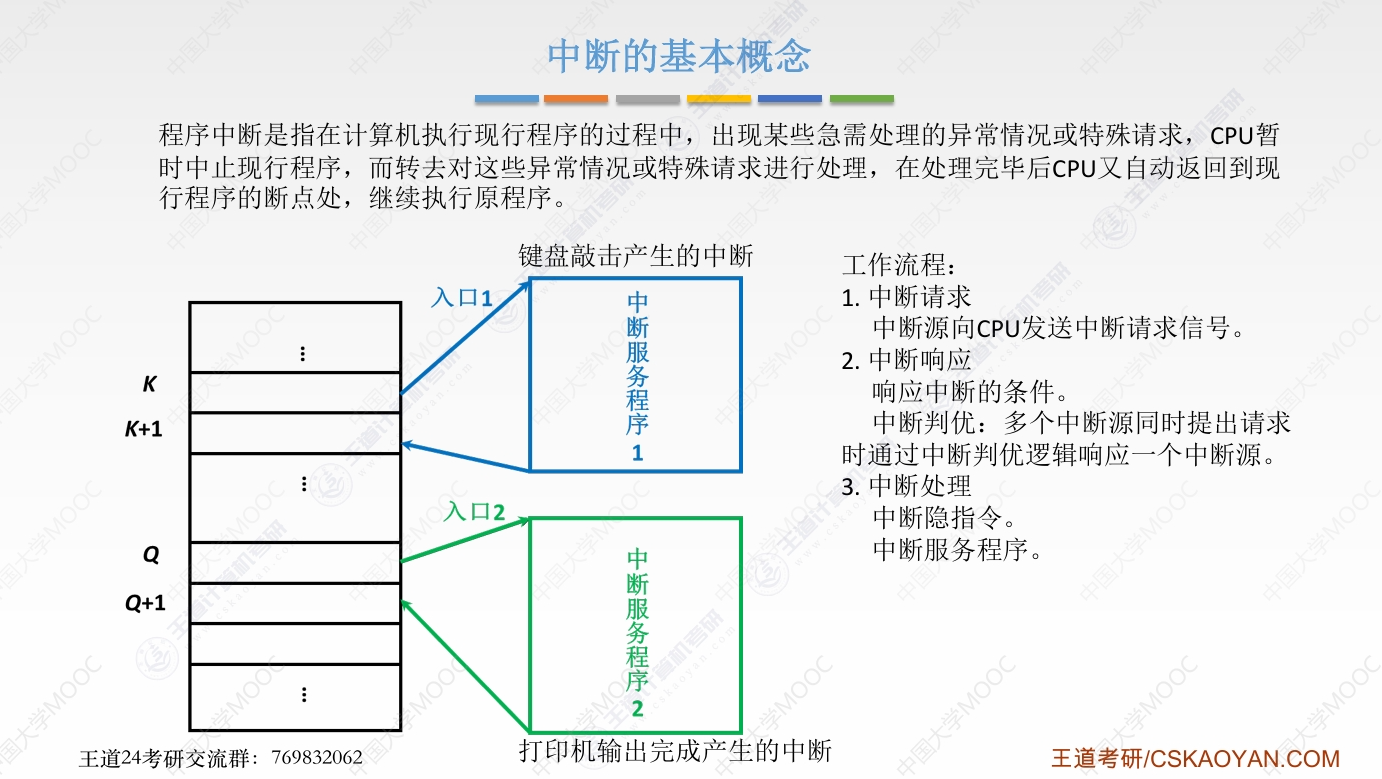

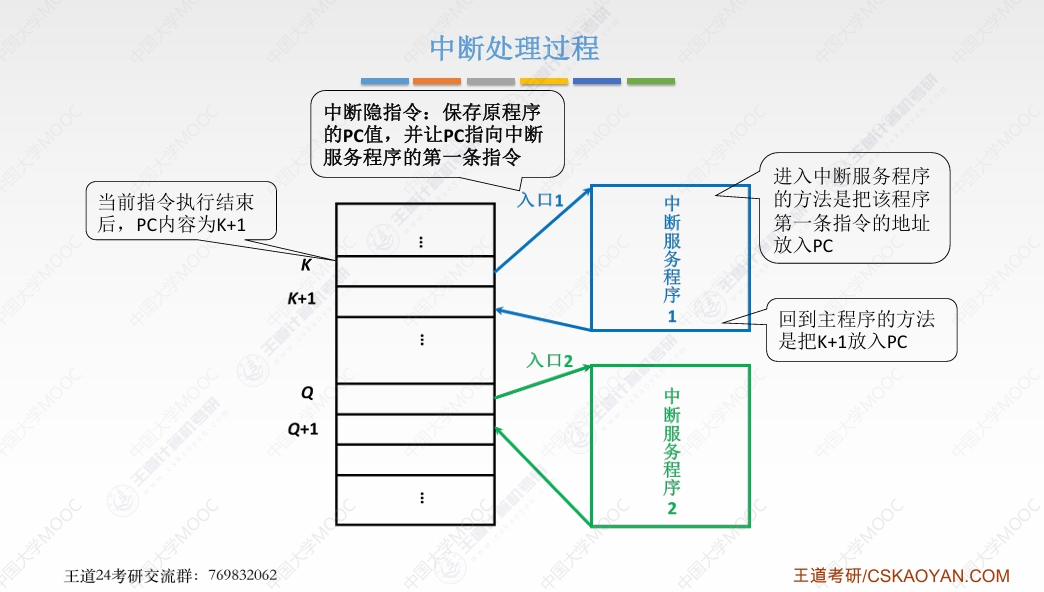

- 中断隐指令并不是一条具体的指令,而是CPU在检测中断请求时自动完成的一系列动作